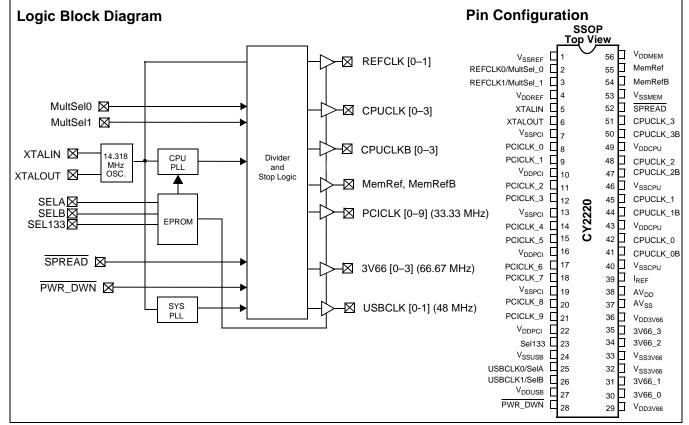

# 133-MHz Spread Spectrum Clock Synthesizer/Driver with Differential CPU Outputs

| Features                                                            | Benefits                                                                                     |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Compliant to Intel® CK00 Clock Synthesizer/Driver<br>Specifications | Supports next generation Pentium® processors using differential clock drivers                |

| Multiple output clocks at different frequencies                     | Motherboard clock generator                                                                  |

| — Four pairs of differential CPU outputs, up to 133 MHz             | <ul> <li>Support Multiple CPUs and a chipset</li> </ul>                                      |

| —Ten synchronous PCI clocks                                         | <ul> <li>Support for PCI slots and chipset</li> </ul>                                        |

| Two Memory Reference clocks, 180 degrees out of phase               | <ul> <li>— Drives up to two Direct Rambus<sup>™</sup> Clock Generators<br/>(DRCG)</li> </ul> |

| — Four AGP and Hub Link clocks at 66 MHz                            | — Supports USB host controller and SuperI/O chip                                             |

| — Two 48-MHz clocks                                                 | — Supports ISA slots and I/O chip                                                            |

| Two reference clocks at 14.318 MHz                                  |                                                                                              |

| Spread Spectrum clocking                                            | Enables reduction of EMI and overall system cost                                             |

| —31 kHz modulation frequency                                        |                                                                                              |

| — Default is -0.6%, which is recommended by Intel                   |                                                                                              |

| Power-down features                                                 | Enables ACPI compliant designs                                                               |

| Three Select inputs                                                 | Supports up to eight CPU clock frequencies                                                   |

| Low-skew and low-jitter outputs                                     | Meets tight system timing requirements at high frequency                                     |

| OE and Test Mode support                                            | Enables ATE and "bed of nails" testing                                                       |

| 56-pin SSOP package                                                 | Widely available, standard package enables lower cost                                        |

Intel and Pentium are registered trademarks of Intel Corporation. Direct Rambus is a trademark of Rambus, Inc.

# **Pin Summary**

| Name                     | Pins                                 | Description                                                                                                                |  |  |

|--------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| V <sub>SSREF</sub>       | 1                                    | 3.3V Reference ground                                                                                                      |  |  |

| V <sub>DDREF</sub>       | 4                                    | 3.3V Reference voltage supply                                                                                              |  |  |

| V <sub>SSPCI</sub>       | 7, 13, 19                            | 3.3V PCI ground                                                                                                            |  |  |

| V <sub>DDPCI</sub>       | 10, 16, 22                           | 3.3V PCI voltage supply                                                                                                    |  |  |

| V <sub>SS3V66</sub>      | 32, 33                               | 3.3V AGP and Hub Link ground                                                                                               |  |  |

| V <sub>DD3V66</sub>      | 29, 36                               | 3.3V AGP and Hub Link voltage supply                                                                                       |  |  |

| V <sub>SSUSB</sub>       | 24                                   | 3.3V USB ground                                                                                                            |  |  |

| V <sub>DDUSB</sub>       | 27                                   | 3.3V USB voltage supply                                                                                                    |  |  |

| V <sub>SSCPU</sub>       | 40, 46                               | 3.3V CPU ground                                                                                                            |  |  |

| V <sub>DDCPU</sub>       | 43, 49                               | 3.3V CPU voltage supply                                                                                                    |  |  |

| V <sub>SSMEM</sub>       | 53                                   | 3.3V Memory ground                                                                                                         |  |  |

| V <sub>DDMEM</sub>       | 56                                   | 3.3V Memory voltage supply                                                                                                 |  |  |

| AV <sub>SS</sub>         | 37                                   | Analog ground for PLL and Core                                                                                             |  |  |

| $AV_{DD}$                | 38                                   | Analog voltage supply to PLL and Core                                                                                      |  |  |

| I <sub>REF</sub>         | 39                                   | Reference current for external biasing                                                                                     |  |  |

| XTALIN <sup>[1]</sup>    | 5                                    | Reference crystal input                                                                                                    |  |  |

| XTALOUT <sup>[1]</sup>   | 6                                    | Reference crystal feedback                                                                                                 |  |  |

| CPUCLK [0-3]             | 42, 45, 48, 51                       | CPU clock outputs                                                                                                          |  |  |

| CPUCLK [0-3]B            | 41, 44, 47, 50                       | Inverse CPU clock outputs                                                                                                  |  |  |

| PCICLK [0-9]             | 8, 9, 11, 12, 14, 15, 17, 18, 20, 21 | PCI clock outputs, synchronously running at 33.33 MHz                                                                      |  |  |

| MemRef                   | 55                                   | MemRef clock output, drives memory clock generator                                                                         |  |  |

| MemRefB                  | 54                                   | MemRefB clock output 180 degrees out of phase with MemRef                                                                  |  |  |

| 3V66_[0-3]               | 30, 31, 34, 35                       | AGP and Hub Link clock outputs, running at 66 MHz                                                                          |  |  |

| USBCLK [0-1]/Sel[A-B]    | 25, 26                               | Sel [A–B] inputs are sensed then internally latched on power-up before the pins are used for 48-MHz USB clock outputs      |  |  |

| REFCLK[0-1]/MultSel[0-1] | 2, 3                                 | MultSel[0–1] inputs are sensed then internally latched on power-up before the pins are Reference clock outputs, 14.318 MHz |  |  |

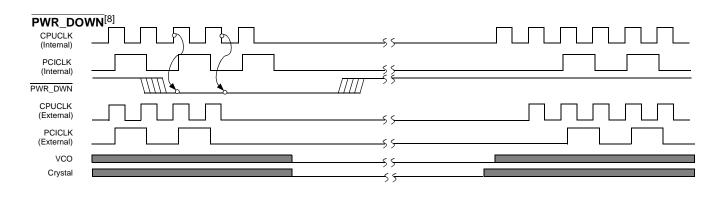

| PWR_DWN                  | 28                                   | Active LOW input, powers down part when asserted                                                                           |  |  |

| SPREAD <sup>[2]</sup>    | 52                                   | Active LOW input, enables spread spectrum when asserted                                                                    |  |  |

| SEL133                   | 23                                   | CPU frequency select input (See Function Table)                                                                            |  |  |

#### Notes:

Document #: 38-07206 Rev. \*A

<sup>1.</sup> For best accuracy, use a parallel-resonant crystal,  $C_{LOAD}$  = 18 pF. For crystals with different  $C_{LOAD}$ , please refer to the application note, "Crystal Oscillator Topics."

2. Input is static HIGH or LOW. Frequency of toggling cannot exceed 30 MHz.

#### Function Table<sup>[3]</sup>

| SEL133 | SELA | SELB | CPUCLK<br>(MHz) | MemRef<br>(MHz) | 3V66CLK<br>(MHz) | PCICLK<br>(MHz) | USBCLK<br>(MHz) | REFCLK<br>(MHz) |

|--------|------|------|-----------------|-----------------|------------------|-----------------|-----------------|-----------------|

| 0      | 0    | 0    | 100             | 50              | 66               | 33              | 48              | 14.318          |

| 0      | 0    | 1    | N/A             | N/A             | N/A              | N/A             | N/A             | N/A             |

| 0      | 1    | 0    | N/A             | N/A             | N/A              | N/A             | N/A             | N/A             |

| 0      | 1    | 1    | Hi-Z            | Hi-Z            | Hi-Z             | Hi-Z            | Hi-Z            | Hi-Z            |

| 1      | 0    | 0    | 133             | 66              | 66               | 33              | 48              | 14.318          |

| 1      | 0    | 1    | N/A             | N/A             | N/A              | N/A             | N/A             | N/A             |

| 1      | 1    | 0    | N/A             | N/A             | N/A              | N/A             | N/A             | N/A             |

| 1      | 1    | 1    | TCLK/2          | TCLK/4          | TCLK/4           | TCLK/8          | TCLK/2          | TCLK            |

# **Actual Clock Frequency Values**

|                 | Target             | CY2220-                   | ·1    | CY2220-2               |       |  |

|-----------------|--------------------|---------------------------|-------|------------------------|-------|--|

| Clock<br>Output | Frequency<br>(MHz) | Actual Frequency<br>(MHz) | PPM   | Actual Frequency (MHz) | PPM   |  |

| CPUCLK          | 100                | 99.126                    | -8741 | 100.227                | +2270 |  |

| CPUCLK          | 133                | 132.769                   | -1740 | 133.269                | +2022 |  |

| USBCLK          | 48                 | 48.008                    | 167   | 48.008                 | 167   |  |

# **Swing Select Functions**

| MultSel0 | MultSel1 Board Target |                                     | Reference R, I <sub>REF</sub> =  | Output<br>Current        | V <sub>OH</sub> @ Z,<br>Iref = 2.32 mA |

|----------|-----------------------|-------------------------------------|----------------------------------|--------------------------|----------------------------------------|

| 0        | 0                     | 60Ω                                 | Rr = 475 ± 1%,<br>Iref = 2.32 mA | I <sub>OH</sub> = 5*Iref | 0.71 @ 60                              |

| 0        | 0                     | 50Ω                                 | Rr = 475 ± 1%,<br>Iref = 2.32 mA | I <sub>OH</sub> = 5*Iref | 0.59 @ 50                              |

| 0        | 1                     | $Rr = 475 \pm 1\%$ , Iref = 2.32 mA |                                  | I <sub>OH</sub> = 6*Iref | 0.85 @ 60                              |

| 0        | 1                     | 50Ω                                 | Rr = 475 ± 1%,<br>Iref = 2.32 mA | I <sub>OH</sub> = 6*Iref | 0.71 @ 50                              |

| 1        | 0                     | 60Ω                                 | Rr = 475 ± 1%,<br>Iref = 2.32 mA | I <sub>OH</sub> = 4*Iref | 0.56 @ 60                              |

| 1        | 0                     | 50Ω                                 | Rr = 475 ± 1%,<br>Iref = 2.32 mA | I <sub>OH</sub> = 4*Iref | 0.47 @ 50                              |

| 1        | 1                     | 60Ω                                 | Rr = 475 ± 1%,<br>Iref = 2.32 mA | I <sub>OH</sub> = 7*Iref | 0.99 @ 60                              |

| 1        | 1                     | 50Ω                                 | Rr = 475 ± 1%,<br>Iref = 2.32 mA | I <sub>OH</sub> = 7*Iref | 0.82 @ 50                              |

# **Clock Driver Impedances**

|                 |                       |             |                                                           | Impedance        |                                                           |

|-----------------|-----------------------|-------------|-----------------------------------------------------------|------------------|-----------------------------------------------------------|

| Buffer Name     | V <sub>DD</sub> Range | Buffer Type | $\begin{array}{c} \textbf{Minimum} \\ \Omega \end{array}$ | Typical $\Omega$ | $\begin{array}{c} \mathbf{Maximum} \\ \Omega \end{array}$ |

| CPUCLK, CPUCLKB |                       | Type X1     |                                                           |                  |                                                           |

| USB, REF        | 3.135-3.465           | Type 3      | 20                                                        | 40               | 60                                                        |

| PCI, 3V66       | 3.135–3.465           | Type 5      | 12                                                        | 30               | 55                                                        |

| MemRef, MemRefB | 3.135-3.465           | Type 5      | 12                                                        | 30               | 55                                                        |

Note:

Document #: 38-07206 Rev. \*A

<sup>3.</sup> TCLK is a test clock driven in on the XTALIN input in test mode.

# **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

Supply Voltage.....-0.5 to +7.0V Input Voltage.....-0.5V to  $V_{\rm DD}$  + 0.5

| Storage Temperature (Non-Condensing)65°C to +150°C          |

|-------------------------------------------------------------|

| Junction Temperature+150°C                                  |

| Package Power Dissipation1W                                 |

| Static Discharge Voltage (per JEDEC EIA/JESD22-A114-A)2000V |

#### **Operating Conditions** Over which Electrical Parameters are Guaranteed

| Parameter                                                                                                                                             | Description                                                                                    | Min.   | Max.     | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--------|----------|------|

| V <sub>DDREF</sub> , V <sub>DDPCI</sub> , AV <sub>DD</sub> ,<br>V <sub>DD3V66</sub> , V <sub>DDUSB</sub> , V <sub>DDCPU</sub> ,<br>V <sub>DDMEM</sub> | 3.3V Supply Voltages                                                                           | 3.135  | 3.465    | V    |

| T <sub>A</sub>                                                                                                                                        | Operating Temperature, Ambient                                                                 | 0      | 70       | °C   |

| C <sub>in</sub>                                                                                                                                       | Input Pin Capacitance Nominal Value                                                            | 18 pF  | 18 pF    | pF   |

| C <sub>XTAL</sub>                                                                                                                                     | XTAL Pin Capacitance                                                                           |        | 22.5     | pF   |

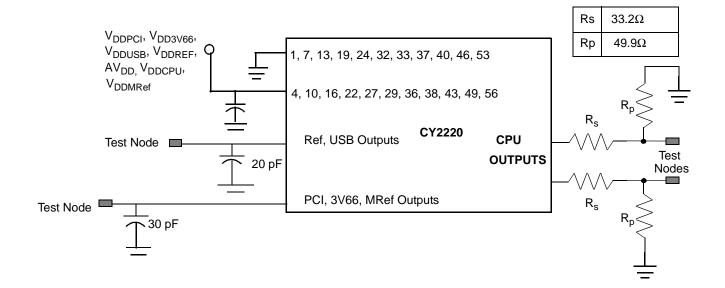

| CL                                                                                                                                                    | Max. Capacitive Load on MemRef, USBCLK, REF PCICLK, 3V66                                       |        | 20<br>30 | pF   |

| f <sub>(REF)</sub>                                                                                                                                    | Reference Frequency, Oscillator Nominal Value                                                  | 14.318 | 14.318   | MHz  |

| t <sub>PU</sub>                                                                                                                                       | Power-up time for all VDD's to reach minimum specified voltage (power ramps must be monotonic) | 0.05   | 50       | ms   |

# **Electrical Characteristics** Over the Operating Range

| Parameter          | Description               | Test Conditions                                  |                                       |       | Max.  | Unit |

|--------------------|---------------------------|--------------------------------------------------|---------------------------------------|-------|-------|------|

| V <sub>IH</sub>    | High-level Input Voltage  | Except Crystal Pads. Threshold voltage           | for crystal pads = V <sub>DD</sub> /2 | 2.0   |       | V    |

| V <sub>IL</sub>    | Low-level Input Voltage   | Except Crystal Pads                              |                                       |       | 0.8   | V    |

| V <sub>OH</sub>    | High-level Output Voltage | MemRef, USB, REF, 3V66 $I_{OH} = -1 \text{ mA}$  |                                       | 2.4   |       | V    |

|                    |                           | PCI                                              | I <sub>OH</sub> = -1 mA               | 2.4   |       | V    |

| V <sub>OL</sub>    | Low-level Output Voltage  | MemRef, USB, REF, 3V66                           | I <sub>OL</sub> = 1 mA                |       | 0.4   | V    |

|                    |                           | PCI                                              | I <sub>OL</sub> = 1 mA                |       | 0.55  | V    |

| I <sub>IH</sub>    | Input High Current        | $0 \le V_{IN} \le V_{DD}$                        | -5                                    | 5     | μΑ    |      |

| I <sub>IL</sub>    | Input Low Current         | $0 \le V_{IN} \le V_{DD}$                        |                                       |       | 5     | μΑ   |

| I <sub>OH</sub>    | High-level Output Current | CPU<br>For I <sub>OH</sub> =6*IRef Configuration | Type X1, V <sub>OH</sub> = 0.65V      | -12.9 | -14.9 | mA   |

|                    |                           | USB, REF                                         | Type 3, V <sub>OH</sub> = 2.4V        | -15   | -51   |      |

|                    |                           | 3V66, PCI, MemRef, MemRefB                       | Type 5, V <sub>OH</sub> = 2.4V        | -30   | -100  |      |

| I <sub>OL</sub>    | Low-level Output Current  | USB, REF                                         | Type 3, $V_{OL} = 0.4V$               | 10    | 24    | mA   |

|                    |                           | 3V66, PCI, MemRef, MemRefB                       | Type 5, V <sub>OL</sub> =0.4 V        | 20    | 49    |      |

| I <sub>OZ</sub>    | Output Leakage Current    | Three-state                                      |                                       |       | 10    | μА   |

| I <sub>DD3</sub>   | 3.3V Power Supply Current | $AV_{DD}/V_{DD33} = 3.465V, F_{CPU} = 133 MHz$   |                                       |       | 250   | mA   |

| I <sub>DDPD3</sub> | 3.3V Shutdown Current     | $AV_{DD}/V_{DDQ3} = 3.465V$                      |                                       |       | 60    | mA   |

Document #: 38-07206 Rev. \*A

# Switching Characteristics<sup>[4]</sup> Over the Operating Range

| Parameter              | Output                                 | Description                                         | Test Conditions                                                                                   | Min.                         | Max.                         | Unit |

|------------------------|----------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------|------------------------------|------|

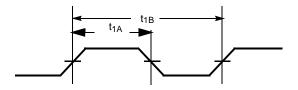

| t <sub>1</sub>         | All                                    | Output Duty Cycle <sup>[5]</sup>                    | t <sub>1A</sub> /(t <sub>1B</sub> )                                                               | 45                           | 55                           | %    |

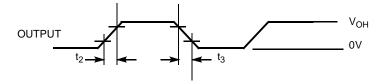

| t <sub>2</sub>         | CPU                                    | Rise Time                                           | Measured at 20% to 80% of V <sub>OH</sub>                                                         | 175                          | 700                          | ps   |

| t <sub>2</sub>         | USB, REF                               | Rising Edge Rate                                    | Between 0.4V and 2.4V                                                                             | 0.5                          | 2.0                          | V/ns |

| t <sub>2</sub>         | PCI, 3V66,<br>MemRef                   | Rising Edge Rate                                    | Between 0.4V and 2.4V                                                                             | 1.0                          | 4.0                          | V/ns |

| t <sub>3</sub>         | CPU                                    | Fall Time Measured at 80% to 20% of V <sub>OH</sub> |                                                                                                   | 175                          | 700                          | ps   |

| t <sub>3</sub>         | USB, REF                               | Falling Edge Rate                                   | Between 2.4V and 0.4V                                                                             | 0.5                          | 2.0                          | V/ns |

| t <sub>3</sub>         | PCI, 3V66,<br>MemRef                   | Falling Edge Rate                                   | Between 2.4V and 0.4V                                                                             | 1.0                          | 4.0                          | V/ns |

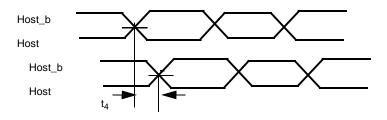

| t <sub>4</sub>         | CPU CPU-CPU Skew Measured at Crossover |                                                     |                                                                                                   | 150                          | ps                           |      |

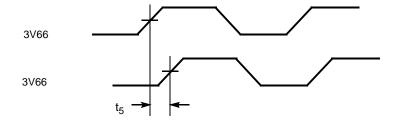

| t <sub>5</sub>         | 3V66                                   | 3V66-3V66 Skew                                      | Measured at 1.5V                                                                                  |                              | 250                          | ps   |

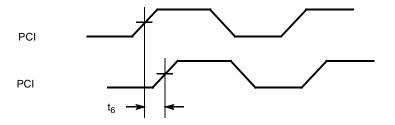

| t <sub>6</sub>         | PCI                                    | PCI-PCI Skew                                        | Measured at 1.5V                                                                                  |                              | 500                          | ps   |

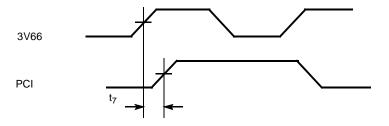

| t <sub>7</sub>         | 3V66,PCI                               | 3V66-PCI Clock Skew                                 | 3V66 leads. Measured at 1.5V                                                                      | 1.5                          | 3.5                          | ns   |

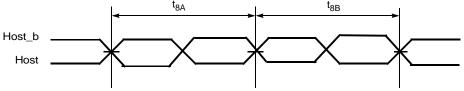

| t <sub>8</sub>         | CPU                                    | Cycle-Cycle Clock Jitter                            | Measured at Crossover t <sub>8</sub> = t <sub>8A</sub> - t <sub>8B</sub> With all outputs running |                              | 200                          | ps   |

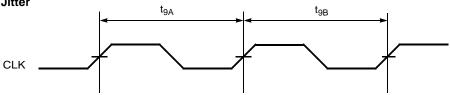

| t <sub>9</sub>         | Mref                                   | Cycle-Cycle Clock Jitter                            | Measured at 1.5V $t_9 = t_{9A} - t_{9B}$                                                          |                              | 250                          | ps   |

| t <sub>9</sub>         | 3V66                                   | Cycle-Cycle Clock Jitter                            | Measured at 1.5V $t_9 = t_{9A} - t_{9B}$                                                          |                              | 300                          | ps   |

| t <sub>9</sub>         | USB                                    | Cycle-Cycle Clock Jitter                            | Measured at 1.5V $t_9 = t_{9A} - t_{9B}$                                                          |                              | 350                          | ps   |

| t <sub>9</sub>         | PCI                                    | Cycle-Cycle Clock Jitter                            | Measured at 1.5V $t_9 = t_{9A} - t_{9B}$                                                          |                              | 500                          | ps   |

| t <sub>9</sub>         | REF                                    | Cycle-Cycle Clock Jitter                            | Measured at 1.5V $t_9 = t_{9A} - t_{9B}$                                                          |                              | 1000                         | ps   |

|                        | CPU, PCI                               | Settle Time                                         | CPU and PCI clock stabilization from power-up                                                     |                              | 3                            | ms   |

|                        | CPU                                    | Rise/Fall Matching                                  | Measured with test loads <sup>[6, 7]</sup>                                                        |                              | 20%                          |      |

|                        | CPU Overshoot                          |                                                     | Measured with test loads <sup>[7]</sup>                                                           |                              | V <sub>OH</sub> + 0.2        | V    |

|                        | CPU                                    | Undershoot                                          | Measured with test loads <sup>[7]</sup>                                                           | -0.2                         |                              | V    |

| V <sub>oh</sub>        | CPU                                    | High-level Output Voltage                           | Measured with test loads <sup>[7]</sup>                                                           | 0.65                         | 0.74                         | V    |

| V <sub>ol</sub>        | CPU                                    | Low-level Output Voltage                            | Measured with test loads <sup>[7]</sup>                                                           | 0.0                          | 0.05                         | V    |

| V <sub>crossover</sub> | CPU                                    | Crossover Voltage                                   | Measured with test loads <sup>[7]</sup>                                                           | 45%<br>of<br>V <sub>OH</sub> | 55%<br>of<br>V <sub>OH</sub> | V    |

- All parameters specified with loaded outputs. Parameters not tested in production, but are guaranteed by design characterization. Duty cycle is measured at 1.5V with V<sub>DD</sub> at 3.3V on all output except CPU. Duty Cycle on CPU is measured at V<sub>Crossover</sub>.

Determined as a fraction of 2\*(t<sub>RP</sub> t<sub>RN</sub>)/(t<sub>RP</sub> + t<sub>RN</sub>) Where t<sub>RP</sub> is a rising edge and t<sub>RN</sub> is an intersecting falling edge.

The test load is specified in test circuit.

# **Switching Waveforms**

# **Duty Cycle Timing** (Single Ended Output)

# **Duty Cycle Timing (CPU Differential Output)**

#### All Outputs Rise/Fall Time

#### **CPU-CPU Clock Skew**

#### 3V66-3V66 Clock Skew

# Switching Waveforms (continued)

#### **PCI-PCI Clock Skew**

#### **3V66-PCI Clock Skew**

#### **CPU Clock Cycle-Cycle Jitter**

#### **Cycle-Cycle Clock Jitter**

#### Note

<sup>8.</sup> Shaded section on the VCO and Crystal waveforms indicates that the VCO and crystal oscillator are active, and there is a valid clock.

#### Test Circuit<sup>[9, 10]</sup>

# **Ordering Information**

| Ordering Code | Package<br>Name | Package Type | Operating<br>Range |

|---------------|-----------------|--------------|--------------------|

| CY2220PVC-1   | O56             | 56-Pin SSOP  | Commercial         |

| CY2220PVC-2   | O56             | 56-Pin SSOP  | Commercial         |

#### Notes:

<sup>9.</sup> Each supply pin must have an individual decoupling capacitor.

<sup>10.</sup> All capacitors must be placed as close to the pins as is physically possible.

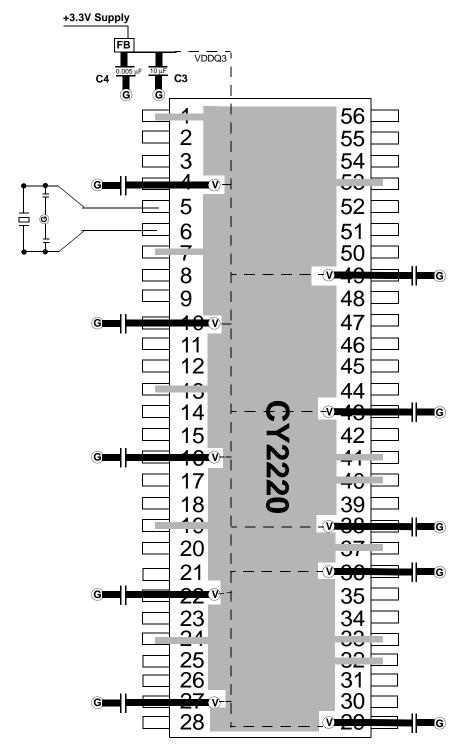

# **Layout Example**

FB = Dale ILB1206 - 300 (30 $\Omega$  @ 100 MHz)

Cermaic Caps C3 =  $10-22 \mu F$  C4 =  $0.005 \mu F$

G = VIA to GND plane layer V =VIA to respective supply plane layer

Note: Each supply plane or strip should have a ferrite bead and capacitors All bypass caps = 0.01  $\mu F$  ceramic

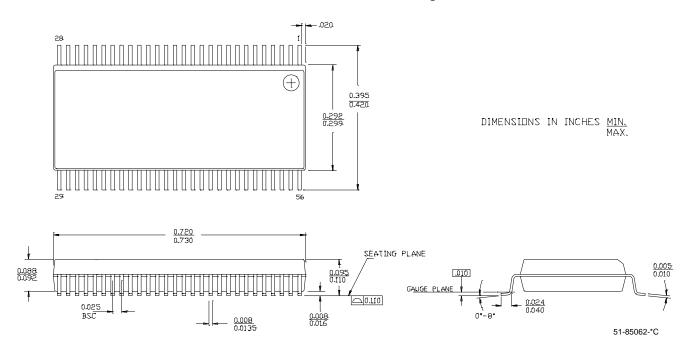

#### **Package Diagram**

#### 56-Lead Shrunk Small Outline Package O56

| Document Title: CY2220 133-MHz Spread Spectrum Clock Synthesizer/Driver with Differential CPU Outputs Document Number: 38-07206 |        |          |                       |                                                                 |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|--------|----------|-----------------------|-----------------------------------------------------------------|--|--|

| REV. ECN NO. Issue Orig. of Change                                                                                              |        |          | Description of Change |                                                                 |  |  |

| **                                                                                                                              | 111730 | 01/17/02 | DSG                   | Change from Spec number: 38-00813 to 38-07206                   |  |  |

| *A                                                                                                                              | 121841 | 12/30/02 | RBI                   | Power up requirements added to Operating Conditions Information |  |  |