# 2% 5V, 750mA Low Dropout Linear Regulator with Delayed RESET

The CS8122 is a precision 5V linear regulator capable of sourcing in excess of 750mA. The  $\overline{\text{RESET}}$ 's delay time is externally programmed using a discrete RC network. During power up, or when the output goes out of regulation, the **RESET** lead remains in the low state for the duration of the delay. This function is independent of the input voltage and will function correctly as long as the output voltage remains at or above 1V. Hysteresis is included in the Delay and the **RESET** comparators to improve noise immunity. A latching discharge circuit is used to discharge the delay capacitor when it is triggered by a brief fault condition.

## Description

The regulator is protected against a variety of fault conditions: i.e. reverse battery, overvoltage, short circuit and thermal runaway conditions. The regulator is protected against voltage transients ranging from -50V to +40V. Short circuit current is limited to 1.2A (typ).

The CS8122 is an improved replacement for the CS8126 and features a tighter tolerance on its output voltage (2% vs 4%).

The CS8122 is packaged in a 5 lead TO–220 with copper tab. The copper tab can be connected to a heat sink if necessary.

1

### Features

CS8122

- 5V +/- 2% Regulated Output

- Low Dropout Voltage (0.6V @ 0.5A)

- 750mA Output Current Capability

- Externally Programmed RESET Delay

- Fault Protection Reverse Battery 60V Load Dump -50V Reverse Transient Short Circuit Thermal Shutdown

#### V<sub>IN</sub> Over Voltage Shutdowr νουτ Regulated Supply Regulato for Circuit Bias Error Amplifie Bandgap Anti-Saturatior Reference and Current Limit VOUTSENSE Thermal Charge Current Generat Shutdown (+) Latching Discharge Delay Delay Comparato ± vbisc RESET Gnd

Cherry Semiconductor Corporation 2000 South County Trail, East Greenwich, RI 02818 Tel: (401)885-3600 Fax: (401)885-5786 Email: info@cherry-semi.com Web Site: www.cherry-semi.com

#### **Block Diagram**

# 5 Lead TO-220

**Package Options**

Delay

RESÉT

| Input Operating Range                  |                         |

|----------------------------------------|-------------------------|

| Power Dissipation                      |                         |

| Transient Input Voltage                |                         |

| Output Current                         |                         |

| ESD Susceptibility (Human Body Model)  |                         |

| Junction Temperature                   | 55°C to 150°C           |

| Storage Temperature                    |                         |

| Lead Temperature Soldering             |                         |

| Wave Solder (through hole styles only) | 10 sec. max, 260°C peak |

## $\begin{array}{l} \mbox{Electrical Characteristics:} & -40^{\circ} \mbox{C} \leq T_{A} \leq +125^{\circ} \mbox{C}, -40^{\circ} \mbox{C} \leq T_{J} \leq +150^{\circ} \mbox{C}, \mbox{6V} \leq V_{IN} \leq 26 \mbox{V}, \mbox{5mA} \leq I_{OUT} \leq 500 \mbox{mA}, \\ & R_{\overline{RESET}} = 4.7 \mbox{k} \mbox{\Omega} \mbox{ to } V_{CC} \mbox{ unless otherwise noted}^{*} \end{array}$

|                                             | RESEI                                                                                                 |              |              |                                                  |        |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------|--------------|--------------------------------------------------|--------|

| PARAMETER                                   | TEST CONDITIONS                                                                                       | MIN          | ТҮР          | MAX                                              | UNI    |

| Output Stage (V <sub>OUT</sub> )            |                                                                                                       |              |              |                                                  |        |

| Output Voltage                              |                                                                                                       | 4.9          | 5.0          | 5.1                                              | V      |

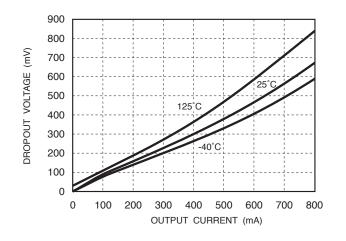

| Dropout Voltage                             | $I_{OUT} = 500 \text{mA}$                                                                             |              | 0.35         | 0.60                                             | V      |

| Supply Current                              | $\begin{split} I_{OUT} &\leq 10 mA \\ I_{OUT} &\leq 100 mA \\ I_{OUT} &\leq 500 mA \end{split}$       |              | 2<br>6<br>55 | 7<br>12<br>100                                   | mA     |

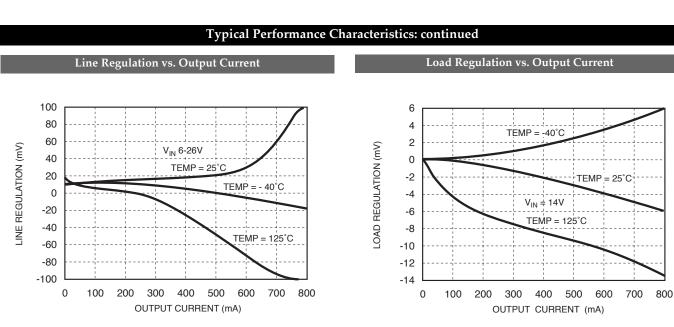

| Line Regulation                             | $6V \leq V_{IN} \leq 26V, \ I_{OUT} = 50mA$                                                           |              | 5            | 50                                               | mV     |

| Load Regulation                             | $50mA \le I_{OUT} \le 500mA$ , $V_{IN} = 14V$                                                         |              | 10           | 50                                               | mV     |

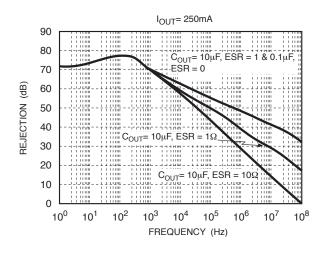

| Ripple Rejection                            | $f = 120Hz, V_{IN} = 7 \text{ to } 17V,$ 54<br>$I_{OUT} = 250\text{mA}$                               |              | 75           |                                                  | dB     |

| Current Limit                               |                                                                                                       | 0.75         | 1.20         |                                                  | А      |

| Overvoltage Shutdown                        |                                                                                                       | 32           |              | 40                                               | V      |

| Maximum Line Transient                      | $V_{OUT} \le 5.5 V$                                                                                   | 60           | 95           |                                                  | V      |

| Reverse Polarity Input<br>Voltage DC        | $V_{OUT} \ge -0.6V$ , 10 $\Omega$ Load                                                                | -15          | -30          |                                                  | V      |

| Reverse Polarity Input<br>Voltage Transient | 1% Duty Cycle, T < 100ms,<br>10Ω Load                                                                 | -50          | -80          |                                                  | V      |

| Thermal Shutdown                            | Guaranteed by Design                                                                                  | 150          | 180          | 210                                              | °C     |

| <b>RESET</b> and Delay Functions            |                                                                                                       |              |              |                                                  |        |

| Delay Charge Current                        | $V_{DELAY} = 2V$                                                                                      | 5            | 10           | 15                                               | μA     |

| RESET Threshold                             | V <sub>OUT</sub> Increasing, V <sub>RT(ON)</sub><br>V <sub>OUT</sub> Decreasing, V <sub>RT(OFF)</sub> | 4.65<br>4.50 | 4.90<br>4.70 | V <sub>OUT</sub> -0.01<br>V <sub>OUT</sub> -0.16 | V<br>V |

| <b>RESET</b> Hysteresis                     | $V_{RH} = V_{RT(ON)} - V_{RT(OFF)}$                                                                   | 150          | 200          | 250                                              | mV     |

| Delay Threshold                             | Charge, V <sub>DC(HI)</sub><br>Discharge, V <sub>DC(L)</sub>                                          | 3.25<br>2.85 | 3.50<br>3.10 | 3.75<br>3.35                                     | V<br>V |

| Delay Hysteresis                            |                                                                                                       | 200          | 400          | 800                                              | mV     |

| <b>RESET</b> Output Voltage Low             | $1V < V_{OUT} < V_{RT(L)}$ , $3k\Omega$ to $V_{OUT}$                                                  |              | 0.1          | 0.4                                              | V      |

| RESET Output Leakage                        | V <sub>OUT</sub> > V <sub>RT(H)</sub><br>Current                                                      | 0            |              | 10                                               | μA     |

| Delay Capacitor<br>Discharge Voltage        | Discharge Latched "ON",<br>V <sub>OUT</sub> > V <sub>RT</sub>                                         |              | 0.2          | 0.5                                              | V      |

| Delay Time                                  | $C_{DELAY} = 0.1 \mu F$                                                                               | 16           | 32           | 48                                               | ms     |

\* To observe safe operating junction temperatures, low duty cycle pulse testing is used in tests where applicable.

Delay Time =  $\frac{C_{Delay} \times V_{Delay Threshold Charge}}{I_{T}} = C_{Delay} \times 3.5 \times 10^{5} (typ)$

I<sub>Charge</sub>

| Package Lead Description |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PACKAGE LEAD #           | LEAD SYMBOL      | ge Lead Description Grant Gr |

| 5Lead TO-220             |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1                        | V <sub>IN</sub>  | Unregulated supply voltage to IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2                        | V <sub>OUT</sub> | Regulated 5V output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3                        | Gnd              | Ground connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4                        | Delay            | Timing capacitor for RESET function.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5                        | RESET            | CMOS/TTL compatible output lead. $\rm \overline{RESET}$ goes low whenever $V_{OUT}$ drops below 6% of it's regulated value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

**Typical Performance Characteristics** Quiescent Current vs Input Voltage over Temperature Quiescent Current vs Input Voltage over Load Resistance 55.0 120.0  $R_{load} = 25\Omega$ Room Temp. 50.0  $R_{load} = 6.67\Omega$ 45.0 100.0 Quiescent Current (mA) 40.0 Quiescent Current (mA) 80.0 35.0 30.0 125°C 60.0 25.0  $R_{load} = 10\Omega$ 20.0 40.0 15.0 25°C 4 10.0 20.0  $d = 25\Omega$ -40°C R. 5.0 R<sub>load</sub> = NO LOAD 0.0 0.0  $0.0 \quad 1.0 \quad 2.0 \quad 3.0 \quad 4.0 \quad 5.0 \quad 6.0 \quad 7.0 \quad 8.0 \quad 9.0 \quad 10.0$ 0.0 1.0 2.0 3.0 4.0 5.0 6.0 7.0 8.0 9.0 10.0  $V_{IN}\left(V\right)$  $V_{IN}\left(V

ight)$ Output Voltage vs Input Voltage over Temperature V<sub>OUT</sub> vs. V<sub>IN</sub> over R<sub>LOAD</sub> 5.5 5.5 Room Temp. 5.0 R<sub>load</sub>=25Ω 5.0 4.5 4.5 4.0 4.0  $R_{load} = 6.67\Omega$ 3.5 3.5 V<sub>OUT</sub> (V) 3.0 V<sub>OUT</sub> (V) 3.0 2.5 125°C 2.5 2.0 R<sub>load</sub> = NO LOAD 2.0 1.5 1.5 С -40°C 1.0 1.0  $10\Omega$ Rload 0.5 0.5 0.0 0.0 0.0 1.0 2.0 3.0 4.0 5.0 6.0 7.0 8.0 9.0 10.0 0.0 1.0 2.0 3.0 4.0 5.0 6.0 7.0 8.0 9.0 10.0  $V_{IN}(V)$

$V_{IN}(V)$

100 90

80

70

60

50

40

30

QUIESCENT CURRENT (mA)

Dropout Voltage vs. Output Current

Quiescent Current vs. Output Current

125°C

-40°C

25°C

$V_{IN} = 14V$

4

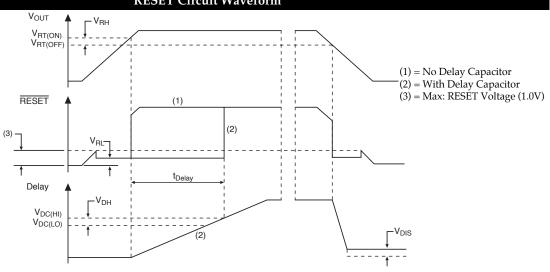

#### **RESET** Circuit Waveform

**Circuit Description**

The CS8122 RESET function, has hysteresis on both the reset and delay comparators, a latching Delay capacitor discharge circuit, and operates down to 1V.

The **RESET** circuit output is an open collector type with ON and OFF parameters as specified. The RESET output NPN transistor is controlled by the two circuits described (see Block Diagram).

#### Low Voltage Inhibit Circuit

The Low Voltage Inhibit Circuit monitors output voltage, and when output voltage is below the specified minimum, causes the **RESET** output transistor to be in the ON (saturation) state. When the output voltage is above the specified level, this circuit permits the RESET output transistor to go into the OFF state if allowed by the RESET Delay circuit.

#### **Reset Delay Circuit**

CS8122

The Reset Delay Circuit provides a programmable (by external capacitor) delay on the RESET output lead. The Delay lead provides source current to the external delay capacitor only when the Low Voltage Inhibit circuit indicates that output voltage is above V<sub>RT(ON)</sub>. Otherwise, the Delay lead sinks current to ground (used to discharge the delay capacitor). The discharge current is latched ON when the output voltage is below  $V_{RT(OFF)}$ . The Delay capacitor is fully discharged anytime the output voltage falls out of regulation, even for a short period of time. This feature ensures that a controlled **RESET** pulse is generated following detection of an error condition. The circuit allows the **RESET** output transistor to go to the OFF (open) state only when the voltage on the Delay lead is higher than V<sub>DC(HI)</sub>.

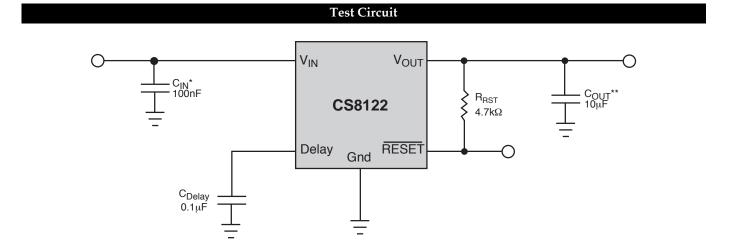

\*C<sub>IN</sub> required if regulator is far from power source filter.

\*\*C<sub>OUT</sub> required for stability.

# CS8122

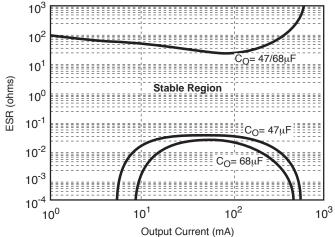

#### **Stability Considerations**

The output or compensation capacitor helps determine three main characteristics of a linear regulator: start-up delay, load transient response and loop stability.

The capacitor value and type should be based on cost, availability, size and temperature constraints. A tantalum or aluminum electrolytic capacitor is best, since a film or ceramic capacitor with almost zero ESR can cause instability. The aluminum electrolytic capacitor is the least expensive solution, but, if the circuit operates at low temperatures (-25°C to -40°C), both the value and ESR of the capacitor will vary considerably. The capacitor manufacturers data sheet usually provides this information.

The value for the output capacitor  $C_{OUT}$  shown in the test and applications circuit should work for most applications, however it is not necessarily the optimized solution.

To determine an acceptable value for  $C_{OUT}$  for a particular application, start with a tantalum capacitor of the recommended value and work towards a less expensive alternative part.

**Step 1:** Place the completed circuit with a tantalum capacitor of the recommended value in an environmental chamber at the lowest specified operating temperature and monitor the outputs with an oscilloscope. A decade box connected in series with the capacitor will simulate the higher ESR of an aluminum capacitor. Leave the decade box outside the chamber, the small resistance added by the longer leads is negligible.

**Step 2:** With the input voltage at its maximum value, increase the load current slowly from zero to full load while observing the output for any oscillations. If no oscillations are observed, the capacitor is large enough to ensure a stable design under steady state conditions.

**Step 3:** Increase the ESR of the capacitor from zero using the decade box and vary the load current until oscillations appear. Record the values of load current and ESR that cause the greatest oscillation. This represents the worst case load conditions for the regulator at low temperature.

**Step 4**: Maintain the worst case load conditions set in step 3 and vary the input voltage until the oscillations increase. This point represents the worst case input voltage conditions.

**Step 5:** If the capacitor is adequate, repeat steps 3 and 4 with the next smaller valued capacitor. A smaller capacitor will usually cost less and occupy less board space. If the output oscillates within the range of expected operating conditions, repeat steps 3 and 4 with the next larger standard capacitor value.

**Step 6:** Test the load transient response by switching in various loads at several frequencies to simulate its real working environment. Vary the ESR to reduce ringing.

**Step 7:** Remove the unit from the environmental chamber and heat the IC with a heat gun. Vary the load current as instructed in step 5 to test for any oscillations.

Once the minimum capacitor value with the maximum ESR is found, a safety factor should be added to allow for the tolerance of the capacitor and any variations in regulator performance. Most good quality aluminum electrolytic capacitors have a tolerance of  $\pm 20\%$  so the minimum value found should be increased by at least 50% to allow

for this tolerance plus the variation which will occur at low temperatures. The ESR of the capacitor should be less than 50% of the maximum allowable ESR found in step 3 above.

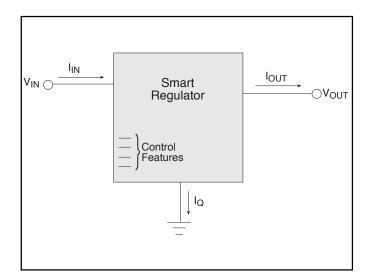

> Calculating Power Dissipation in a Single Output Linear Regulator

The maximum power dissipation for a single output regulator (Figure 1) is:

$$P_{D(max)} = [V_{IN(max)} - V_{OUT(min)}]I_{OUT(max)} + V_{IN(max)}I_Q$$

(1)

where

Ŀ

V<sub>IN(max)</sub> is the maximum input voltage,

V<sub>OUT(min)</sub> is the minimum output voltage,

$I_{\text{OUT}(\text{max})}$  is the maximum output current for the application, and

$I_Q$  is the quiescent current the regulator consumes at  $I_{OUT(max)}.$

Once the value of  $P_{D(max)}$  is known, the maximum permissible value of  $R_{\Theta JA}$  can be calculated:

$$R_{\Theta JA} = \frac{150^{\circ}\text{C} - \text{T}_{A}}{P_{D}}$$

(2)

The value of  $R_{\Theta JA}$  can then be compared with those in the package section of the data sheet. Those packages with  $R_{\Theta JA}$ 's less than the calculated value in equation 2 will keep the die temperature below 150°C.

In some cases, none of the packages will be sufficient to dissipate the heat generated by the IC, and an external heatsink will be required.

Figure 1: Single output regulator with key performance parameters labeled.

#### Heat Sinks

A heat sink effectively increases the surface area of the package to improve the flow of heat away from the IC and into the surrounding air.

Each material in the heat flow path between the IC and the outside environment will have a thermal resistance. Like series electrical resistances, these resistances are summed to determine the value of  $R_{\Theta JA}$ :

$$R_{\Theta JA} = R_{\Theta JC} + R_{\Theta CS} + R_{\Theta SA}$$

(3)

where:

$R_{\Theta IC}$  = the junction–to–case thermal resistance,

$R_{\Theta CS}$  = the case-to-heatsink thermal resistance, and

$R_{\Theta SA}$  = the heatsink-to-ambient thermal resistance.

$R_{\Theta JC}$  appears in the package section of the data sheet. Like  $R_{\Theta JA}$ , it too is a function of package type.  $R_{\Theta CS}$  and  $R_{\Theta SA}$  are functions of the package type, heatsink and the interface between them. These values appear in heat sink data sheets of heat sink manufacturers.

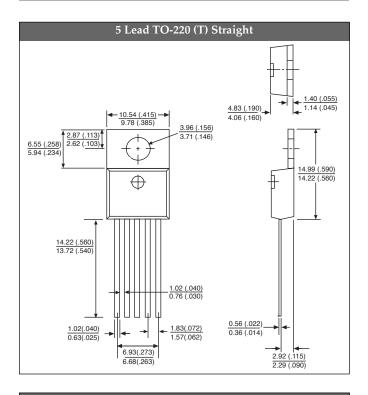

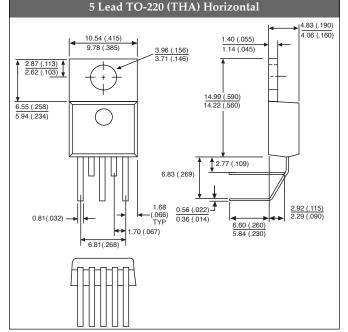

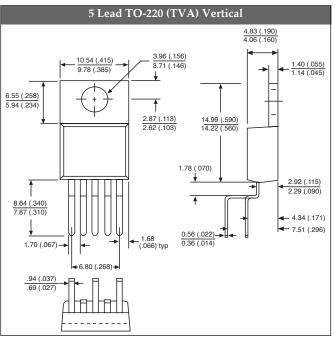

**Package Specification**

#### PACKAGE DIMENSIONS IN mm(INCHES)

| Ordering Information |                          |  |

|----------------------|--------------------------|--|

| Part Number          | Description              |  |

| CS8122YT5            | 5 Lead TO-220 Straight   |  |

| CS8122YTHA5          | 5 Lead TO-220 Horizontal |  |

| CS8122YTVA5          | 5 Lead TO-220 Vertical   |  |

#### PACKAGE THERMAL DATA

| Therma          | l Data | 5 Lead TO-220 |      |

|-----------------|--------|---------------|------|

| $R_{\Theta JC}$ | typ    | 2.1           | °C/W |

| $R_{\Theta JA}$ | typ    | 50            | °C/W |

Cherry Semiconductor Corporation reserves the right to make changes to the specifications without notice. Please contact Cherry Semiconductor Corporation for the latest available information.