March 1997

# Features

- Cascadable Up to 4 Units for 32-Bit by 32-Bit Multiply or 64  $\div$  32-Bit Divide

- 8-Bit by 8-Bit Multiply or 16  $\div$  8-Bit Divide in 5.6 $\mu s$  at 5V or 2.8 $\mu s$  at 10V

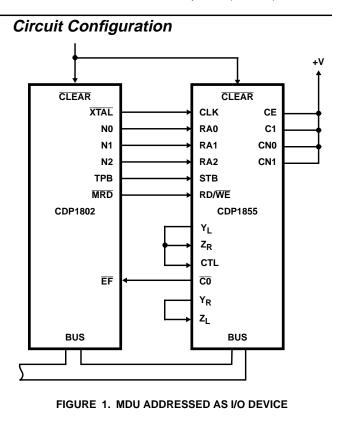

- Direct Interface to CDP1800-Series Microprocessors

- · Easy Interface to Other 8-Bit Microprocessors

- Significantly Increases Throughput of Microprocessor Used for Arithmetic Calculations

# Ordering Information

| PACKAGE | TEMP. RANGE    | 5V         | 10V      | PKG.<br>NO. |

|---------|----------------|------------|----------|-------------|

| PDIP    | -40°C to +85°C | CDP1855CE  | CDP1855E | E28.6       |

| Burn-In |                | CDP1855CEX | -        | E28.6       |

| SBDIP   | -40°C to +85°C | CDP1855CD  | CDP1855D | D28.6       |

| Burn-In |                | CDP1855CDX | -        | D28.6       |

# Description

The CDP1855 and CDP1855C are CMOS 8-bit multiply/divide units which can be used to greatly increase the capabilities of 8-bit microprocessors. They perform multiply and divide operations on unsigned, binary operators. In general, microprocessors do not contain multiply or divide instructions and even efficiently coded multiply or divide subroutines require considerable memory and execution time. These multiply/divide units directly interface to the CDP1800-series microprocessors via the N-lines and can easily be configured to fit in either the memory or I/O space of other 8-bit microprocessors.

CDP1855,

**CDP1855C**

8-Bit Programmable Multiply/Divide Unit

The multiple/divide unit is based on a method of multiplying by add and shift right operations and dividing by subtract and shift left operations. The device is structured to permit cascading identical units to handle operands up to 32 bits.

The CDP1855 and CDP1855C are functionally identical. They differ in that the CDP1855 has a recommended operating voltage range of 4V to 10.5V, and the CDP1855C, a recommended operating voltage range of 4V to 6.5V.

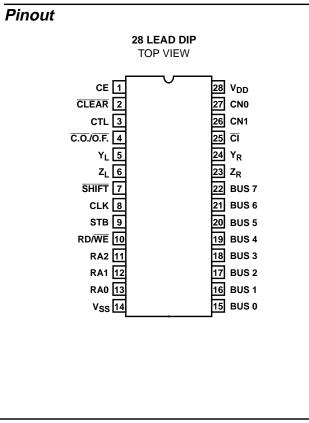

The CDP1855 and CDP1855C types are supplied in a 28 lead hermetic dual-in-line ceramic package (D suffix) and in a 28 lead dual-in-line plastic package (E suffix). The CDP1855C is also available in chip form (H suffix).

# **Absolute Maximum Ratings**

#### Therm

| (All voltage values referenced to V <sub>SS</sub> terminal)  |

|--------------------------------------------------------------|

| CDP1855                                                      |

| CDP1855C                                                     |

| Input Voltage Range, All Inputs0.5V to V <sub>DD</sub> +0.5V |

| DC Input Current, Any One Input                              |

# **Thermal Information**

| Thermal Resistance (Typical)                      | $\theta_{JA}$ ( <sup>o</sup> C/W) | θ <sub>JC</sub> ( <sup>o</sup> C/W)   |

|---------------------------------------------------|-----------------------------------|---------------------------------------|

| PDIP Package                                      | 55                                | N/A                                   |

| SBDIP Package                                     | 50                                | 12                                    |

| Device Dissipation Per Output Transistor          |                                   |                                       |

| For T <sub>A</sub> = Full Package-Temperature Rar | nge                               |                                       |

| (All Package Types)                               |                                   |                                       |

| Operating Temperature Range (T <sub>A</sub> )     |                                   |                                       |

| Storage Temperature Range (T <sub>STg</sub> )     | 65 <sup>0</sup>                   | <sup>o</sup> C to +150 <sup>o</sup> C |

| Lead Temperature (During Soldering)               |                                   |                                       |

| At distance $1/16 \pm 1/32$ In. $(1.59 \pm 0.79)$ | mm)                               |                                       |

| from case for 10s max                             |                                   | +265 <sup>о</sup> С                   |

|                                                   |                                   |                                       |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

# Static Electrical Specifications At $T_A = -40$ to +85°C, $V_{DD} \pm 10\%$ , Unless Otherwise Specified

|                           |                  | cc                    | NDITION                | s                      |       |                | LIM | ITS   |                |     |       |

|---------------------------|------------------|-----------------------|------------------------|------------------------|-------|----------------|-----|-------|----------------|-----|-------|

|                           |                  |                       |                        |                        |       | CDP1855        |     |       | CDP1855C       |     |       |

| PARAMETER                 |                  | V <sub>O</sub><br>(V) | V <sub>IN</sub><br>(V) | V <sub>DD</sub><br>(V) | MIN   | (NOTE1)<br>TYP | мах | MIN   | (NOTE1)<br>TYP | МАХ | UNITS |

| Quiescent Device          | I <sub>DD</sub>  | -                     | 0, 5                   | 5                      | -     | 0.01           | 50  | -     | 0.02           | 200 | μΑ    |

| Current                   |                  | -                     | 0, 10                  | 10                     | -     | 1              | 200 | -     | -              | -   | μΑ    |

| Output Low Drive (Sink)   | I <sub>OL</sub>  | 0.4                   | 0, 5                   | 5                      | 1.6   | 3.2            | -   | 1.6   | 3.2            | -   | mA    |

| Current                   |                  | 0.5                   | 0, 10                  | 10                     | 2.6   | 5.2            | -   | -     | -              | -   | mA    |

| Output High Drive         | I <sub>ОН</sub>  | 4.6                   | 0, 5                   | 5                      | -1.15 | -2.3           | -   | -1.15 | -2.3           | -   | mA    |

| (Source) Current          |                  | 9.5                   | 0, 10                  | 10                     | -2.6  | -5.2           | -   | -     | -              | -   | mA    |

| Output Voltage Low Level  | V <sub>OL</sub>  | -                     | 0, 5                   | 5                      | -     | 0              | 0.1 | -     | 0              | 0.1 | V     |

| (Note 2)                  |                  | -                     | 0, 10                  | 10                     | -     | 0              | 0.1 | -     | -              | -   | V     |

| Output Voltage High Level | V <sub>OH</sub>  | -                     | 0, 5                   | 5                      | 4.9   | 5              | -   | 4.9   | 5              | -   | V     |

| (Note 2)                  |                  | -                     | 0, 10                  | 10                     | 9.9   | 10             | -   | -     | -              | -   | V     |

| Input Low Voltage         | V <sub>IL</sub>  | 0.5, 4.5              | -                      | 5                      | -     | -              | 1.5 | -     | -              | 1.5 | V     |

|                           |                  | 0.5, 9.5              | -                      | 10                     | -     | -              | 3   | -     | -              | -   | V     |

| Input High Voltage        | VIH              | 0.5, 4.5              | -                      | 5                      | 3.5   | -              | -   | 3.5   | -              | -   | V     |

|                           |                  | 0.5, 9.5              | -                      | 10                     | 7     | -              | -   | -     | -              | -   | V     |

| Input Leakage Current     | I <sub>IN</sub>  | -                     | 0, 5                   | 5                      | -     | -              | ±1  | -     | -              | ±1  | μΑ    |

|                           |                  | -                     | 0, 10                  | 10                     | -     | -              | ±1  | -     | -              | -   | μΑ    |

| Three-State Output        | I <sub>OUT</sub> | 0, 5                  | 0, 5                   | 5                      | -     | -              | ±1  | -     | -              | ±1  | μΑ    |

| Leakage Current           |                  | 0, 10                 | 0, 10                  | 10                     | -     | -              | ±10 | -     | -              | -   | μΑ    |

| Operating Current         | I <sub>DD1</sub> | -                     | 0, 5                   | 5                      | -     | 1.5            | -   | -     | 1.5            | 3   | mA    |

| (Note 3)                  |                  | -                     | 0, 10                  | 10                     | -     | 6              | 12  | -     | -              | -   | mA    |

| Input Capacitance         | C <sub>IN</sub>  | -                     | -                      | -                      | -     | 5              | 7.5 | -     | 5              | 7.5 | pF    |

| Output Capacitance        | C <sub>OUT</sub> | -                     | -                      | -                      | -     | 10             | 15  | -     | 10             | 15  | pF    |

NOTES:

1. Typical values are for  $T_A = +25^{\circ}C$  and nominal  $V_{DD}$ .

2.  $I_{OL} = I_{OH} = 1\mu A$

3. Operating current is measured at 3.2MHz with open outputs.

**Recommended Operating Conditions** At  $T_A$  = Full package temperature range. For maximum reliability, operating conditions should be selected so that operation is always within the following ranges:

|                                             |                 |                 | LIM             | IITS            |                 |       |  |

|---------------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-------|--|

|                                             | V <sub>DD</sub> | CDP1855         |                 | CDP1855C        |                 | 1     |  |

| PARAMETER                                   | (V)             | MIN             | MAX             | MIN             | MAX             | UNITS |  |

| DC Operating Voltage Range                  | -               | 4               | 10.5            | 4               | 6.5             | V     |  |

| Input Voltage Range                         | -               | V <sub>SS</sub> | V <sub>DD</sub> | V <sub>SS</sub> | V <sub>DD</sub> | V     |  |

| Maximum Clock Input Frequency               | 5               | 3.2             | -               | 3.2             | -               | MHz   |  |

|                                             | 10              | 6.4             | -               | -               | -               | MHz   |  |

| Minimum 8 x 8 Multiply (16 ÷ 8 Divide) Time | 5               | -               | 5.6             | -               | 5.6             | μs    |  |

|                                             | 10              | -               | 2.8             | -               | -               | μs    |  |

# Functional Description

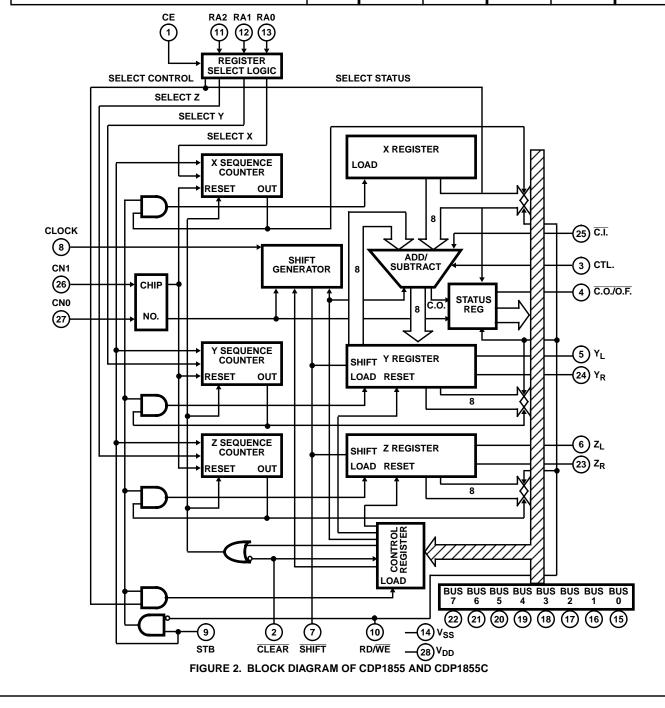

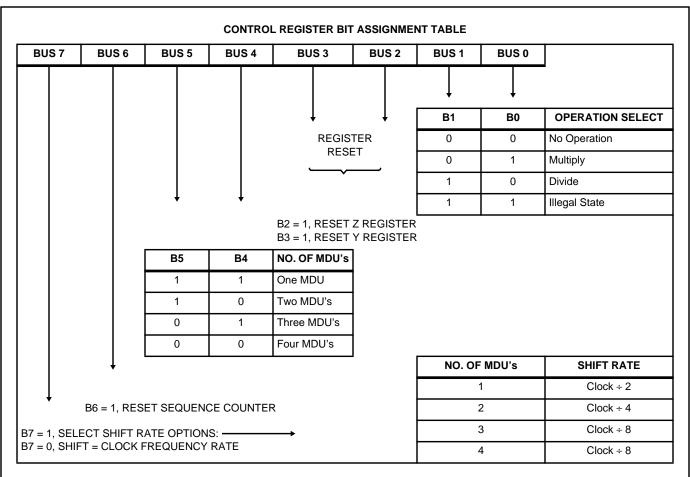

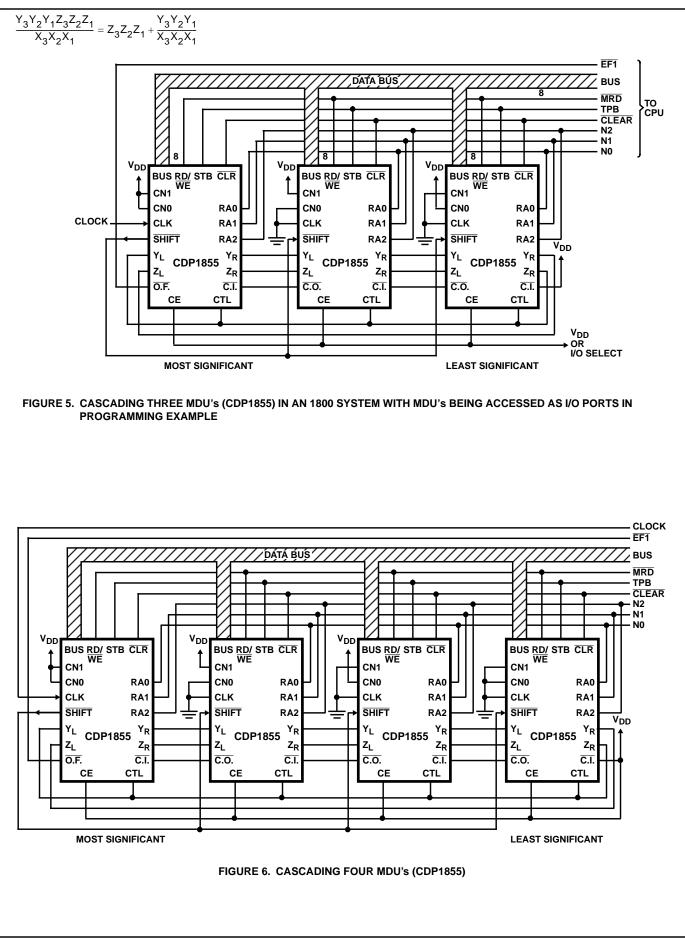

The CDP1855 is a multiply-divide unit (MDU) designed to be compatible with CDP1800 series microprocessor systems. It can, in fact, be interfaced to most 8-bit microprocessors (see Figure 5). The CDP1855 performs binary multiply or divide operations as directed by the microprocessor. It can do a 16N-bit by 8N-bit divide yielding a 8N-bit result plus and 8Nbit remainder. The multiply is an 8N-bit by 8N-bit operation with a 16N-bit result. The "N" represent the number of cascaded CDP1855's and can be 1, 2, 3 or 4. All operations require 8N + 1 shift pulses (See "DELAY NEEDED WITH AND WITHOUT PRESCALER").

The CDP1855 contains three registers, X, Y, and Z, which are loaded with the operands prior to an operation and contain the results at the completion. In addition, the control register must be loaded to initiate a multiply or divide. There is also a status register which contains an overflow flag as shown in the "CONTROL REGISTER BIT ASSIGNMENT TABLE". The register address lines (RA0-RA1) are used to select the appropriate register for loading or reading. The RD/WE and STB lines are used in conjunction with the RA lines to determine the exact MDU response (See "CONTROL TRUTH TABLE").

When multiple MDU's are cascaded, the loading of each register is done sequentially. For example, the first selection of register X for loading loads the most significant CDP1855, the second loads the next significant, and so on. Registers are also read out sequentially. This is accomplished by internal counters on each MDU which are decremented by STB during each register selection. When the counter matches the chip number (CN1, CN0 lines), the device is selected. These counters must be cleared with a clear on pin 2 or with bit 6 in the control word (See "CONTROL REGISTER BIT ASSIGNMENT TABLE") in order to start each sequence of accesses with the most significant device.

The CDP1855 has a built in clock prescaler which can be selected via bit 7 in the control register. The prescaler may be necessary in cascaded systems operating at high frequencies or in systems where a suitable clock frequency is not readily available. Without the prescaler select, the shift frequency is equal to the clock input frequency. With the prescaler selected, the rate depends on the number of MDU's as defined by bits 4 and 5 of the control word (See "CONTROL REGISTER BIT ASSIGNMENT TABLE").

- 1. For one MDU, the clock frequency is divided by 2.

- 2. For two MDU's the clock frequency is divided by 4.

- 3. For 3 or 4 MDU's, the clock frequency is divided by 8.

# Operation

# 1. Initialization and Controls

The CDP1855 must be cleared by a low on pin 2 during power-on which prevents bus contention problems at the Y<sub>L</sub>, Y<sub>R</sub> and Z<sub>L</sub>, Z<sub>R</sub> terminals and also resets the sequence counters and the shift pulse generator.

Prior to loading any other registers the control register must be loaded to specify the number of MDU's being used (See "CONTROL REGISTER BIT ASSIGNMENT TABLE").

Once the number of devices has been specified and the sequence counters cleared with a clear pulse or bit 6 of the control word, the X, Y, and Z registers can be loaded as defined in the "CONTROL TRUTH TABLE". All bytes of the X register can be loaded, then all bytes of the Y, and then all bytes of the Z, or they can be loaded randomly. Successive loads to a given register will always proceed sequentially from the most significant byte to the least significant byte, as previously described. Resetting the sequence counters select the most significant MDU. In a four MDU system, loading all MDU's results in the sequence counter pointing to the first MDU again. In all other configurations (1, 2, or 3 MDU's), the sequence counter must be reset prior to each series of register reads or writes.

#### 2. Divide Operation

For the divide operation, the divisor is loaded in the X register. The dividend is loaded in the Y and Z registers with the more significant half in the Y register and the less significant half in the Z register. These registers may be loaded in any order, and after loading is completed, a control word is loaded to specify a divide operation and the number of MDU's and also to reset the sequence counters and Y or Z register and select the clock option if desired. Clearing the sequence counters with bit 6 will set the MDU's up for reading the results.

The X register will be unaltered by the operation. The quotient will be in the Z register while the remainder will be in the Y register. An overflow will be indicated by the  $\overline{C.O./O.F.}$  of the most significant MDU and can also be determined by reading the status byte.

While the CDP1855 is specified to perform 16 by 8-bit divides, if the quotient of a divide operation exceeds the size of the Z register(s) (8N-bits - where N is the number of cascaded CDP1855's) the overflow bit in the Status Register will be set. Neither the quotient in Z nor the remainder in Y will represent a valid answer. This will always be the result of a division performed when the divisor (X) is equal to or less than the most significant 8N-bits of the dividend (Y).

The MDU can still be used for such computations if the divide is done in two steps. The dividend is split into two parts-the more significant 8N-bits and the less significant 8N-bits-and a divide done on each part. Each step yields an 8N-bit result for a total quotient of 16N-bits.

The first step consists of dividing the more significant 8Nbits by the divisor. This is done by clearing the Y register(s), loading the Z register(s) with the more significant 8N-bits of the dividend, and loading the X register(s) with the divisor. A division is performed and the resultant value in Z represents the more significant 8N-bits of the final quotient. The Z register(s) value must be unloaded and saved by the processor. A second division is performed using the remainder from the first division (in Y) as the more significant 8N-bits of the dividend and the less significant half of the original dividend loaded into the Z register. The divisor in X remains unaltered and is, by definition, larger than the remainder from the first division which is in Y. The resulting value in Z becomes the less significant 8N-bits of the final quotient and the value in Y is, as usual, the remainder.

Extending this technique to more steps allows division of any size number by an 8N-bit divisor.

Note that division by zero is never permitted and must be tested for and handled in software.

The following example illustrates the use of this algorithm.

#### Example:

Assume three MDU's capable of a by 24-bit division. The problem is to divide 00F273, 491C06H by 0003B4H.

| Step 1: | 000000 | , | 00F273 | / | 0003B4   | = | 000041 | R=0001BF |

|---------|--------|---|--------|---|----------|---|--------|----------|

|         | Y      |   | Z(MS)  |   | Х        |   | Z1     | Y1       |

| Step 2: | 0001BF | , | 491C06 | / | 0003B4   | = | 78C936 | R=00000E |

|         | Y1     |   | Z(LS)  |   | Х        |   | Z2     | Y2       |

| Result: | 000041 | , | 78C936 |   | R=00000E |   |        |          |

|         | Z1     |   | Z2     |   | Y2       |   |        |          |

The Z register can simply be reset using bit 2 of the control word and another divide can be done in order to further divide the remainder.

## 3. Multiply Operation

For a multiply operation the two numbers to be multiplied are loaded in the X and Z registers. The result is in the Y and Z register with Y being the more significant half and Z the less significant half. The X register will be unchanged after the operation is completed.

The original contents of the Y register are added to the product of X and Z. Bit 3 of the control word will reset register Y to 0 if desired.

# Functional Description of CDP1855 Terminals

# CE - Chip Enable (Input):

A high on this pin enables the CDP1855 MDU to respond to the select lines. All cascaded MDU's must be enabled together. CE also controls the three-state  $\overline{C.O./O.F.}$ , output of the most significant MDU.

# Clear (Input):

The CDP1855 MDU(s) must be cleared upon power-on with a low-on this pin. The clear signal resets the sequence counters, the shift pulse generator, and bits 0 and 1 of the control register.

# CTL - Control (Input):

This is an input pin. All CTL pins must be wired together and to the  $Y_1$  of the most significant CDP1855 MDU and to the

$Z_{R}$  of the least significant CDP1855 MDU. This signal is used to indicate whether the registers are to be operated on or only shifted.

# C.O./O.F. - Carry Out/Over Flow (Output):

This is a three-state output pin. It is the CDP1855 Carry Out signal and is connected to  $\overline{CI}$  (CARRY-IN) of the next more significant CDP1855 MDU, except for on the most significant MDU. On that MDU it is an overflow indicator and is enabled when chip enables is true. A low on this pin indicates that an overflow has occurred. The overflow signal is latched each time the control register is loaded, but is only meaningful after a divide command.

# Y<sub>L</sub>, Y<sub>R</sub> - Y-Left, Y-Right:

These are three-state bi-directional pins for data transfer between the Y registers of cascaded CDP1855 MDU's. The  $Y_R$  pin is an output and  $Y_L$  is an input during a multiply and the reverse is true at all other times. The  $Y_L$  pin must be connected to the  $Y_R$  pin of the next more significant MDU. An exception is that the  $Y_L$  pin of the most significant CDP1855 MDU must be connected to the  $Z_R$  pin of the least significant MDU and to the CTL pins of all MDU's. Also the  $Y_R$  pin of the least significant MDU is tied to the  $Z_L$  pin of the most significant MDU.

# Z<sub>L</sub>, Z<sub>R</sub> - Z-Left, Z-Right:

These are three-state bi-directional pins for data transfers between the "Z" registers of cascaded MDU's. The  $Z_R$  pin is an output and  $Z_L$  is an input during a multiply and the reverse is true at all other times. The  $Z_L$  pin must be tied to the  $Y_R$  pin of the next more significant MDU. An exception is that the  $Z_L$  in of the most significant MDU must be connected to the  $Y_R$  pin of the least significant MDU. Also, the  $Z_R$  pin of the least significant MDU. So the most significant MDU.

# Shift - Shift Clock:

This is a three-state bi-directional pin. It is an output on the most significant MDU. And an input on all other MDU's. It provides the MDU system timing pulses. All SHIFT pins must be connected together for cascaded operation. A maximum of the 8N +1 shifts are required for an operation where "N" equals the number of MDU devices that are cascaded.

# CLK - Clock (Input):

This pin should be grounded on all but the most significant MDU. There is an optional reduction of clock frequency available on this pin if so desired, controlled by bit 7 of the control byte.

# STB - Strobe (Input):

When RD/WE is low, data is latched from bus lines on the falling edge of this signal. It may be asynchronous to the clock. Strobe also increments the selected register's sequence counter during reads and writes. TPB would be used in CDP1800 systems.

# RD/WE - Read/Write Enable (Input):

This signal defines whether the selected register is to be read from or written to. In 1800 systems use  $\overline{\text{MRD}}$  if MDU's are addressed as I/O devices,  $\overline{\text{MWR}}$  is used if MDU's are addressed as memory devices.

## RA2, RA1, RA0 - Register Address (Input):

These input signals define which register is to be read from or written to. It can be seen in the "CONTROL TRUTH TABLE" that RA2 can be used as a chip enable. It is identical to the CE pin, except only CE controls the three-state  $\overline{C.O./O.F.}$  on the most significant MDU. In 1800 systems use N lines if MDU's are used as I/O devices, use address lines or function of address lines if MDU's are used as memory devices.

## Bus 0 - Bus 7 - Bus Lines:

Three-state bi-directional bus for direct interface with CDP1800 series and other 8-bit microprocessors.

# Z<sub>R</sub> - Z-Right:

See Pin 6.

# Y<sub>R</sub> - Y-Right:

See Pin 5.

#### CI- Carry In (Input):

This is an input for the carry from the next less significant MDU. On the least significant MDU it must be high (V<sub>DD</sub>) on all others it must be connected to the  $\overline{CO}$  pin of the next less significant MDU.

#### CN1, CN0 - Chip Number (Input):

These two input pins are wired high or low to indicate the MDU position in the cascaded chain. Both are high for the most significant MDU regardless of how many CDP1855 MDU's are used. Then CN1 = high and CN0 = low for the next MDU and so forth.

#### V<sub>SS</sub> - Ground:

Power supply line.

#### V<sub>DD</sub> - V+:

Power supply line.

|                                                |      |                    | INPUTS (NOTE 1) |                |             |             |             |    |  |  |

|------------------------------------------------|------|--------------------|-----------------|----------------|-------------|-------------|-------------|----|--|--|

| PONSE                                          | RES  |                    | STB<br>(TPB)    | RD/WE<br>(MRD) | RA0<br>(N0) | RA1<br>(N1) | RA2<br>(N2) | CE |  |  |

|                                                | ats) | No Action (Bus Flo | Х               | Х              | Х           | Х           | Х           | 0  |  |  |

|                                                | ats) | No Action (Bus Flo | Х               | Х              | Х           | Х           | 0           | Х  |  |  |

| <pre>Increment Sequence Counter When STB</pre> | ן    | X to Bus           | Х               | 1              | 0           | 0           | 1           | 1  |  |  |

|                                                | }    | Z to Bus           | Х               | 1              | 1           | 0           | 1           | 1  |  |  |

| and RD = 1                                     | J    | Y to Bus           | Х               | 1              | 0           | 1           | 1           | 1  |  |  |

|                                                |      | Status to Bus      | Х               | 1              | 1           | 1           | 1           | 1  |  |  |

|                                                | 1    | Load X from Bus    | 1               | 0              | 0           | 0           | 1           | 1  |  |  |

| Increment Sequence<br>Counter                  | }    | Load Z from Bus    | 1               | 0              | 1           | 0           | 1           | 1  |  |  |

|                                                | J    | Load Y from Bus    | 1               | 0              | 0           | 1           | 1           | 1  |  |  |

|                                                | ter  | Load Control Regis | 1               | 0              | 1           | 1           | 1           | 1  |  |  |

|                                                | ats) | No Action (Bus Flo | 0               | 0              | Х           | Х           | 1           | 1  |  |  |

NOTE:

1. () = 1800 System Signals. 1 = High Level, 0 = Low Level, X = High or Low Level.

CONTROL TRUTH TABLE

#### STATUS REGISTER

|        |   | STATUS BYTE |   |   |   |   |   |      |

|--------|---|-------------|---|---|---|---|---|------|

| BIT    | 7 | 6           | 5 | 4 | 3 | 2 | 1 | 0    |

| OUTPUT | 0 | 0           | 0 | 0 | 0 | 0 | 0 | 0.F. |

NOTES:

1. O.F. = 1 if overflow (only valid after a divide has been done)

2. Bits 1 - 7 are read as 0 always.

## DELAY NEEDED WITH AND WITHOUT PRESCALER

8N + 1 Shifts/Operation at 1 Clock Cycle/Shift N = Number of MDU's, S = Shift Rate

|              | WITHOUT P                | RESCALER                             | WITH PRESCALER               |                                      |            |  |

|--------------|--------------------------|--------------------------------------|------------------------------|--------------------------------------|------------|--|

| NO. OF MDU's | SHIFTS = 8N +1<br>NEEDED | (NOTE 1)<br>MACHINE CYCLES<br>NEEDED | SHIFTS = S (8N +1)<br>NEEDED | (NOTE 1)<br>MACHINE CYCLES<br>NEEDED | SHIFT RATE |  |

| 1            | 9                        | 2 (1 NOP)                            | 18                           | 3 (1 NOP)                            | 2          |  |

| 2            | 17                       | 2 (1 NOP)                            | 68                           | 9 (3 NOPs)                           | 4          |  |

| 3            | 25                       | 3 (1 NOP)                            | 200                          | 25 (9 NOPs)                          | 8          |  |

| 4            | 33                       | 4 (2 NOPs)                           | 264                          | 33 (11 NOPs)                         | 8          |  |

NOTE:

1. NOP instruction is shown for machine cycles needed (3/NOP). Other instructions may be used.

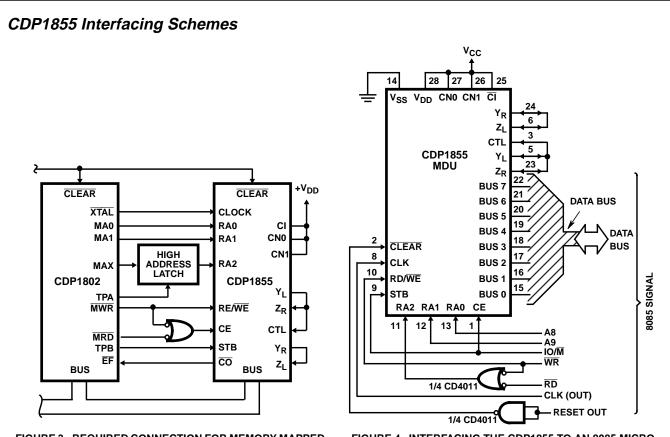

FIGURE 3. REQUIRED CONNECTION FOR MEMORY MAPPED ADDRESSING OF THE MDU

FIGURE 4. INTERFACING THE CDP1855 TO AN 8085 MICRO-PROCESSOR AS AN I/O DEVICE

# Programming Example for Multiplication

For a 24-bit x 24-bit multiply using the system shown in Figure 5, the following is an assembly listing of a program to multiply  $201F7C_{16}$  by  $723C09_{16}$ :

| MEMORY<br>LOCATION | OP<br>CODE | LINE<br>NO. | ASSEMBLY LANGUAGE                     |

|--------------------|------------|-------------|---------------------------------------|

| 0000               | F830;      | 0001        | LDI 030H                              |

| 0002               | A2;        | 0002        | PLO R2 LOAD 30 INTO R2.0              |

| 0003               | F800;      | 0003        | LDI 00H                               |

| 0005               | B2;        | 0004        | PHI R2 LOAD 00 INTO R2.1 (R2=0030)    |

| 0006               | 6758;      | 0005        | OUT 7; DC 058H LOAD CONTROL REGISTERS |

| 0008               | •          | 0006        | SPECIFYING THREE MDU's                |

| 0008               | -          | 0007        | RESET THE Y REGISTER AND              |

| 0008               | -          | 0008        | SEQUENCE COUNTER                      |

| 0008               | 6420;      | 0009        | OUT 4; DC 020H LOAD MSB OF X REGISTER |

| 000A               | -          | 0010        | WITH 20                               |

| 000A               | 641F;      | 0011        | OUT 4; DC 01FH LOAD NEXT MSB OF X REG |

| 000C               | -          | 0012        | WITH 1F                               |

| 000C               | 647C;      | 0013        | OUT 4; DC 07CH LOAD LSB OF X REGISTER |

| 000E               |            | 0014        | WITH 7C                               |

| 000E               | 6572;      | 0015        | OUT 5; DC 072H LOAD MSB OF Z REGISTER |

| 0010               | ;          | 0016        | WITH 72                               |

# Programming Example for Multiplication

For a 24-bit x 24-bit multiply using the system shown in Figure 5, the following is an assembly listing of a program to multiply  $201F7C_{16}$  by  $723C09_{16}$ : (Continued)

| MEMORY<br>LOCATION | OP<br>CODE   | LINE<br>NO. | ASSEMBLY LANGUAGE                     |

|--------------------|--------------|-------------|---------------------------------------|

| 0010               | 653C;        | 0017        | OUT 5; DC 030H LOAD NEXT MSB OF Z REG |

| 0012               | ;            | 0018        | WITH 3C                               |

| 0012               | 6509;        | 0019        | OUT 5; DC 09H LOAD LSB OF Z REGISTER  |

| 0014               | -            | 0020        | WITH 09                               |

| 0014               | 6759;        | 0021        | OUT 7; DC 059H LOAD CONTROL REGISTERS |

| 0016               | -            | 0022        | RESETTING Y REGISTERS                 |

| 0016               | <del>,</del> | 0023        | AND SEQUENCE COUNTERS                 |

| 0016               | -            | 0024        | AND STARTING MULTIPLY                 |

| 0016               | -            | 0025        | OPERATION                             |

| DELAY FOR MULTIPI  | _Y TO FINISH |             |                                       |

| 0016               | E2;          | 0026        | SEX R2                                |

| 0017               | 6E60;        | 0027        | INP 6; IRX MSB OF RESULTS IS STORED   |

| 0019               | •            | 0028        | AT LOCATION 0030                      |

| 0019               | 6E60;        | 0029        | INP 6; IRX                            |

| 001B               | 6E60;        | 0030        | INP 6; IRX                            |

| 001D               | 6D60;        | 0031        | INP 5; IRX                            |

| 001F               | 6D60;        | 0032        | INP 5; IRX                            |

| 0021               | 6D;          | 0033        | INP 5 COMPLETE LOADING RESULT         |

| 0022               | •            | 0034        | INTO MEMORY LOCATIONS                 |

| 0022               | •            | 0035        | 0030 TO 0035                          |

| 0022               | •            | 0036        | RESULTS = 0E558DBA2B5C                |

| 0022               | 3022;        | 0037 STOP   | BR STOP                               |

| 0024               | ;            | 0038        | END                                   |

| 0000               |              |             |                                       |

The result of  $201F7C_{16} \times 723C09_{16}$  is  $0E558DBA2B5C = E_{15760612797276_{10}}$ . It will be stored in memory as follows:

| ▫ |    | $\mathbf{n}$ | MU   | пт | וסו | v   |

|---|----|--------------|------|----|-----|-----|

|   | БГ | υr           | IVIU |    | 1 . | - 1 |

|   |    |              |      |    |     |     |

| LOC  | ВҮТЕ |

|------|------|

| 0030 | 0E   |

| 31   | 55   |

| 32   | 8D   |

| 33   | ВА   |

| 34   | 2B   |

| 35   | 5C   |

| REGISTER X |

|------------|

| REGISTER Y |

| REGISTER Z |

|            |

AFTER MULTIPLY

REGISTER X REGISTER Y REGISTER Z

| MDU1 | MDU2 | MDU3 |

|------|------|------|

| 20   | 1F   | 7C   |

| 00   | 00   | 00   |

| 72   | 3C   | 09   |

| MDU1 | MDU2 | MDU3 |

|------|------|------|

| 20   | 1F   | 7C   |

| 0E   | 55   | 8D   |

| BA   | 2B   | 5C   |

# Programming Example for Division

| MEMORY<br>OCATION | OP<br>CODE | LINE<br>NO. | ASSEMBLY LANGUAGE          |                                          |  |  |  |  |

|-------------------|------------|-------------|----------------------------|------------------------------------------|--|--|--|--|

| 0000              | ,          | 0001        | Program example for a 16   | -bit by 8-bit divide using 1 CDP1855 MDU |  |  |  |  |

| 0000              | ;          | 0002        | Gives a 16-bit answer with | n 8-bit remainder                        |  |  |  |  |

| 0000              | ;          | 0003        |                            |                                          |  |  |  |  |

| 0000              | 68C22000;  | 0004        | RLDI R2, 2000H             | Answer is stored at 2000 hex             |  |  |  |  |

| 0004              | ;          | 0005        |                            | Register 2 points to it                  |  |  |  |  |

| 0004              | 68C33000;  | 0006        | RLDI R3, 3000H             | Dividend is stored at 3000 hex           |  |  |  |  |

| 0008              | ;          | 0007        |                            | Register 3 points to it                  |  |  |  |  |

| 0008              | 68C44000;  | 8000        | RLDI R4, 4000H             | Divisor is stored at 4000 hex            |  |  |  |  |

| 000C              | ;          | 0009        |                            | Register 4 points to it                  |  |  |  |  |

| 000C              | ;          | 0010        |                            |                                          |  |  |  |  |

| 000C              | E067F0;    | 0011        | SEX R4; OUT 7; DC OF0H     | Write to the control register to use     |  |  |  |  |

| 000F              | ;          | 0012        |                            | clock/2; 1MDU; reset sequence            |  |  |  |  |

| 000F              | ;          | 0013        |                            | counter; and no operation                |  |  |  |  |

| 000F              | ;          | 0014        |                            |                                          |  |  |  |  |

| 000F              | E464;      | 0015        | SEX R4; OUT 4              | Load the divisor into the X register     |  |  |  |  |

| 0011              | ;          | 0016        |                            |                                          |  |  |  |  |

| 0011              | E06600;    | 0017        | SEX R0; OUT 6; DC 0        | Load 0 into the Y register               |  |  |  |  |

| 0014              | E365;      | 0018        | SEX R3; OUT 5              | Load the most significant 8 bits of      |  |  |  |  |

| 0016              | ;          | 0019        |                            | the dividend into the Z register         |  |  |  |  |

| 0016              | ;          | 0020        |                            |                                          |  |  |  |  |

| 0016              | E067F2;    | 0021        | SEX R0; OUT 7; DC 0F2H     | Do the first divide, also resets the     |  |  |  |  |

| 0019              | ;          | 0022        |                            | sequence counter                         |  |  |  |  |

| 0019              | -<br>,     | 0023        |                            |                                          |  |  |  |  |

| 0019              | E26D60;    | 0024        | SEX R2; INP 5; IRX         | Read and store the most significant      |  |  |  |  |

| 001C              | ;          | 0025        |                            | 8 bits of the answer at 2000 hex         |  |  |  |  |

| 001C              | -<br>,     | 0026        |                            |                                          |  |  |  |  |

| 001C              | E067F0;    | 0027        | SEX R0; OUT 7; DC 0F0H     | Reset the sequence counter               |  |  |  |  |

| 001F              | -<br>,     | 0028        |                            |                                          |  |  |  |  |

| 001F              | E365;      | 0029        | SEX R3; OUT 5              | Load the 8 least significant 8 bits      |  |  |  |  |

| 0021              | -          | 0030        |                            | of the original dividend into the Z      |  |  |  |  |

| 0021              | ;          | 0031        |                            | register                                 |  |  |  |  |

| 0021              | ;          | 0032        |                            |                                          |  |  |  |  |

| 0021              | E067F2;    | 0033        | SEX R0; OUT 7; DC 0F2H     | Do the second division                   |  |  |  |  |

| 0024              | -          | 0034        |                            |                                          |  |  |  |  |

| 0024              | E26D60;    | 0035        | SEX R2; INP 5; IRX         | Read and store the least significant     |  |  |  |  |

| 0027              | ;          | 0036        |                            | 8 bits of the answer at 2001 hex         |  |  |  |  |

| 0027              | 6E;        | 0037        | INP 6                      | Read and store the remainder at 2002     |  |  |  |  |

| 0028              | ;          | 0038        |                            | hex                                      |  |  |  |  |

| 0000              |            |             |                            |                                          |  |  |  |  |

For the divide operation (Figure 5), the formula is:

|                              |                                      |                        | LIMITS |                 |     |     |                 |     |       |

|------------------------------|--------------------------------------|------------------------|--------|-----------------|-----|-----|-----------------|-----|-------|

|                              |                                      |                        |        | CDP1855         |     |     | CDP1855C        |     | 1     |

| (NOTE 1)<br>PARAMETER        |                                      | V <sub>DD</sub><br>(V) | MIN    | (NOTE 2)<br>TYP | MAX | MIN | (NOTE 2)<br>TYP | МАХ | UNITS |

| OPERATION TIMING             |                                      |                        |        | -               |     |     |                 |     | -     |

| Maximum Clock Frequency      |                                      | 5                      | 3.2    | 4               | -   | 3.2 | 4               | -   | MHz   |

| (Note 3)                     |                                      | 10                     | 6.4    | 8               | -   | -   | -               | -   | MHz   |

| Maximum Shift Frequency      |                                      | 5                      | 1.6    | 2               | -   | 1.6 | 2               | -   | MHz   |

| (1 Device) (Note 4)          |                                      | 10                     | 3.2    | 4               | -   | -   | -               | -   | MHz   |

| Minimum Clock Width          | t <sub>CLK0</sub>                    | 5                      | -      | 100             | 150 | -   | 100             | 150 | ns    |

|                              | <sup>t</sup> CLK1                    | 10                     | -      | 50              | 75  | -   | -               | -   | ns    |

| Minimum Clock Period         | t <sub>CLK</sub>                     | 5                      | -      | 250             | 312 | -   | 250             | 312 | ns    |

|                              |                                      | 10                     | -      | 125             | 156 | -   | -               | -   | ns    |

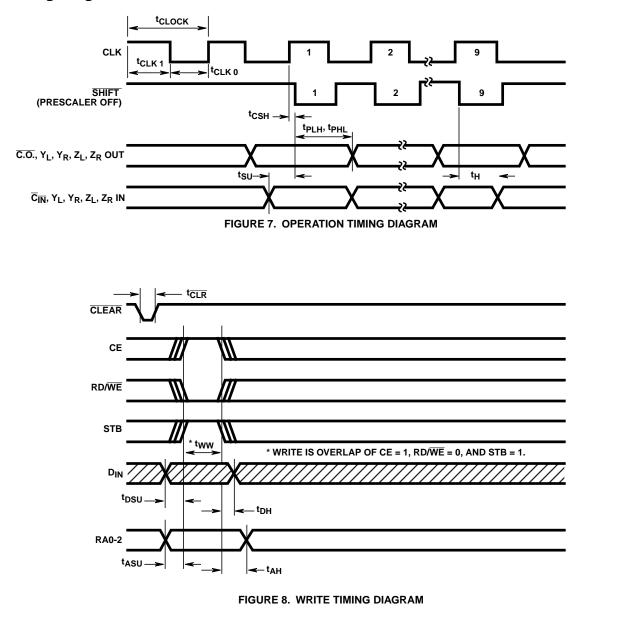

| Clock to Shift Propagation   | t <sub>CSH</sub>                     | 5                      | -      | 200             | 300 | -   | 200             | 300 | ns    |

| Delay                        |                                      | 10                     | -      | 100             | 150 | -   | -               | -   | ns    |

| Minimum C.I. to Shift Setup  | ts∪                                  | 5                      | -      | 50              | 67  | -   | 50              | 67  | ns    |

|                              |                                      | 10                     | -      | 25              | 33  | -   | -               | -   | ns    |

| C.O. from Shift Propagation  | t <sub>PLH</sub><br>t <sub>PHL</sub> | 5                      | -      | 450             | 600 | -   | 450             | 600 | ns    |

| Delay                        |                                      | 10                     | -      | 225             | 300 | -   | -               | -   | ns    |

| Minimum C.I. from Shift Hold | t <sub>H</sub>                       | 5                      | -      | 50              | 75  | -   | 50              | 75  | ns    |

|                              |                                      | 10                     | -      | 25              | 40  | -   | -               | -   | ns    |

| Minimum Register Input       | t <sub>SU</sub>                      | 5                      | -      | -20             | 10  | -   | -20             | 10  | ns    |

| Setup                        |                                      | 10                     | -      | -10             | 10  | -   | -               | -   | ns    |

| Register after Shift Delay   | t <sub>PLH</sub>                     | 5                      | -      | 400             | 600 | -   | 400             | 600 | ns    |

|                              | <sup>t</sup> PHL                     | 10                     | -      | 200             | 300 | -   | -               | -   | ns    |

| Minimum Register after Shift | t <sub>Н</sub>                       | 5                      | -      | 50              | 100 | -   | 50              | 100 | ns    |

| Hold                         |                                      | 10                     | -      | 25              | 50  | -   | -               | -   | ns    |

| C.O. from C.I. Propagation   | t <sub>PLH</sub>                     | 5                      | -      | 100             | 150 | -   | 100             | 150 | ns    |

| Delay                        | <sup>t</sup> PHL                     | 10                     | -      | 50              | 75  | -   | -               | -   | ns    |

| Register from C.I.           | t <sub>PLH</sub>                     | 5                      | -      | 80              | 120 | -   | 80              | 120 | ns    |

| Propagation Delay            | t <sub>PHL</sub>                     | 10                     | -      | 40              | 60  | -   | -               | -   | ns    |

NOTES:

1. Maximum limits of minimum characteristics are the values above which all devices function.

2. Typical values are for  $T_A = 25^{\circ}C$  and nominal voltages.

3. Clock frequency and pulse width are given for systems using the internal clock option of the CDP1855. Clock frequency equals shift frequency for systems not using the internal clock option.

4. Shift period for cascading of devices is increased by an amount equal to the  $\overline{C.I.}$  to  $\overline{C.O.}$  Propagation Delay for each device added.

# Dynamic Electrical Specifications At $T_A = -40$ to +85°C, $V_{DD} \pm 5\%$ , $t_R$ , $t_F = 20$ ns, $V_{IH} = 0.7V_{DD}$ , $V_{IL} = 0.3V_{DD}$ , $C_L = 100$ pF (See Figure 8)

|                           |                        |     |                 | LIMITS  |     |                 |     |       |    |  |

|---------------------------|------------------------|-----|-----------------|---------|-----|-----------------|-----|-------|----|--|

|                           |                        |     |                 | CDP1855 |     | CDP1855C        |     |       | 1  |  |

| (NOTE 1)<br>PARAMETER     | V <sub>DD</sub><br>(V) | MIN | (NOTE 2)<br>TYP | МАХ     | MIN | (NOTE 2)<br>TYP | МАХ | UNITS |    |  |

| WRITE CYCLE               |                        |     |                 |         |     | 2               |     |       | -  |  |

| Minimum Clear Pulse Width | tCLR                   | 5   | -               | 50      | 75  | -               | 50  | 75    | ns |  |

|                           |                        | 10  | -               | 25      | 40  | -               | -   | -     | ns |  |

| Minimum Write Pulse Width | t <sub>WW</sub>        | 5   | -               | 150     | 225 | -               | 150 | 225   | ns |  |

|                           |                        | 10  | -               | 75      | 115 | -               | -   | -     | ns |  |

| Minimum Data-In-Setup     | t <sub>DSU</sub>       | 5   | -               | -75     | 0   | -               | -75 | 0     | ns |  |

|                           |                        | 10  | -               | -40     | 0   | -               | -   | -     | ns |  |

| Minimum Data-In-Hold      | <sup>t</sup> DH        | 5   | -               | 50      | 75  | -               | 50  | 75    | ns |  |

|                           |                        | 10  | -               | 25      | 40  | -               | -   | -     | ns |  |

| Minimum Address to Write  | t <sub>ASU</sub>       | 5   | -               | 50      | 75  | -               | 50  | 75    | ns |  |

| Setup                     |                        | 10  | -               | 25      | 40  | -               | -   | -     | ns |  |

| Minimum Address after     | t <sub>AH</sub>        | 5   | -               | 50      | 75  | -               | 50  | 75    | ns |  |

| Write Hold                |                        | 10  | -               | 25      | 40  | -               | -   | -     | ns |  |

# NOTES:

1. Maximum limits of minimum characteristics are the values above which all devices function.

2. Typical values are for  $T_A = 25^{\circ}C$  and nominal voltages.

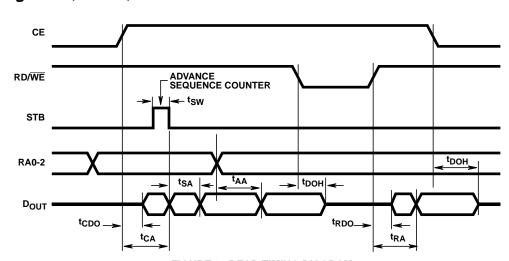

Dynamic Electrical Specifications At  $T_A = -40$  to  $+85^{\circ}$ C,  $V_{DD} \pm 5\%$ ,  $t_R$ ,  $t_F = 20$ ns,  $V_{IH} = 0.7 V_{DD}$ ,  $V_{IL} = 0.3 V_{DD}$ ,  $C_L = 100$ pF (See Figure 9)

|                          |                  |                        |     |                 | LIN | IITS |                 |     |       |

|--------------------------|------------------|------------------------|-----|-----------------|-----|------|-----------------|-----|-------|

|                          |                  |                        |     | CDP1855         |     |      | CDP1855C        |     | 1     |

| (NOTE 1)<br>PARAMETER    |                  | V <sub>DD</sub><br>(V) | MIN | (NOTE 2)<br>TYP | МАХ | MIN  | (NOTE 2)<br>TYP | МАХ | UNITS |

| READ CYCLE               |                  |                        |     |                 |     |      |                 |     | -     |

| CE to Data Out Active    | t <sub>CDO</sub> | 5                      | -   | 200             | 300 | -    | 200             | 300 | ns    |

|                          |                  | 10                     | -   | 100             | 150 | -    | -               | -   | ns    |

| CE to Data Access        | t <sub>CA</sub>  | 5                      | -   | 300             | 450 | -    | 300             | 450 | ns    |

|                          |                  | 10                     | -   | 150             | 225 | -    | -               | -   | ns    |

| Address to Data Access   | t <sub>AA</sub>  | 5                      | -   | 300             | 450 | -    | 300             | 450 | ns    |

|                          |                  | 10                     | -   | 150             | 225 | -    | -               | -   | ns    |

| Data Out Hold after CE   | t <sub>DOH</sub> | 5                      | 50  | 150             | 225 | 50   | 150             | 225 | ns    |

|                          |                  | 10                     | 25  | 75              | 115 | -    | -               | -   | ns    |

| Data Out Hold after Read | t <sub>DOH</sub> | 5                      | 50  | 150             | 225 | 50   | 150             | 225 | ns    |

|                          |                  | 10                     | 25  | 75              | 115 | -    | -               | -   | ns    |

| Read to Data Out Active  | t <sub>RDO</sub> | 5                      | -   | 200             | 300 | -    | 200             | 300 | ns    |

|                          |                  | 10                     | -   | 100             | 150 | -    | -               | -   | ns    |

| Read to Data Access      | t <sub>RA</sub>  | 5                      | -   | 200             | 300 | -    | 200             | 300 | ns    |

|                          |                  | 10                     | -   | 100             | 150 | -    | -               | -   | ns    |

| Dynamic Electrical Spe |                 |                        | = -40 to +85<br>gure 9) <b>(Co</b> |                 | , t <sub>R</sub> , t <sub>F</sub> = 20 | ns, V <sub>IH</sub> = 0.7 | 7V <sub>DD</sub> , V <sub>IL</sub> = 0. | .3V <sub>DD</sub> , |       |  |

|------------------------|-----------------|------------------------|------------------------------------|-----------------|----------------------------------------|---------------------------|-----------------------------------------|---------------------|-------|--|

|                        |                 |                        |                                    |                 | LIM                                    | IITS                      |                                         |                     |       |  |

|                        |                 |                        |                                    | CDP1855         |                                        |                           | CDP1855C                                |                     | 1     |  |

| (NOTE 1)<br>PARAMETER  |                 | V <sub>DD</sub><br>(V) | MIN                                | (NOTE 2)<br>TYP | MAX                                    | MIN                       | (NOTE 2)<br>TYP                         | МАХ                 | UNITS |  |

| Strobe to Data Access  | t <sub>SA</sub> | 5                      | 50                                 | 200             | 300                                    | 50                        | 200                                     | 300                 | ns    |  |

|                        |                 | 10                     | 25                                 | 100             | 150                                    | -                         | -                                       | -                   | ns    |  |

| Minimum Strobe Width   | <sup>t</sup> sw | 5                      | -                                  | 150             | 225                                    | -                         | 150                                     | 225                 | ns    |  |

|                        |                 | 10                     | -                                  | 75              | 115                                    | -                         | -                                       | -                   | ns    |  |

# NOTES:

1. Maximum limits of minimum characteristics are the values above which all devices function.

2. Typical values are for  $T_{A}$  = 25  $^{0}C$  and nominal voltages.

# **Timing Diagrams**

FIGURE 9. READ TIMING DIAGRAM

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

# Sales Office Headquarters

# NORTH AMERICA

Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (407) 724-7000 FAX: (407) 724-7240

#### EUROPE

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

#### ASIA

Intersil (Taiwan) Ltd. Taiwan Limited 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029