a leap ahead

**DataSheet**

**austriamicro**systems

## AS1326 High Current, 0.8A DC-DC Step-Up Converters

# **1** General Description

The AS1326A/AS1326B are high-efficiency, high current, DC-DC step-up converters specifically designed for battery-powered wireless applications. Low quiescent supply current ( $65\mu A$ ), high operating frequency (1MHz), and minimal external component requirements make these devices perfect for small hand-held applications.

Table 1. Standard Products

| Model   | Input Signal Activation |

|---------|-------------------------|

| AS1326A | Logic-Low On            |

| AS1326B | Logic-High On           |

Both devices use synchronous-rectified pulse-width modulation (PWM) boost technology to generate 2.5 to 5.0V outputs from a wide range of inputs, such as 1 to 3 alkaline/NiCd/NiMH cells or a single lithium-ion (Li+) cell. Automatic powersave operation significantly improves efficiency at light-loads.

Continuous switching mode is available for applications requiring constant-frequency operation at all load currents. PWM operation can also be synchronized to an external clock to protect sensitive frequency bands in communications equipment.

Analog soft-start and adjustable current limit permit optimization of rush in current and external component size.

The AS1326A/AS1326B are available in a 10-pin TDFN (3.0mm x 3.0mm) package.

## 2 Key Features

- Up to 800mA Output

- Constant-Frequency (1MHz) Operation

- Up to 96% Efficiency

- Input Range: 0.7 to 5.0V

- Fixed Output: 3.3V

- Adjustable Output: 2.5 to 5.0V

- PWM Synchronous-Rectified Technology

- Logic-Controlled Shutdown: 0.1µA

- Synchronizable Switching Frequency (0.5 to 1.2MHz)

- Adjustable Current Limit

- Adjustable Soft-Start

- 10-pin TDFN (3.0mm x 3.0mm) Package

## **3** Applications

The devices are ideal for digital cordless phones. mobile phones, wireless handsets, hand-held instruments, PDAs, two-way pagers, and any battery-operated equipment.

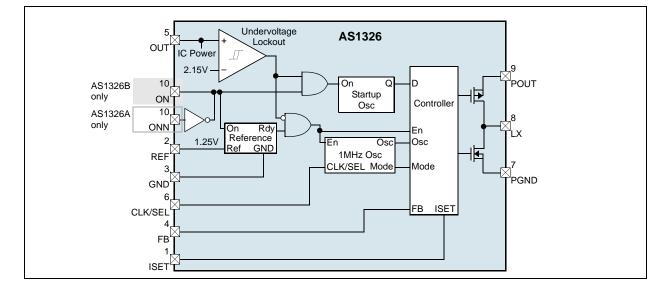

Figure 1. Block Diagram

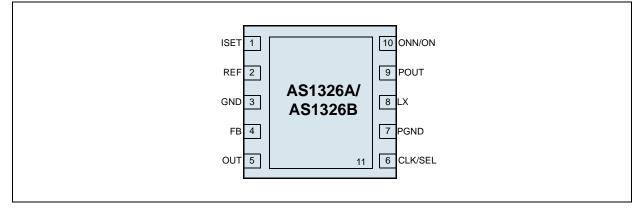

# 4 Pinout

## **Pin Assignments**

Figure 2. Pin Assignments (Top View)

## **Pin Descriptions**

Table 2. Pin Descriptions

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

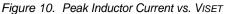

| 1          | ISET     | <b>N-Channel Current-Limit Control.</b> For maximum current limit, connect to pin REF. To reduce current, supply a voltage between pin REF and GND using a resistive voltage-divider. If soft-start is desired, connect a capacitor from this pin to GND.                                                                                                                                                                                                                                                 |

| 2          | REF      | <b>1.250V Internal Reference Bypass.</b> Connect a 10nF ceramic bypass capacitor to GND. Up to 50µA of external load current is allowed.                                                                                                                                                                                                                                                                                                                                                                  |

| 3          | GND      | <b>Ground.</b> Connect this pin to PGND using a short trace. The exposed pad can be used for this routing.                                                                                                                                                                                                                                                                                                                                                                                                |

| 4          | FB       | <b>DC-DC Converter Feedback Input.</b> To set fixed output voltage of +3.3V, connect this pin to GND. For adjustable output of 2.5 to 5.0V, connect to a resistor-divider network from pin OUT to GND. The set point for this pin is 1.24V.                                                                                                                                                                                                                                                               |

| 5          | OUT      | IC Power, Supplied from the Output. Bypass this pin to GND with a 330nF ceramic capacitor, and connect to POUT with a $10\Omega$ series resistor (see Figure 19 on page 11).                                                                                                                                                                                                                                                                                                                              |

| 6          | CLK/SEL  | <ul> <li>Clock Input for the DC-DC Converter. This pin is also used to program the operational mode as follows:</li> <li>0 = Normal operation – the AS1326A operates at a fixed frequency, and switches into automatic powersave operation if the load is minimized.</li> <li>1 = Forced-PWM mode – the AS1326A operates in low-noise, constant-frequency mode at all loads.</li> <li>Clocked = Forced-PWM mode with the internal oscillator synchronized to this pin in 500 to 1200kHz range.</li> </ul> |

| 7          | PGND     | N-Channel Power MOSFET Switch Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8          | LX       | Inductor Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9          | POUT     | Power Output. P-channel synchronous rectifier source.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10         | ONN      | Enable Low (AS1326A only). Must be connected to GND for normal operation.<br>0 = The AS1326A is on.<br>1 = The AS1326A is off.                                                                                                                                                                                                                                                                                                                                                                            |

|            | ON       | Enable High (AS1326B only). Must be connected to OUT for normal operation.<br>0 = The AS1326B is off.<br>1 = The AS1326B is on.                                                                                                                                                                                                                                                                                                                                                                           |

| 11         | NC       | <b>Exposed Pad.</b> This pad is not connected internally. It can be used for ground connection between GND and PGND.                                                                                                                                                                                                                                                                                                                                                                                      |

# **5** Absolute Maximum Ratings

Stresses beyond those listed in Table 3 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 4 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Table 3. Absolute Maximum Ratings | Table 3. | Absolute | Maximum | Ratings |

|-----------------------------------|----------|----------|---------|---------|

|-----------------------------------|----------|----------|---------|---------|

| Parameter                    | Min  | Max            | Units | Comments                                                                                                                                                                                                                                                                                             |

|------------------------------|------|----------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ON, ONN, OUT, CLK/SEL to GND | -0.3 | 7              | V     |                                                                                                                                                                                                                                                                                                      |

| PGND to GND                  | -0.3 | +0.3           | V     |                                                                                                                                                                                                                                                                                                      |

| REF, FB, ISET, POUT to GND   | -0.3 | Vout +<br>0.3  | V     |                                                                                                                                                                                                                                                                                                      |

| LX to PGND                   | -0.3 | VPOUT +<br>0.3 | V     |                                                                                                                                                                                                                                                                                                      |

| POUT to OUT                  | -0.3 | +0.3           | V     |                                                                                                                                                                                                                                                                                                      |

| Thermal Resistance OJA       |      | 33             | °C/W  | on PCB                                                                                                                                                                                                                                                                                               |

| Operating Temperature Range  | -40  | +85            | °C    |                                                                                                                                                                                                                                                                                                      |

| Storage Temperature Range    | -65  | +150           | °C    |                                                                                                                                                                                                                                                                                                      |

| Junction Temperature         |      | +150           | °C    |                                                                                                                                                                                                                                                                                                      |

| Package Body Temperature     |      | +260           | ٥C    | The reflow peak soldering temperature (body<br>temperature) specified is in accordance with<br>IPC/JEDEC J-STD-020C "Moisture/Reflow<br>Sensitivity Classification for Non-Hermetic Solid<br>State Surface Mount Devices".<br>The lead finish for Pb-free leaded packages is<br>matte tin (100% Sn). |

# 6 Electrical Characteristics

CLK/SEL = FB = PGND = GND, ISET = REF, OUT = POUT, VOUT = 3.6V, TAMB = -40 to  $+85^{\circ}C$ . Typical values are at  $TAMB = +25^{\circ}C$ . Unless otherwise specified.

Table 4. Electrical Characteristics

| Symbol    | Parameter                                                | Condition                                                                              | Min   | Тур   | Max   | Unit     |

|-----------|----------------------------------------------------------|----------------------------------------------------------------------------------------|-------|-------|-------|----------|

| DC-DC C   | Converter                                                |                                                                                        |       |       |       |          |

| Vin       | Input Voltage Range <sup>1</sup>                         |                                                                                        |       | 0.7   | 5.0   | V        |

| VMINSU    | Minimum Startup Voltage <sup>2</sup>                     | Iload < 1mA, Tamb = +25°C                                                              |       | 0.9   | 1.1   | V        |

|           | Temperature Coefficient of<br>Startup Voltage            |                                                                                        |       | -1.6  |       | mV/°C    |

| fsu       | Frequency in Startup Mode                                | Vout = 1.5V                                                                            | 125   | 500   | 1000  | kHz      |

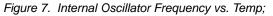

| fsw       | Internal Oscillator Frequency                            | CLK/SEL = OUT                                                                          | 0.8   | 1     | 1.2   | MHz      |

|           | Oscillator Maximum<br>Duty Cycle <sup>3</sup>            |                                                                                        | 80    | 86    | 90    | %        |

| fSWEXT    | External Clock<br>Frequency Range                        |                                                                                        | 0.5   |       | 1.2   | MHz      |

| Vout      | Output Voltage                                           | VFB < 0.1V, CLK/SEL = OUT, includes load<br>regulation for 0 < ILX < 0.55A             | 3.17  | 3.3   | 3.38  | V        |

| Vfb       | FB Regulation Voltage                                    | Adjustable output, CLK/SEL = OUT, includes load regulation for $0 < I \perp X < 0.55A$ | 1.215 | 1.240 | 1.270 | V        |

| lfв       | FB Input Leakage Current                                 | Vfb = 1.35V, Tamb = +25°C                                                              | -100  | 0.01  | 100   | nA       |

|           | Load Regulation                                          | CLK/SEL = OUT, no load to full load,<br>0 < ILX < 1.0A                                 |       | -1    |       | %        |

| Voutadj   | Output Voltage<br>Adjust Range                           |                                                                                        | 2.5   |       | 5.0   | V        |

|           | Output Voltage<br>Lockout Threshold <sup>4</sup>         | Rising edge                                                                            | 2.00  | 2.15  | 2.30  | V        |

|           | ISET Input Leakage Current                               | VISET = 1.25V, TAMB = +25°C                                                            | -50   | 0.01  | 50    | nA       |

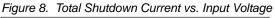

| ISHDN     | Supply Current in Shutdown                               | Von = 0V, Vonn = 3.6V                                                                  |       | 0.1   | 5     | μA       |

|           | No-Load Supply Current <sup>5</sup>                      | CLK/SEL = GND                                                                          |       | 65    | 100   | μA       |

|           | No-Load Supply Current <sup>5</sup> ,<br>Forced PWM Mode | CLK/SEL = OUT                                                                          |       | 2     |       | mA       |

| DC-DC S   | witches                                                  |                                                                                        |       |       |       | <u>.</u> |

|           | POUT Leakage Current                                     | VLX = 0, VOUT = 5.5V, TAMB = +25°C                                                     |       | 0.1   | 10    | μA       |

|           | LX Leakage Current                                       | $V_{LX} = V_{OUT} = 5.5V$ , in shutdown,<br>TAMB = +25°C                               |       | 0.1   | 10    | μA       |

| Ron       | Switch On-Resistance                                     | N-channel                                                                              |       | 0.2   | 0.35  | 0        |

| KON       | Switch On-Resistance                                     | P-channel                                                                              |       | 0.25  | 0.45  | Ω        |

| INMOS     | N-Channel Current Limit                                  |                                                                                        | 1.25  | 1.6   | 1.95  | А        |

| Reference | ces                                                      |                                                                                        |       |       |       |          |

| Vref      | Reference Output Voltage                                 | IREF = 0                                                                               | 1.230 | 1.250 | 1.270 | V        |

|           | Reference Load Regulation                                | -1μΑ < IREF < +50μΑ                                                                    |       | 5     | 15    | mV       |

|           | Reference Supply Rejection                               | 2.5V < VOUT < 5V                                                                       |       | 0.2   | 6     | mV       |

| Symbol   | Parameter                             | Condition                       | Min           | Тур | Max           | Unit |  |

|----------|---------------------------------------|---------------------------------|---------------|-----|---------------|------|--|

| Logic In |                                       |                                 |               |     |               |      |  |

|          | CLK/SEL Input Low Level               | $2.5V \le V\text{OUT} \le 5.0V$ |               |     | 0.2 x<br>Vouт | V    |  |

|          | CLK/SEL Input High Level              | $2.5V \le V\text{OUT} \le 5.0V$ | 0.8 x<br>Vout |     |               | V    |  |

|          | 6                                     | $1.1V \leq Vout \leq 1.8V$      |               |     | 0.2           | V    |  |

|          | ON, ONN Input Low Level <sup>6</sup>  | $1.8V \le Vout \le 5.0V$        |               |     | 0.4           | v    |  |

|          | ON, ONN Input High Level <sup>6</sup> | $1.1V \leq Vout \leq 1.8V$      | Vout -<br>0.2 |     |               | V    |  |

|          | e., epge.e.                           | $1.8V \leq Vout \leq 5.0V$      | 1.6           |     |               |      |  |

|          | Input Leakage Current                 | CLK/SEL, ON, ONN, TAMB = +25°C  |               | 0.1 | 1             | μA   |  |

|          | Minimum CLK/SEL<br>Pulse Width        |                                 |               | 200 |               | ns   |  |

|          | Maximum CLK/SEL<br>Rise/Fall Time     |                                 |               | 100 |               | ns   |  |

#### Table 4. Electrical Characteristics (Continued)

1. Operating voltage; since the regulator is bootstrapped to the output, once started, the AS1326 operates down to 0.7V input. If CLK/SEL = GND then VIN  $\leq$  VOUT. If CLK/SEL = VOUT then VIN  $\leq$  0.75xVOUT.

2. Startup is tested with the circuit shown in Figure 25 on page 14.

3. Defines maximum step-up ratio.

4. The regulator is in startup mode until this voltage is reached. **Caution**: Do not apply full load current until the device output > 2.3V.

5. Supply current into pin OUT. This current correlates directly to the actual battery-supply current, but is reduced in value according to the step-up ratio and efficiency.

6. ON and ONN have a hysteresis of typically 0.15V.

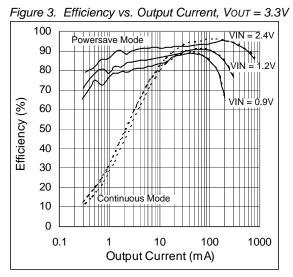

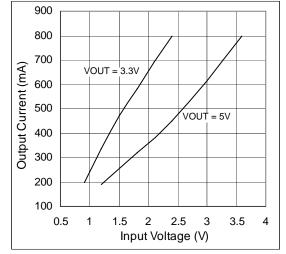

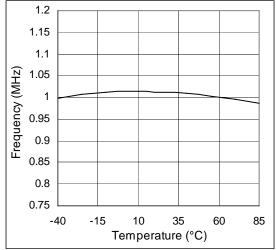

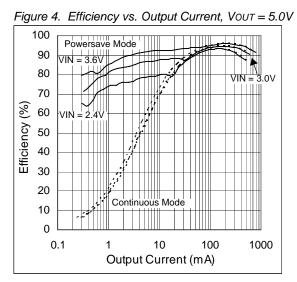

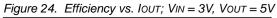

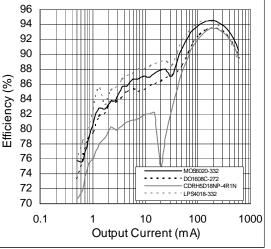

# **7** Typical Operating Characteristics

Circuit of Figure 19, VIN = 2.4V, VOUT = 3.3V, TA = +25°C, unless otherwise noted.

Figure 5. Maximum Output Current vs. Input Voltage;

Figure 6. No-Load Current vs. Input Voltage;

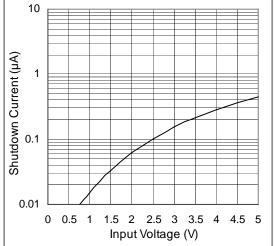

Figure 9. Startup Voltage vs. Output Current

Figure 11. Light-Load Switching Waveform IOUT = 10mA, CLK/SEL = OUT

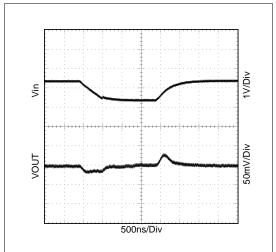

Figure 13. Line-Transient Response.  $V_{IN} = 2.4 \text{ to } 1.4V$ , IOUT = 200mA

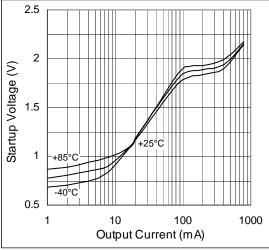

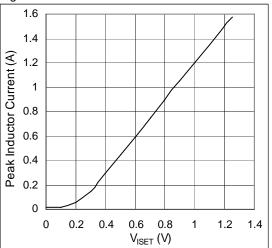

Figure 12. Heavy-Load Switching Waveform IOUT = 500mA

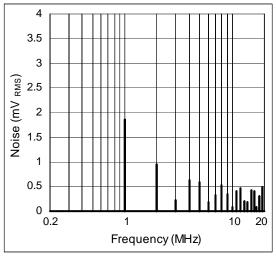

Figure 14. Noise Spectrum CLK/SEL = OUT

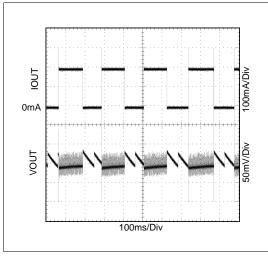

#### *Figure 15.* Load Transient Response; *Automatic Powersave Mode, CLK/SEL* = *GND*

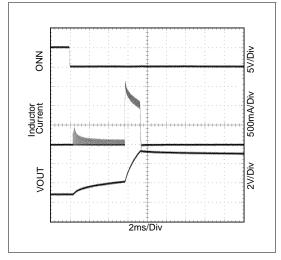

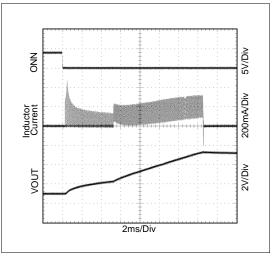

Figure 17. Turn-On Waveform No Soft Start

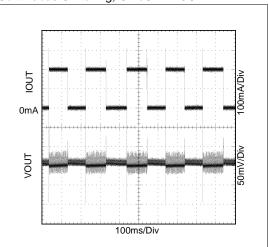

Figure 16. Load Transient Response Continuous Switching, CLK/SEL = OUT

Figure 18. Turn-On Waveform Soft Start, Rss =  $220k\Omega$  ,Css = 100nF

Parts used for measurments: 3.3µH (Coilcraft MOS6020-332ML) Inductor, 33µF (Panasonic EEFCD0K330R) CIN, 100µF (Panasonic EEFUD0J101R) COUT

# 8 Detailed Description

The AS1326A/AS1326B are high-efficiency, low-noise DC-DC boost converters suitable as power supplies for portable devices. Both devices feature integrated boost switching regulator, N-channel power MOSFET, P-channel synchronous rectifier, precision reference, and shutdown control circuitry (see Figure 1 on page 1).

The AS1326A/AS1326B are able to boost a 1- to 3-cell battery voltage input to a fixed 3.3V output, or adjustable output between 2.5 and 5.0V (an external Schottky diode is required for output voltages greater than 4V).

| # of NiCd/NiMh Cells | Input Voltage (V) | Output Voltage (V) | Output Current (mA) |

|----------------------|-------------------|--------------------|---------------------|

| 1                    | 1.2               | 3.3                | 335                 |

| 2                    | 2.4               | 3.3                | 800                 |

| Ζ                    | 2.4               | 5.0                | 450                 |

| 3                    | 3.6               | 5.0                | 800                 |

Table 5. Typical Output Voltages and Currents

The devices are guaranteed to startup with an input voltage as low as 1.1V and remain operational down to an input of as little as 0.7V, and are optimized for use in mobile phones and other RF applications which have low noise and low quiescent current (extended battery life) requirements.

The integrated shutdown circuitry reduces device quiescent current down to 0.1µA.

### Step-Up Converter

During boost operation, the internal N-channel MOSFET switch turns on for the first part of each cycle, allowing current to ramp up in the inductor and store energy in a magnetic field. During the second part of each cycle, the MOSFET turns off and inductor current flows through the synchronous rectifier to the output filter capacitor and the load. As the energy stored in the inductor is depleted, the current ramps down and the synchronous rectifier turns off.

At light loads, the device operates at fixed-frequency or only as needed to maintain regulation, depending on the setting of pin CLK/SEL (see Table 6).

### **Operational Modes**

The AS1326A/AS1326B are capable of operating in 3 different modes (see Table 6) as controlled by pin CLK/SEL (see page 2).

Table 6. Operational Modes

| CLK/SEL Setting                    | <b>Operational Mode</b> | Description                                                                     |

|------------------------------------|-------------------------|---------------------------------------------------------------------------------|

| 0                                  | Normal                  | High-efficiency at all loads; Fixed-frequency (1MHz) at heavy and medium loads. |

| 1                                  | Forced PWM              | Fixed-frequency (1MHz), low-noise at all loads. VIN $\leq 0.75 x \text{Vout}$   |

| External 500kHz to<br>1.2MHz clock | Synchronized PWM        | Fixed-frequency, low-noise at all loads. VIN $\leq 0.75 x \text{Vout}$          |

#### **Normal Operation**

When CLK/SEL is pulled low, the devices are in normal operating mode. In normal mode the devices operate in PWM when driving medium-to-heavy loads, and automatically switches to automatic powersave mode if the load requires less power. The use of automatic powersave mode will boost the efficiency furthermore at light-load conditions.

#### **Forced-PWM Operation**

Pulling CLK/SEL high, selects the low-noise PWM-only mode. During forced-PWM operation, the devices switch at a constant frequency (1MHz) and modulates the MOSFET switch pulse width to control the power transferred per cycle to regulate the output voltage. Switching harmonics generated by fixed-frequency operation are consistent and can be filtered. See the Noise Spectrum plot in the Typical Operating Characteristics (see Figure 14 on page 7).

#### Synchronized-PWM Operation

In PWM mode the AS1326A/AS1326B can be synchronized with an external clock (500kHz to 1.2MHz) by applying an external clock signal to pin CLK/SEL. This synchronization will minimize interference in wireless applications since the operating frequency can be set to a preferred value. The synchronous rectifier is active during synchronized-PWM operation.

### **Synchronous Rectifier**

The AS1326A/AS1326B feature an integrated, P-channel synchronous rectifier for enhanced efficiency operation. Synchronous rectification provides 5% improved efficiency over similar non-synchronous boost regulators.

In PWM mode, the synchronous rectifier is turned on during the second half of each switching cycle. In low-power mode, an internal comparator turns on the synchronous rectifier when the voltage at LX exceeds the boost regulator output.

**Note:** While operating with output voltages greater than 4V, an external 0.5A Schottky diode must be connected in parallel with the P-channel synchronous rectifier.

### Low-Voltage Startup Oscillator

The AS1326A/AS1326B contain a CMOS, low-voltage startup oscillator for a 1.1V guaranteed minimum startup input voltage. At startup, the low-voltage oscillator switches on the N-channel MOSFET until the output voltage reaches 2.15V. With output voltages > 2.15V, the boost-converter feedback and control circuitry are acitvated.

When the AS1326A/AS1326B is in regulation, it can operate down to 0.7V input since internal power for the device is bootstrapped from the output through pin OUT.

**Caution:** Do not apply full load until the output > 2.3V.

### Shutdown

The AS1326A/AS1326B feature an integrated shutdown mode that reduces quiescent current to  $0.1\mu$ A. During shutdown mode (ONN = 1 on AS1326A, ON = 0 on AS1326B), the internal reference and feedback/control circuitry are disabled.

Note: During shutdown, the output voltage is one diode drop below the input voltage.

#### Reference

The AS1326A/AS1326B contain an internal reference (1.250V  $\pm$ 1%). A 10nF ceramic bypass capacitor must be connected between pins REF and GND. REF can source up to 50µA of external load current.

Note: The bypass capacitor must be placed within 5mm (0.2") of pin REF.

# **9** Application Information

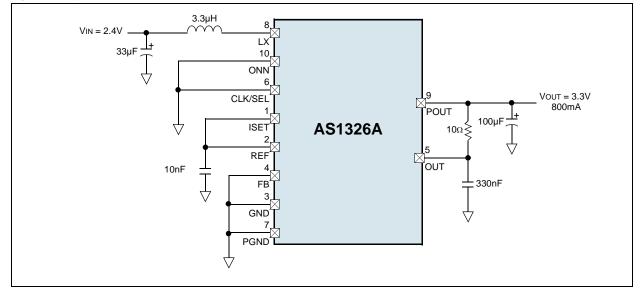

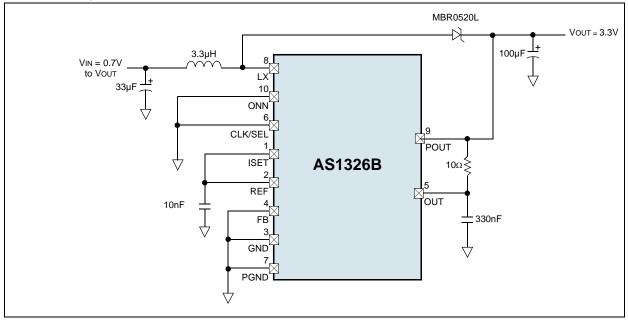

Figure 19. Typical AS1326A Application Circuit

## **Setting the Output Voltages**

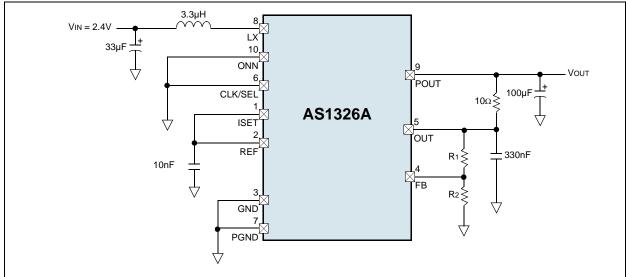

For a fixed 3.3V output, connect pin FB to GND. To set adjustable output voltages between 2.5 and 5.0V, connect a resistor voltage-divider to pin FB from pin OUT to GND (Figure 20).

Figure 20. Application Circuit using External Feedback Resistors

For the circuit shown in Figure 20, the input bias current into FB is <20nA, permitting large-value resistor-divider networks while maintaining accuracy. Place the resistor-divider network as close to the device as possible. Use  $a \le 270 k\Omega$  resistor for R<sub>2</sub>, then calculate R<sub>1</sub> as:

$$R_1 = R_2 \cdot \left(\frac{V_{OUT}}{V_{FB}} - 1\right)$$

(EQ 1)

Where:

VFB (the boost-regulator feedback set point) is 1.24V.

## Setting the Switch Current Limit

The ISET pin is used to adjust the inductor current limit and to implement the soft-start feature.

With pin ISET connected to pin REF, the inductor current limit is set to 1.6A. With ISET connected to a resistor-divider network from pin REF to GND, the current limit is calculated as:

$$ILIMIT = 1.6A \cdot \left(\frac{VISET}{1.25V}\right)$$

(EQ 2)

### Soft Start

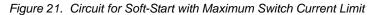

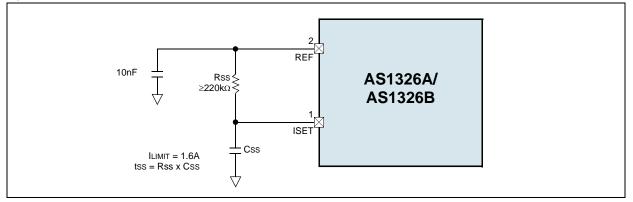

The soft-start feature can be implemented by placing a resistor between pin ISET and pin REF (see Figure 21) and a capacitor between pin ISET and GND.

At power-up, ISET is 0V and the LX current is zero. As the capacitor voltage rises, the current increases and the output voltage rises. The soft-start time constant is:

#### Where:

$\text{Rss} \geq \text{220k}\Omega.$

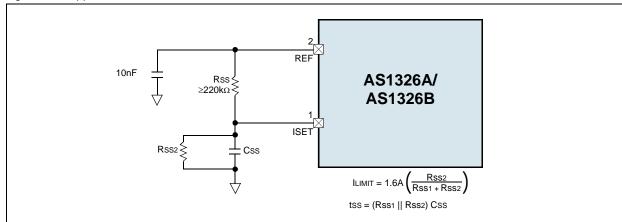

**Note:** Placing a capacitor across the lower resistor of the current-limiting resistor-divider network enables both the current-limit and soft-start (see Figure 22).

Revision 1.02

#### Figure 22. Application Circuit for Soft-Start with Reduced Switch Current Limit

## **Inductor Selection**

The AS1326A/AS1326B high switching-frequency allows the use of a small  $3.3\mu$ H surface-mount inductor. The inductor should generally have a saturation current rating exceeding the N-channel switch current limit; however, it is acceptable to bias the inductor current into saturation by as much as 20% if a slight reduction in efficiency is acceptable.

Lower current-rated inductors may be used if ISET is used to reduce the peak inductor current (see Setting the Switch Current Limit on page 12). For high efficiency, select an inductor with a high-frequency ferrite core material to reduce core losses. To minimize radiated noise, use a toroid or shielded inductor. Connect the inductor from the battery to the pin LX as close to the device as possible.

Table 7. Recommended Inductors

| Part Number     | L     | DCR                 | Current Rating | Dimensions (L/W/T) | Manufacturer             |

|-----------------|-------|---------------------|----------------|--------------------|--------------------------|

| MOS6020-332     | 3.3µH | $46 m\Omega$        | 1.8A           | 6.8x6.0x2.4mm      | Coilcraft                |

| LPS4018-332     | 3.3µH | $80 \text{m}\Omega$ | 2.0A           | 4x4x1.8mm          | www.coilcraft.com        |

| DO1608C-272     | 2.7µH | $80 \text{m}\Omega$ | 2.1A           | 6.6x4.45x2.92mm    |                          |

| CDRH5D18NP-4R1N | 4.1µH | $57 \text{m}\Omega$ | 1.95A          | 6x6x2mm            | Sumida<br>www.sumida.com |

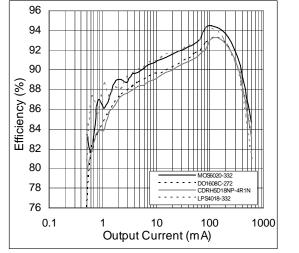

#### Figure 23. Efficiency vs. IOUT; VIN = 2V, VOUT = 3.3V

### **External Schottky Diode**

For output voltages greater than 4V, an external Schottky diode must be connected between pin LX and POUT, in parallel with the integrated synchronous rectifier (see Figure 25). The diode should be rated for 0.5A. An external diode is also recommended for applications that must start with input voltages at or below 1.8V. The Schottky diode carries current during startup and after the synchronous rectifier turns off; thus, its current rating only needs to be 500mA.

**Note:** Connect the diode as close to the IC as possible.

For circuits that do not require startup with inputs below 1.8V and have an output of 4V or less, the external diode is not needed.

**Caution:** Do not use ordinary rectifier diodes as their slow switching speeds and long reverse-recovery times render them unacceptable.

## Input and Output Filter Capacitors

Choose input and output filter capacitors that will service the input and output peak currents with acceptable voltage ripple. Choose input capacitors with voltage ratings greater than the maximum input voltage, and output capacitors with voltage ratings greater than the output voltage.

| Part Number        | С         | ESR                  | Rated Voltage | Dimensions (L/W/T) | Manufacturer                   |

|--------------------|-----------|----------------------|---------------|--------------------|--------------------------------|

| TPSC336K010R0150   | 33µF ±10% | 150m $\Omega$        | 10V           | 6x3.2x2.6mm        | AVX Corp<br>www.avxcorp.com    |

| T495V336K010ATE100 | 33µF ±10% | $100 \text{m}\Omega$ | 10V           | 7.3x4.3x2mm        | Kemet                          |

| A700V226M006ATE028 | 22µF ±20% | $28 \text{m}\Omega$  | 6.3V          | 7.3x4.3x2mm        | www.kemet.com                  |

| EEFCD0K330R        | 33µF ±20% | 18mΩ                 | 8V            | 7.3x4.3x1.8mm      | Panasonic<br>www.panasonic.com |

#### Table 8. Recommended Input Capacitor

Table 9. Recommended Output Capacitor

| Part Number        | С             | ESR                 | Rated Voltage | Dimensions (L/W/T) | Manufacturer                   |

|--------------------|---------------|---------------------|---------------|--------------------|--------------------------------|

| TPSD107K010R0050   | 100μF<br>±10% | $50 \text{m}\Omega$ | 10V           | 7.3x4.3x2.9mm      | AVX Corp<br>www.avxcorp.com    |

| T495D107M010ATE050 | 100µF<br>±20% | $50 \text{m}\Omega$ | 10V           | 7.3x4.3x2.8mm      | Kemet<br>www.kemet.com         |

| A700V826M006ATE018 | 82µF ±20%     | $18 \text{m}\Omega$ | 6.3V          | 7.3x4.3x2mm        |                                |

| EEFUD0J101R        | 100μF<br>±20% | $15 \text{m}\Omega$ | 6.3V          | 7.3x4.3x2.8mm      | Panasonic<br>www.panasonic.com |

Figure 25. Application Circuits using External Schottky Diode for Output Voltages Greater than 4V, or for Low-Voltage Startup Assistance

The input filter capacitor reduces peak currents drawn from the input source and also reduces input switching noise. The input voltage source impedance determines the required value of the input capacitor. When operating directly from one or two NiMh cells placed close to the AS1326A/AS1326B, use a single 33µF low-ESR input filter capacitor.

**Note:** With higher impedance batteries, such as alkaline and Li+, a higher value input capacitor may improve efficiency.

The output filter capacitor reduces output ripple voltage and provides the load with transient peak currents when necessary. For the output, a 100µF, low-equivalent series-resistance (ESR) capacitor is recommended for most applications.

Low-ESR tantalum capacitors offer a good trade-off between price and performance. Do not exceed the ripple current ratings of tantalum capacitors.

**Note:** Aluminum electrolytic capacitors should not be used as their high ESR typically results in higher output ripple voltage.

### Additional External Components

Two ceramic bypass capacitors are required for proper device operation (see Figure 20 on page 11):

- Bypass pin REF to GND with a 10nF ceramic capacitor.

- Bypass pin OUT to GND with a 330nF ceramic capacitor.

A  $10\Omega$  resistor is required between pin OUT and pin POUT (see Figure 25 on page 14).

Note: External components should be placed as close to its respective pins as possible, within 5mm (0.2").

### **Layout Considerations**

High switching-frequencies and large peak currents of the AS1326A/AS1326B make PC board layout a critical part of design. Poor design may cause excessive EMI and ground bounce, both of which can cause instability or regulation errors by corrupting the voltage and current feedback signals.

- Power components such as the inductor, converter IC, filter capacitors, and output diode should be placed as close together as possible, and their traces should be kept short, direct, and wide.

- Keep the voltage feedback network very close to the device, within 5mm (0.2") of the pin.

- Do as many vias as possible on the exposed pad (for thermal performance) to the ground plane

- Keep noisy traces, such as those from the pin LX, away from the voltage feedback network and guarded from them using grounded copper traces.

# **10 Package Drawings and Markings**

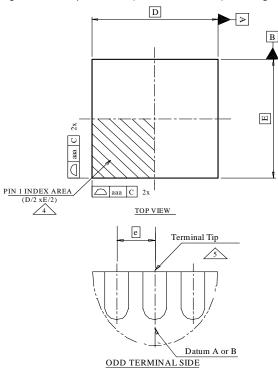

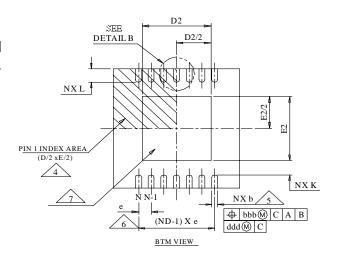

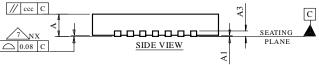

The devices are available in a 10-pin TDFN (3.0mm x 3.0mm) package.

Figure 26. 10-pin TDFN (3.0mm x 3.0mm) Package

| Symbol | Min  | Тур      | Max  | Notes |

|--------|------|----------|------|-------|

| А      | 0.70 | 0.75     | 0.80 | 1, 2  |

| A1     | 0.00 | 0.02     | 0.05 | 1, 2  |

| A3     |      | 0.20 REF |      | 1, 2  |

| L1     | 0.03 |          | 0.15 | 1, 2  |

| L2     |      |          | 0.13 | 1, 2  |

| aaa    |      | 0.15     |      | 1, 2  |

| bbb    |      | 0.10     |      | 1, 2  |

| CCC    |      | 0.10     |      | 1, 2  |

| ddd    |      | 0.05     |      | 1, 2  |

| eee    |      | 0.08     |      | 1, 2  |

| ggg    |      | 0.10     |      | 1, 2  |

| Symbol | Min  | Тур  | Max  | Notes   |

|--------|------|------|------|---------|

| D BSC  |      | 3.00 |      | 1, 2    |

| E BSC  |      | 3.00 |      | 1, 2    |

| D2     | 2.20 |      | 2.70 | 1, 2    |

| E2     | 1.40 |      | 1.75 | 1, 2    |

| L      | 0.30 | 0.40 | 0.50 | 1, 2    |

| θ      | 0°   |      | 14º  | 1, 2    |

| К      | 0.20 |      |      | 1, 2    |

| b      | 0.18 | 0.25 | 0.30 | 1, 2, 5 |

| е      |      | 0.50 |      |         |

| Ν      |      | 10   |      | 1, 2    |

| ND     |      | 5    |      | 1, 2, 5 |

#### Notes:

- 1. Dimensioning and tolerancing conform to ASME Y14.5 M-1994.

- 2. All dimensions are in millimeters; angles in degrees.

- 3. N is the total number of terminals.

- 4. The terminal #1 identifier and terminal numbering convention shall conform to *JEDEC 95-1*, *SPP-012*. Details of terminal #1 identifier are optional, but must be located within the zone indicated. The terminal #1 identifier may be either a mold or marked feature.

- 5. Dimension b applies to metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 6. ND refers to the maximum number of terminals on side D.

- 7. Figure 26 is shown for illustration only.

- 8. Unilateral coplanarity zone applies to the exposed heat sink slug as well as the terminals

# **11 Ordering Information**

The devices are available as the standard products shown in Table 10.

#### Table 10. Ordering Information

| Model        | Marking | Description                                               | <b>Delivery Form</b> | Package                        |

|--------------|---------|-----------------------------------------------------------|----------------------|--------------------------------|

| AS1326A-BTDT | ASLG    | Active-Low, High-Current, 0.8A<br>DC-DC Step-Up Converter | Tape & Reel          | 10-pin TDFN<br>(3.0mm x 3.0mm) |

| AS1326A-BTDR | ASLG    | Active-Low, High-Current 0.8A<br>DC-DC Step-Up Converter  | Tray                 | 10-pin TDFN<br>(3.0mm x 3.0mm) |

| AS1326B-BTDT | ASLH    | Active-High, High-Current 0.8A<br>DC-DC Step-Up Converter | Tape & Reel          | 10-pin TDFN<br>(3.0mm x 3.0mm) |

| AS1326B-BTDR | ASLH    | Active-High, High-Current 0.8A<br>DC-DC Step-Up Converter | Tray                 | 10-pin TDFN<br>(3.0mm x 3.0mm) |

## Copyrights

Copyright © 1997-2007, austriamicrosystems AG, Schloss Premstaetten, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

### Disclaimer

Devices sold by austriamicrosystems AG are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. austriamicrosystems AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. austriamicrosystems AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with austriamicrosystems AG for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by austriamicrosystems AG for each application. For shipments of less than 100 parts the manufacturing flow might show deviations from the standard production flow, such as test flow or test location.

The information furnished here by austriamicrosystems AG is believed to be correct and accurate. However, austriamicrosystems AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of austriamicrosystems AG rendering of technical or other services.

### **Contact Information**

Headquarters austriamicrosystems AG A-8141 Schloss Premstaetten, Austria

Tel: +43 (0) 3136 500 0 Fax: +43 (0) 3136 525 01

For Sales Offices, Distributors and Representatives, please visit:

http://www.austriamicrosystems.com/contact