## Am79C976

## PCnet-PRO<sup>™</sup> 10/100 Mbps PCI Ethernet Controller

## **DISTINCTIVE CHARACTERISTICS**

- Integrated Fast Ethernet controller for the Peripheral Component Interconnect (PCI) bus

- 32-bit glueless PCI host interface

- Supports PCI clock frequency from DC to 33 MHz independent of network clock

- Supports network operation with PCI clock from 15 MHz to 33 MHz

- High performance bus mastering architecture with integrated Direct Memory Access (DMA) Buffer Management Unit for low CPU and bus utilization

- PCI specification revision 2.2 compliant

- Supports PCI Subsystem/Subvendor ID/Vendor ID programming through the EEPROM interface

- Supports both PCI 3.3-V and 5.0-V signaling environments

- Plug and Play compatible

- Uses advanced PCI commands (MWI, MRL, MRM)

- Optionally supports PCI bursts aligned to cache line boundaries

- Supports big endian and little endian byte alignments

- Implements optional PCI power management event (PME) pin

- Supports 40-bit addressing (using PCI Dual Address Cycles)

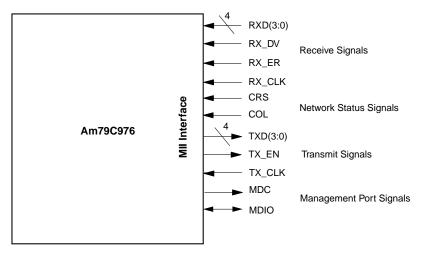

- Media Independent Interface (MII) for connecting external 10/100 megabit per second (Mbps) transceivers

- IEEE 802.3-compliant MII

- Intelligent Auto-Poll<sup>™</sup> external PHY status monitor and interrupt

- Supports both auto-negotiable and non autonegotiable external PHYs

- Supports 10BASE-T, 100BASE-TX/FX, 100BASE-T4, and 100BASE-T2 IEEE 802.3compliant MII PHYs at full- or half-duplex

- Full-duplex operation supported with independent Transmit (TX) and Receive (RX) channels

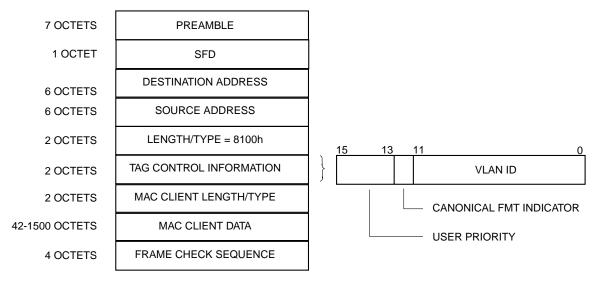

- Includes support for IEEE 802.1Q VLANs

- Automatically inserts, deletes, or modifies VLAN tag

- Optionally filters untagged frames

- Provides optional flow control features

- Recognizes and transmits IEEE 802.3x MAC flow control frames

- Asserts collision-based back pressure in half-duplex mode

- Provides internal Management Information Base (MIB) counters for network statistics

- Supports PC97, PC98, PC99, and Net PC requirements

- Implements full OnNow features including pattern matching and link status wake-up

- Implements Magic Packet™ mode

- Magic Packet mode and the physical address loaded from EEPROM at power up without requiring PCI clock

- Supports PCI Bus Power Management Interface Specification Version 1.1

- Supports Advanced Configuration and Power Interface (ACPI) Specification Version 1.0

- Supports Network Device Class Power Management Specification Version 1.0

- Large independent external TX and RX FIFOs

- Supports up to 4 megabytes (Mbytes) external SSRAM for RX and TX frame storage

- Programmable FIFO watermarks for both transmit and receive operations

- Receive frame queuing for high latency PCI bus host operation

- Programmable allocation of buffer space between transmit and receive queues

- Dual-speed CSMA/CD (10 Mbps and 100 Mbps) Media Access Controller (MAC) compliant with IEEE/ANSI 802.3 and Blue Book Ethernet standards

- Programmable internal/external loopback capabilities

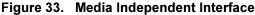

- Supports patented External Address Detection Interface (EADI) with receive frame tagging support for internetworking applications

- EEPROM interface supports jumperless design and provides through-chip programming

- Supports full programmability of all internal registers through EEPROM mapping

- Programmable PHY reset output pin capable of resetting external PHY without needing buffering

- Integrated oscillator circuit is controlled by external crystal

- Extensive programmable LED status support

- Supports up to 16 Mbyte optional Boot PROM or Flash for diskless node application

- Look-Ahead Packet Processing (LAPP) data handling technique reduces system overhead by allowing protocol analysis to begin before the end of a receive frame

- Optional delayed interrupt feature reduces CPU overhead

- Programmable Inter Packet Gap (IPG) to address less aggressive network MAC controllers

- Offers the Modified Back-Off algorithm to address the Ethernet Capture Effect

- Optionally sends and receives non-standard frames of up to 64K octets in length

- IEEE 1149.1-compliant JTAG Boundary Scan test access port interface for board-level production connectivity test

- Provides built-in self test (MBIST) for the external SSRAM

- Software compatible with AMD PCnet Family and LANCE/C-LANCE register and descriptor architecture

- Compatible with the existing PCnet Family driver and diagnostic software (except for statistics)

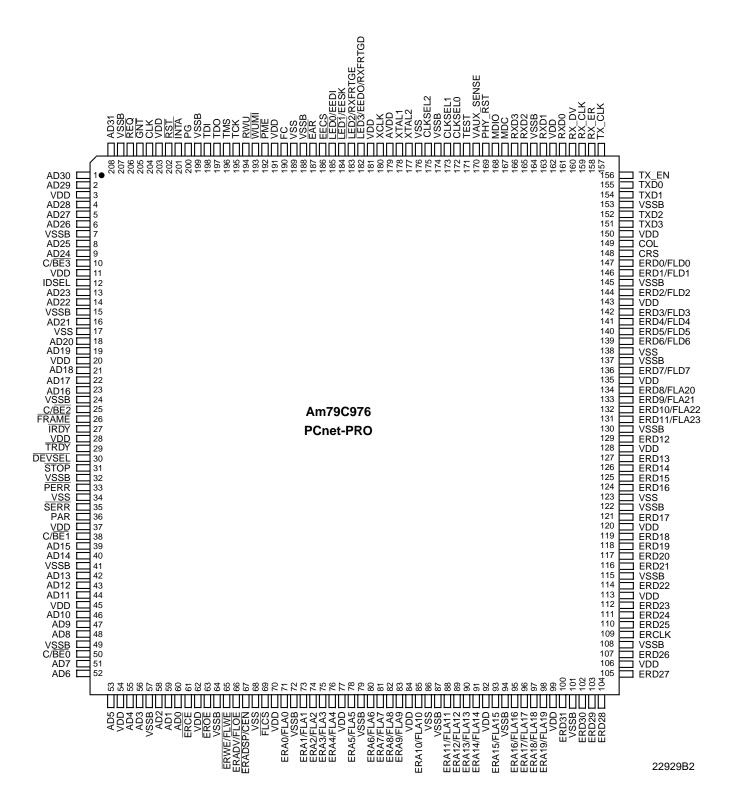

- Available in 208-pin PQFP package

- +3.3-V power supply with 5-V tolerant I/Os enables broad system compatibility

- Support for operation in Industrial temperature range (-40° C to +85° C) available.

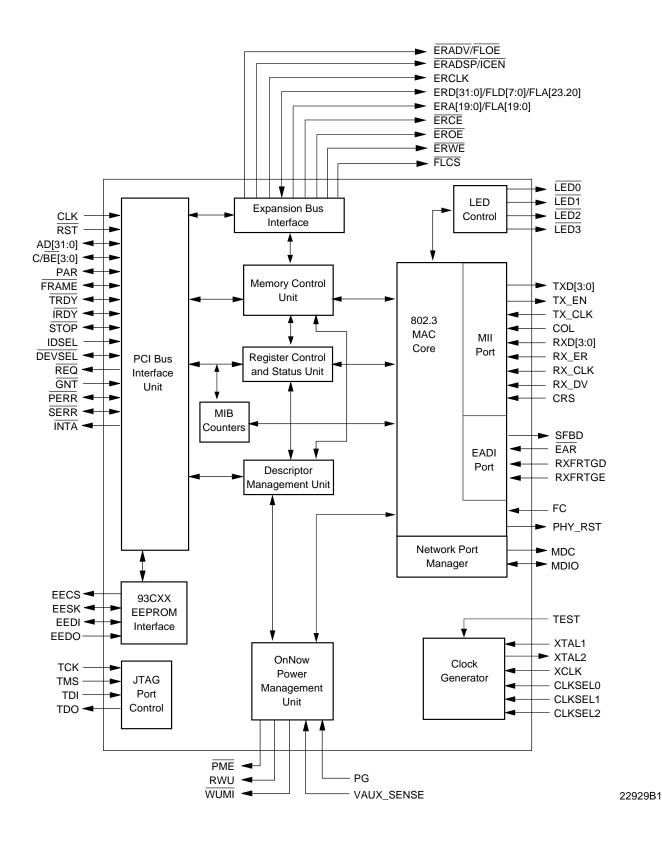

## **GENERAL DESCRIPTION**

The Am79C976 controller is a highly-integrated 32-bit full-duplex, 10/100-Megabit per second (Mbps) Ethernet controller solution, designed to address high-performance system application requirements. It is a flexible bus mastering device that can be used in any application, including network-ready PCs and bridge/router designs. The bus master architecture provides high data throughput and low CPU and system bus utilization. The Am79C976 controller is fabricated with advanced low-power 3.3-V CMOS process to provide low operating current for power sensitive applications.

The Am79C976 controller also has several enhancements over its predecessor, the Am79C971 PCnet-*FAST* device. In addition to providing access to a larger SSRAM, it further reduces system implementation cost by the addition of a new EEPROM programmable pin (PHY\_RST) and the integration of the PAL function needed for Magic Packet application. The PHY\_RST pin is implemented to reset the external PHY without increasing the load to the PCI bus and to block RST to the PHY when PG input is LOW.

The 32-bit multiplexed bus interface unit provides a direct interface to the PCI local bus, simplifying the design of an Ethernet node in a PC system. The Am79C976 controller provides the complete interface to an Expansion ROM or Flash device allowing add-on card designs with only a single load per PCI bus interface pin. With its built-in support for both little and big endian byte alignment, this controller also addresses non-PC applications. The Am79C976 controller's advanced CMOS design allows the bus interface to be connected to either a +5-V or a +3.3-V signaling environment. An IEEE 1149.1-compliant JTAG test interface for board-level testing is also provided.

The Am79C976 controller is also compliant with the PC97, PC98, PC99, and Network PC (Net PC) specifications. It includes the full implementation of the Microsoft OnNow and ACPI specifications, which are backward compatible with the Magic Packet technology, and it is compliant with the PCI Bus Power Management Interface Specification by supporting the four power management states (D0, D1, D2, and D3), the optional PME pin, and the necessary configuration and data registers.

The Am79C976 controller is ideally suited for Net PC, motherboard, network interface card (NIC), and embedded designs. It is available in a 208-pin Plastic Quad Flat Pack (PQFP) package.

The Am79C976 controller contains a bus interface unit, a DMA Buffer Management Unit, an ISO/IEC 8802-3 (IEEE 802.3)-compliant Media Access Controller (MAC), and an IEEE 802.3-compliant MII. An interface to an external RAM of up to 4 Mbytes is provided for frame storage. The MII supports IEEE 802.3-compliant full-duplex and half-duplex operations at 10 Mbps or 100 Mbps. The MII TX and RX clock signals can be stopped independently for home networking applications.

The Am79C976 controller is register compatible with the LANCE<sup>™</sup> (Am7990) and C-LANCE<sup>™</sup> (Am79C90) Ethernet controllers, and all Ethernet controllers in the PCnet Family *except* ILACC<sup>™</sup> (Am79C900), including the PCnet<sup>™</sup>-ISA controller (Am79C960), PCnet<sup>™</sup>-ISA+ (Am79C961), PCnet<sup>™</sup>-ISA II (Am79C961A), PCnet<sup>™</sup>-32 (Am79C965), PCnet<sup>™</sup>-PCI (Am79C970), PCnet<sup>™</sup>-PCI II (Am79C970A), and the PCnet<sup>™</sup>-FAST (Am79C971).

The Buffer Management Unit supports the LANCE and PCnet descriptor software models.

The Am79C976 controller supports auto-configuration in the PCI configuration space. Additional Am79C976 controller configuration parameters, including the unique IEEE physical address, can be read from an external nonvolatile memory (EEPROM) immediately following system reset.

In addition, the device provides programmable on-chip LED drivers for transmit, receive, collision, link integrity, Magic Packet status, activity, address match, fullduplex, or 100 Mbps status. The Am79C976 controller also provides an EADI to allow external hardware address filtering in internetworking applications and a receive frame tagging feature.

With the rise of embedded networking applications operating in harsh environments where temperatures may exceed the normal commercial temperature ( $0^{\circ}$  C to +70° C) window, an industrial temperature (-40° C to +85° C) version is available. This industrial temperature version of the PCnet-PRO Ethernet controller is characterized across the industrial temperature range (-40° C to +85° C) within the published power supply specification (4.75V to 5.25V; ±5% Vcc). Thus, conformance of the PCnet-PRO performance over this temperature range is guaranteed by a design and characterization monitor.

## **BLOCK DIAGRAM**

## TABLE OF CONTENTS

| DISTINCTIVE CHARACTERISTICS                   |

|-----------------------------------------------|

| GENERAL DESCRIPTION                           |

| BLOCK DIAGRAM                                 |

| TABLE OF CONTENTS                             |

| LIST OF FIGURES                               |

| LIST OF TABLES                                |

| ORDERING INFORMATION                          |

| Standard Products                             |

| CONNECTION DIAGRAM (PQR208)18                 |

| PIN DESIGNATIONS (PQR208)19                   |

| Listed By Pin Number                          |

| Listed By Group                               |

| PIN DESCRIPTIONS                              |

| PCI Interface                                 |

| Board Interface                               |

| EEPROM Interface                              |

| External Memory Interface                     |

| Media Independent Interface                   |

| External Address Detection Interface          |

| IEEE 1149.1 (1990) Test Access Port Interface |

| Power Supply Pins                             |

| BASIC FUNCTIONS                               |

| System Bus Interface                          |

| Software Interface                            |

| Network Interface                             |

| DETAILED FUNCTIONS                            |

| Slave Bus Interface Unit                      |

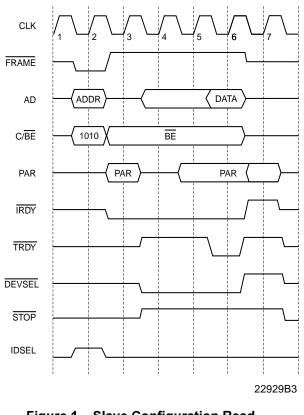

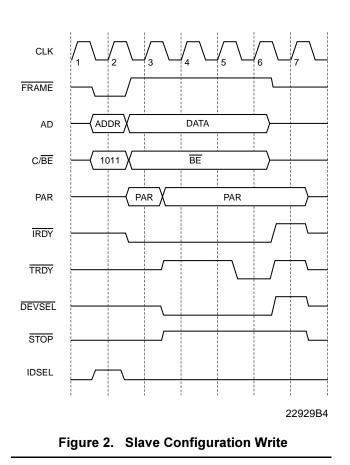

| Slave Configuration Transfers                 |

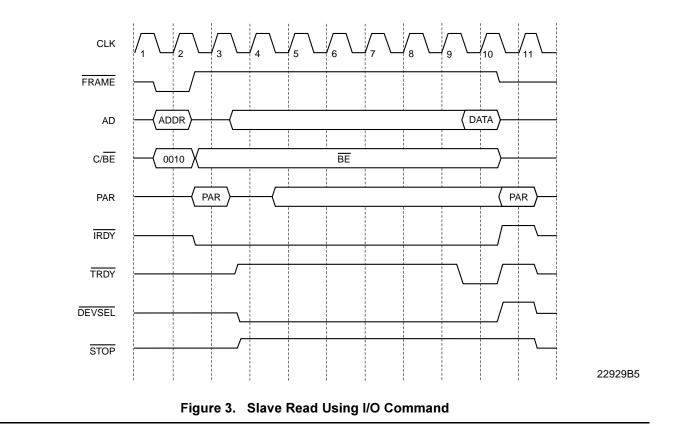

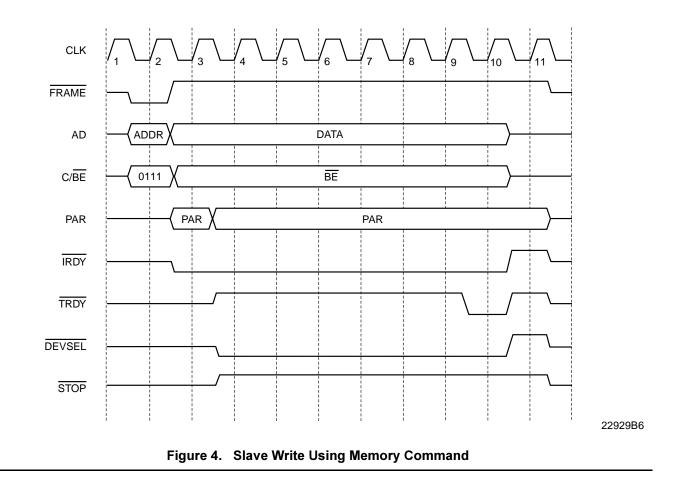

| Slave I/O Transfers                           |

| Expansion ROM Transfers                       |

| Slave Cycle Termination                       |

| Disconnect When Busy                          |

| Disconnect Of Burst Transfer                  |

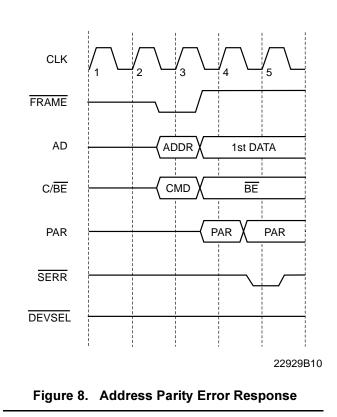

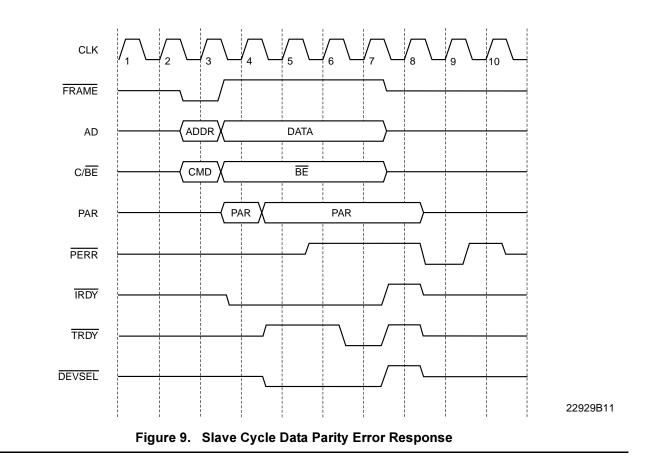

| Parity Error Response                         |

| Master Bus Interface Unit                     |

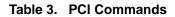

| Bus Acquisition                               |

| Bus Master DMA Transfers                      |

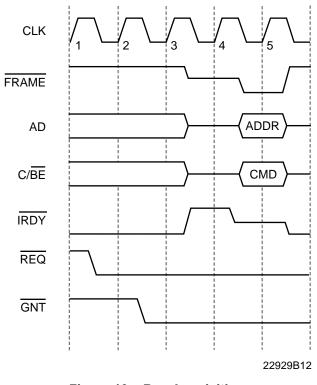

| Basic Non-Burst Read Transfer                 |

| Basic Burst Read Transfer41                   |

| Basic Non-Burst Write Transfer                |

| Basic Burst Write Transfer44                  |

| DMA Burst Alignment                           |

| Target Initiated Termination                  |

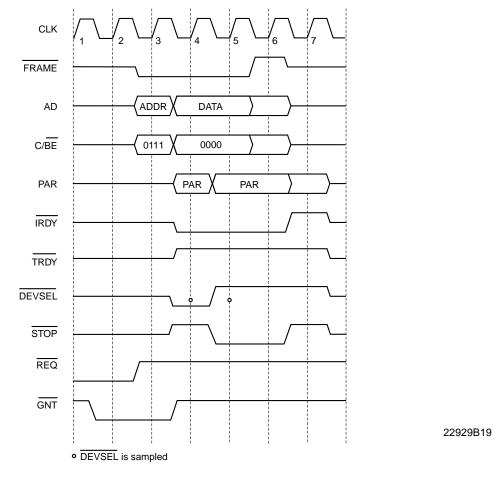

| Disconnect With Data Transfer                 |

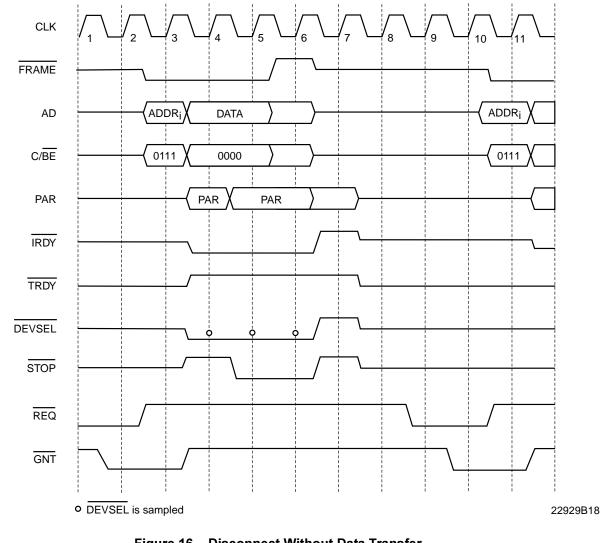

| Disconnect Without Data Transfer              |

| Target Abort                                  |

| Master Initiated Termination                  |

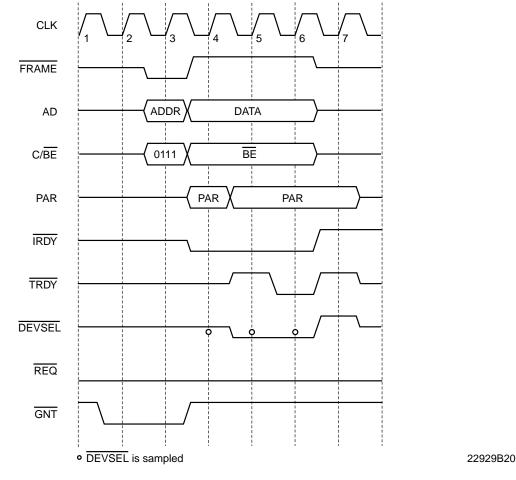

| Preemption During Non-Burst Transaction       |

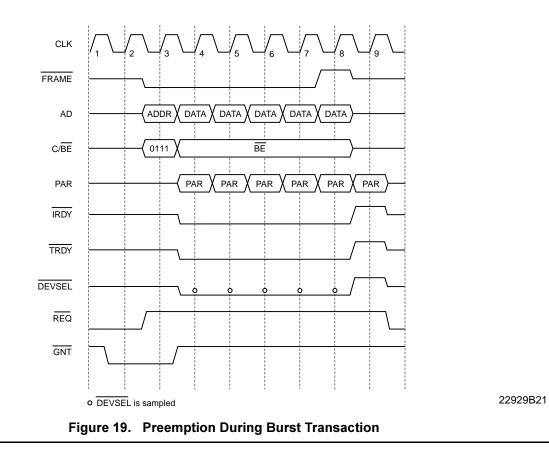

| Preemption During Burst Transaction           |

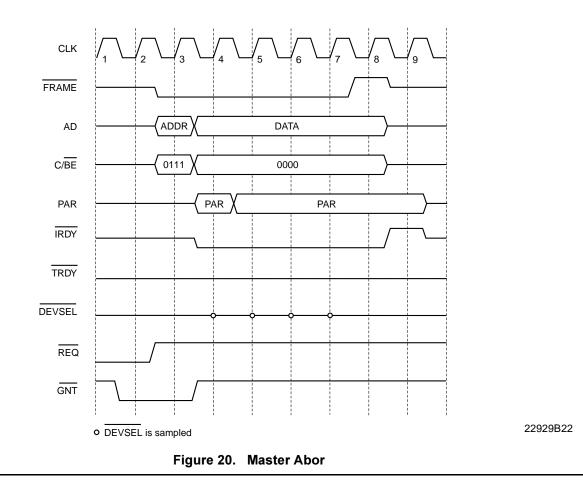

| Master Abort                                  |

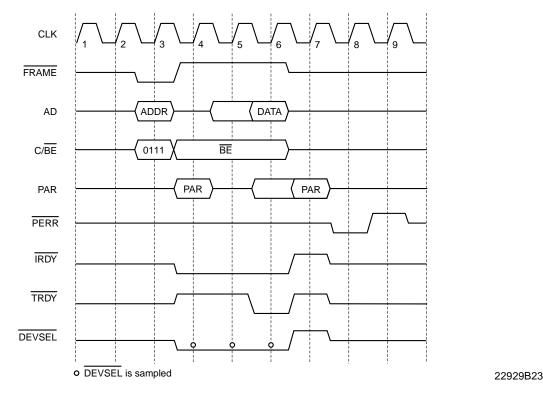

| Parity Error Response                         |

| Initialization Block DMA Transfers            |

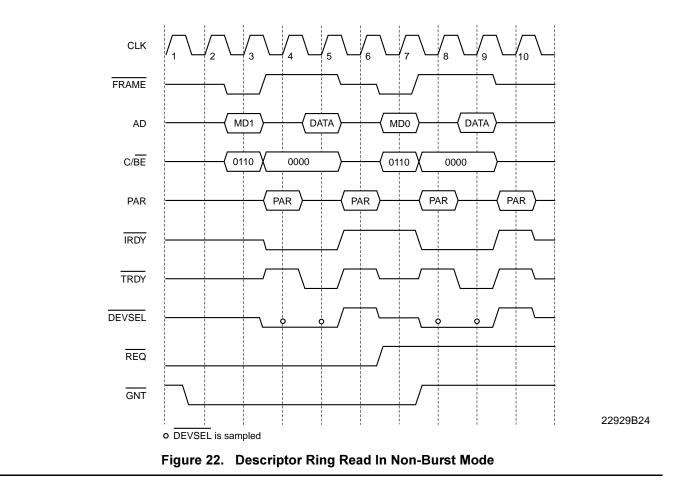

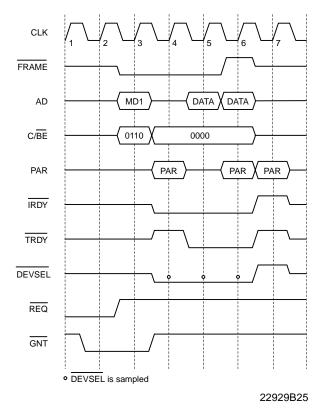

| Descriptor DMA Transfers                      |

| FIFO DMA Transfers                            |

| Descriptor Management Unit                    |

| Initialization                                |

| Re-Initialization                               |   |    |

|-------------------------------------------------|---|----|

| Run and Suspend                                 |   |    |

| Descriptor Management                           |   |    |

| Descriptor Rings                                |   |    |

| Polling                                         |   |    |

| Transmit Polling                                |   |    |

| Receive Polling                                 |   |    |

| Look Ahead Packet Processing                    |   |    |

| Software Interrupt Timer                        |   |    |

| Media Access Control                            |   |    |

| Transmit and Receive Message Data Encapsulation |   |    |

| Framing.                                        |   |    |

| Destination Address Handling                    |   |    |

| Error Detection                                 |   |    |

| Media Access Management                         |   |    |

|                                                 |   |    |

| Signal Quality Error (SQE) Test                 |   |    |

| Collision Handling.                             |   |    |

| Transmit Operation.                             |   |    |

|                                                 |   |    |

|                                                 |   |    |

|                                                 |   |    |

| Transmit Error Conditions                       |   |    |

| Loss of Carrier                                 |   |    |

|                                                 |   |    |

| Transmit FIFO Underflow                         |   |    |

| Receive Operation                               |   |    |

| Receive Function Programming                    |   |    |

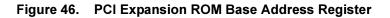

| Address Matching                                |   |    |

| Automatic Pad Stripping                         |   |    |

| Receive FCS Checking                            |   |    |

| Receive Exception Conditions                    |   |    |

| Statistics Counters                             |   |    |

| Receive Statistics Counters.                    |   |    |

| Transmit Statistics Counters                    |   |    |

| VLAN Support                                    |   |    |

| VLAN Frame Size                                 |   |    |

| Admit Only VLAN Frames Option                   |   |    |

| VLAN Tags in Descriptors                        |   |    |

| Loopback Operation.                             |   |    |

| Miscellaneous Loopback Features                 |   |    |

| Full-Duplex Operation                           |   |    |

| Full-Duplex Link Status LED Support             |   |    |

| Media Independent Interface                     |   |    |

| MII Transmit Interface                          |   |    |

| MII Receive Interface.                          |   |    |

| MII Network Status Interface                    |   |    |

| MII Management Interface.                       |   |    |

| MII Management Frames                           |   |    |

| Host CPU Access to External PHY                 |   |    |

| Auto-Poll State Machine                         |   |    |

| Network Port Manager                            |   |    |

| Auto-Negotiation                                |   |    |

| Auto-Negotiation With Multiple PHY Devices      |   |    |

| Operation Without MMI Management Interface.     |   |    |

| Regulating Network Traffic.                     |   |    |

| MAC Control Pause Frames                        |   |    |

| Back Pressure                                   | 8 | 37 |

| Enabling Traffic Regulation                                 |     |

|-------------------------------------------------------------|-----|

| Hardware Control of Traffic Regulation                      |     |

| Software Control of Traffic Regulation                      |     |

| Programming the Pause Length Register                       |     |

| PAUSE Frame Reception                                       |     |

| Delayed Interrupts                                          |     |

| External Address Detection Interface: Receive Frame Tagging |     |

| External Memory Interface.                                  |     |

| Expansion ROM - Boot Device Access                          |     |

| Direct Flash Access.                                        |     |

| Flash/EPROM Read                                            |     |

| SRAM Configuration                                          |     |

| EEPROM Interface                                            |     |

| Automatic EEPROM Read Operation                             |     |

| EEPROM Auto-Detection                                       |     |

| Direct Access to the Interface                              |     |

| EEPROM CRC Calculation                                      |     |

| LED Support                                                 | 98  |

| Power Savings Mode                                          |     |

| Power Management Support.                                   |     |

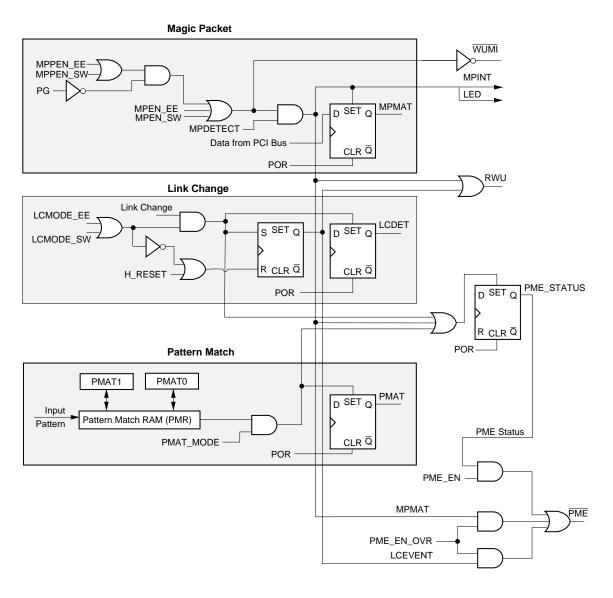

| OnNow Wake-Up Sequence                                      | 100 |

| RWU Wake-Up Sequence                                        | 101 |

| Link Change Detect                                          | 101 |

| Magic Packet Mode                                           |     |

| OnNow Pattern Match Mode                                    |     |

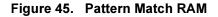

| Pattern Match RAM (PMR)                                     |     |

| IEEE 1149.1 (1990) Test Access Port Interface               |     |

| Boundary Scan Circuit                                       |     |

| TAP Finite State Machine                                    |     |

| Supported Instructions                                      |     |

| Boundary Scan Register                                      |     |

| Other Data Registers.                                       |     |

| Reset                                                       |     |

| H_RESET                                                     |     |

| EE_RESET                                                    |     |

| S_RESET                                                     |     |

| Power on Reset                                              |     |

| External PHY Reset                                          |     |

| Software Access                                             |     |

| PCI Configuration Registers                                 |     |

| I/O Resources                                               |     |

| I/O Registers                                               |     |

| Address PROM Space                                          |     |

| Reset Register                                              |     |

| Word I/O Mode                                               |     |

| Double Word I/O Mode                                        | 108 |

| USER ACCESSIBLE REGISTERS                                   | 111 |

| PCI Configuration Registers                                 | 111 |

| PCI Vendor ID Register                                      | 111 |

| PCI Device ID Register                                      | 111 |

| PCI Command Register                                        |     |

| PCI Status Register                                         |     |

| PCI Revision ID Register.                                   |     |

| PCI Programming Interface Register                          |     |

| PCI Sub-Class Register                                      |     |

| PCI Base-Class Register.                                    | 114 |

| PCI C  | Cache Line Size Register                                             | <br>1       | 115 |

|--------|----------------------------------------------------------------------|-------------|-----|

|        | atency Timer Register                                                |             |     |

| PCI H  | leader Type Register                                                 | <br>1       | 115 |

|        | O Base Address Register                                              |             |     |

|        | /lemory Mapped I/O Base Address Register                             |             |     |

| PCI S  | Subsystem Vendor ID Register                                         | <br>1       | 116 |

| PCI S  | Subsystem ID Register                                                | <br>1       | 17  |

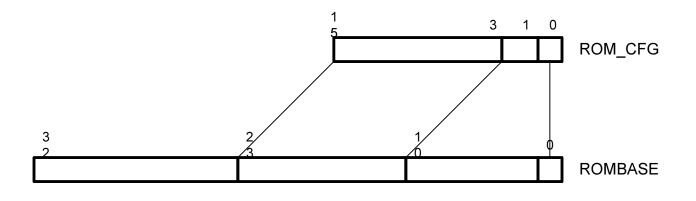

| PCI E  | Expansion ROM Base Address Register                                  | <br>1       | 117 |

| PCI C  | Capabilities Pointer Register                                        | <br>1       | 118 |

| PCI Ir | nterrupt Line Register                                               | <br>1       | 118 |

| PCI Ir | nterrupt Pin Register                                                | <br>1       | 118 |

| PCI M  | /IN_GNT Register                                                     | <br>1       | 118 |

| PCI M  | /IAX_LAT Register                                                    | <br>1       | 119 |

|        | Capability Identifier Register                                       |             |     |

|        | Next Item Pointer Register                                           |             |     |

|        | Power Management Capabilities Register (PMC)                         |             |     |

|        | Power Management Control/Status Register (PMCSR)                     |             |     |

|        | PMCSR Bridge Support Extensions Register                             |             |     |

|        | Data Register                                                        |             |     |

|        | Mapped Registers                                                     |             |     |

|        | Dffset                                                               |             |     |

|        | /ALUE0: Auto-Poll Value0 Register                                    |             |     |

|        | /ALUE1: Auto-Poll Value1 Register                                    |             |     |

|        | /ALUE2: Auto-Poll Value2 Register                                    |             |     |

|        | /ALUE3: Auto-Poll Value3 Register                                    |             |     |

|        | ALUE4: Auto-Poll Value4 Register                                     |             |     |

|        | ALUE5: Auto-Poll Value5 Register                                     |             |     |

|        |                                                                      |             |     |

|        | OPOLL0: Auto-Poll0 Register           OPOLL4: Auto-Poll0 Register    |             |     |

|        | OPOLL1: Auto-Poll1 Register           DPOLL0: A to Pullo Publication |             |     |

|        | DPOLL2: Auto-Poll2 Register                                          |             |     |

|        | OPOLL3: Auto-Poll3 Register                                          |             |     |

|        | DPOLL4: Auto-Poll4 Register                                          |             |     |

|        | DPOLL5: Auto-Poll5 Register.                                         |             |     |

|        | R: Receive Ring Base Address Register                                |             |     |

|        | K: Transmit Ring Base Address Register                               |             |     |

|        | ID: Chip ID Register                                                 |             |     |

|        | OLLTIME: Chain Poll Timer Register                                   |             |     |

|        | 0: Command0                                                          |             |     |

|        | 2: Command2                                                          |             |     |

| CMD3   | 3: Command3                                                          | <br>1       | 135 |

| CMD7   | 7: Command7                                                          | <br>1       | 138 |

| CTRL   | _0: Control0 Register                                                | <br>1       | 139 |

| CTRL   | 1: Control1 Register                                                 | <br>1       | 140 |

| CTRL   | .2: Control2 Register                                                | <br>1       | 143 |

| CTRL   | .3: Control3 Register                                                | <br>1       | 44  |

| DATA   | MBIST: Memory Built-in Self-Test Access Register                     | <br>1       | 145 |

|        | YED_INT: Delayed Interrupts Register                                 |             |     |

|        | ROM_ACC: EEPROM Access Register                                      |             |     |

|        | H_ADDR: Flash Address Register                                       |             |     |

|        | SH_DATA: Flash Data Register                                         |             |     |

|        | W: Flow Control Register.                                            |             |     |

|        | Inter-Frame Spacing Part 1 Register                                  |             |     |

|        | Interrupt0                                                           |             |     |

|        | N0: Interrupt0 Enable                                                |             |     |

|        | Inter-Packet Gap Register                                            |             |     |

|        | RF: Logical Address Filter Register                                  |             |     |

|        | Control Register                                                     |             |     |

|        | Control Register                                                     |             |     |

|        |                                                                      | <br>• • • • | .00 |

| LED2 Control Register                                   | 159 |

|---------------------------------------------------------|-----|

| LED3 Control Register                                   | 159 |

| MAX_LAT_A: PCI Maximum Latency Alias Register           | 160 |

| MIN_GNT_A: PCI Minimum Grant Alias Register             | 160 |

| PADR: Physical Address Register                         |     |

| Pause Count Register                                    |     |

| PCIDATA0: PCI DATA Register Zero Alias Register         |     |

| PCIDATA1: PCI DATA Register One Alias Register          |     |

| PCIDATA2: PCI DATA Register Two Alias Register          |     |

| PCIDATA3: PCI DATA Register Three Alias Register        |     |

| PCIDATA4: PCI DATA Register Four Alias Register         |     |

| PCIDATA5: PCI DATA Register Five Alias Register         |     |

| PCIDATA6: PCI DATA Register Six Alias Register.         |     |

| PCIDATA7: PCI DATA Register Seven Alias Register        |     |

| PHY Access Register.                                    |     |

| PMAT0: OnNow Pattern Register 0                         |     |

| PMAT1: OnNow Pattern Register 1                         |     |

| PMC_A: PCI Power Management Capabilities Alias Register |     |

| Receive Protect Register                                |     |

| RCV_RING_LEN: Receive Ring Length Register              |     |

| ROM_CFG: ROM Base Address Configuration Register        |     |

| SID_A: PCI Subsystem ID Alias Register                  |     |

| SRAM Boundary Register                                  |     |

| SRAM Size Register                                      |     |

| STAT0: Status0                                          |     |

|                                                         |     |

| Software Timer Value Register                           |     |

| SVID_A: PCI Subsystem Vendor ID Alias Register.         |     |

| VID_A: PCI Vendor ID Alias Register                     |     |

| XMT_RING_LEN: Transmit Ring Length Register             |     |

| XMTPOLLTIME: Transmit Poll Timer Register               |     |

| RAP Register                                            |     |

| RAP: Register Address Port                              |     |

| Control and Status Registers.                           |     |

| CSR0: Am79C976 Controller Status and Control Register   |     |

| CSR1: Initialization Block Address 0                    |     |

| CSR2: Initialization Block Address 1                    |     |

| CSR3: Interrupt Masks and Deferral Control.             |     |

| CSR4: Test and Features Control                         |     |

| CSR5: Extended Control and Interrupt 1                  |     |

| CSR6: Reserved                                          |     |

| CSR7: Extended Control and Interrupt 2                  |     |

| CSR8: Logical Address Filter 0                          |     |

| CSR9: Logical Address Filter 1                          |     |

| CSR10: Logical Address Filter 2                         |     |

| CSR11: Logical Address Filter 3                         |     |

| CSR12: Physical Address Register 0                      |     |

| CSR13: Physical Address Register 1                      |     |

| CSR14: Physical Address Register 2                      |     |

| CSR15: Mode                                             |     |

| CSR16-23: Reserved                                      |     |

| CSR24: Base Address of Receive Ring Lower               |     |

| CSR25: Base Address of Receive Ring Upper               |     |

| CSR26-29: Reserved                                      |     |

| CSR30: Base Address of Transmit Ring Lower              |     |

| CSR31: Base Address of Transmit Ring Upper              |     |

| CSR32-46: Reserved                                      |     |

| CSR47: Transmit Polling Interval                        | 188 |

| CSR48: Reserved                                         |     |

|   | CSR49: Chain Polling Interval                                                                                   | . 188 |

|---|-----------------------------------------------------------------------------------------------------------------|-------|

|   | CSR50-57: Reserved                                                                                              | . 189 |

|   | CSR58: Software Style                                                                                           | . 189 |

|   | CSR59-75: Reserved                                                                                              | . 191 |

|   | CSR76: Receive Ring Length                                                                                      |       |

|   | CSR77: Reserved                                                                                                 |       |

|   | CSR78: Transmit Ring Length                                                                                     |       |

|   | CSR79: Reserved                                                                                                 |       |

|   | CSR80: DMA Transfer Counter and FIFO Threshold Control                                                          |       |

|   |                                                                                                                 |       |

|   | CSR81-87: Reserved                                                                                              |       |

|   | CSR88: Chip ID Register Lower                                                                                   |       |

|   | CSR89: Chip ID Register Upper                                                                                   |       |

|   | CSR90-99: Reserved                                                                                              |       |

|   | CSR100: Bus Timeout                                                                                             | . 193 |

|   | CSR101-111: Reserved                                                                                            | . 193 |

|   | CSR112: Missed Frame Count                                                                                      | . 193 |

|   | CSR113: Reserved                                                                                                | . 193 |

|   | CSR114: Receive Collision Count.                                                                                |       |

|   | CSR115: Reserved                                                                                                |       |

|   | CSR116: OnNow Power Mode Register                                                                               |       |

|   | CSR117-121: Reserved                                                                                            |       |

|   |                                                                                                                 |       |

|   | CSR122: Advanced Feature Control.                                                                               |       |

|   | CSR123: Reserved                                                                                                |       |

|   | CSR124: Test Register 1                                                                                         |       |

|   | CSR125: MAC Enhanced Configuration Control.                                                                     |       |

| E | Bus Configuration Registers                                                                                     | . 197 |

|   | BCR0: Master Mode Read Active                                                                                   | . 198 |

|   | BCR1: Master Mode Write Active                                                                                  | . 198 |

|   | BCR2: Miscellaneous Configuration                                                                               |       |

|   | BCR4: LED0 Status.                                                                                              |       |

|   | BCR5: LED1 Status.                                                                                              |       |

|   | BCR6: LED2 Status.                                                                                              |       |

|   | BCR7: LED3 Status.                                                                                              |       |

|   |                                                                                                                 |       |

|   | BCR9: Full-Duplex Control                                                                                       |       |

|   | BCR16: I/O Base Address Lower                                                                                   |       |

|   | BCR17: I/O Base Address Upper                                                                                   |       |

|   | BCR18: Burst and Bus Control Register                                                                           |       |

|   | BCR19: EEPROM Control and Status                                                                                | . 209 |

|   | BCR20: Software Style                                                                                           | . 212 |

|   | BCR22: PCI Latency Register.                                                                                    | . 214 |

|   | BCR23: PCI Subsystem Vendor ID Register.                                                                        | . 214 |

|   | BCR24: PCI Subsystem ID Register                                                                                |       |

|   | BCR25: SRAM Size Register                                                                                       |       |

|   | BCR26: SRAM Boundary Register                                                                                   |       |

|   | BCR27: SRAM Interface Control Register.                                                                         |       |

|   | BCR28: Expansion Bus Port Address Lower (Used for Flash/EPROM and SRAM Accesses).                               |       |

|   |                                                                                                                 |       |

|   | BCR29: Expansion Port Address Upper (Used for Flash/EPROM Accesses)                                             |       |

|   | BCR30: Expansion Bus Data Port Register                                                                         |       |

|   | BCR31: Software Timer Register                                                                                  |       |

|   | BCR32: MII Control and Status Register.                                                                         |       |

|   | BCR33: MII Address Register                                                                                     |       |

|   | BCR34: MII Management Data Register                                                                             | . 220 |

|   | BCR35: PCI Vendor ID Register                                                                                   |       |

|   | BCR36: PCI Power Management Capabilities (PMC) Alias Register                                                   |       |

|   | BCR37: PCI DATA Register Zero (DATA0) Alias Register                                                            |       |

|   | BCR38: PCI DATA Register One (DATA1) Alias Register                                                             |       |

|   | BCR39: PCI DATA Register Two (DATA2) Alias Register                                                             |       |

|   | BCR40: PCI DATA Register Three (DATA3) Alias Register                                                           |       |

|   | אומט הארט היא אין אווא אין אווא אין אווא אין אווא אין אוא אין אוא אין אוא אין אווא אין אווא אין אווא אין אווא א | . 222 |

| BCR41: PCI DATA Register Four (DATA4) Alias Register            | 222                             |

|-----------------------------------------------------------------|---------------------------------|

| BCR42: PCI DATA Register Five (DATA5) Alias Register            | 222                             |

| BCR43: PCI DATA Register Six (DATA6) Alias Register             |                                 |

| BCR44: PCI DATA Register Seven (DATA7) Alias Register           |                                 |

| BCR45: OnNow Pattern Matching Register 1                        | 223                             |

| BCR46: OnNow Pattern Matching Register 2                        |                                 |

| BCR47: OnNow Pattern Matching Register 3                        |                                 |

| Initialization Block                                            |                                 |

| RLEN and TLEN                                                   |                                 |

| RDRA and TDRA                                                   |                                 |

| LADRF.                                                          |                                 |

| PADR                                                            |                                 |

| Mode                                                            | -                               |

| Receive Descriptors.                                            |                                 |

| Transmit Descriptors                                            |                                 |

| REGISTER SUMMARY                                                |                                 |

| PCI Configuration Registers                                     |                                 |

| Memory-Mapped Registers                                         |                                 |

| Control and Status Registers                                    |                                 |

| Bus Configuration Registers                                     |                                 |

| REGISTER BIT CROSS REFERENCE                                    |                                 |

| REGISTER PROGRAMMING SUMMARY                                    |                                 |

|                                                                 |                                 |

| Programmable Registers                                          |                                 |

| OPERATING RANGES                                                |                                 |

| DC CHARACTERISTICS OVER COMMERCIAL OPERATING RANGES             |                                 |

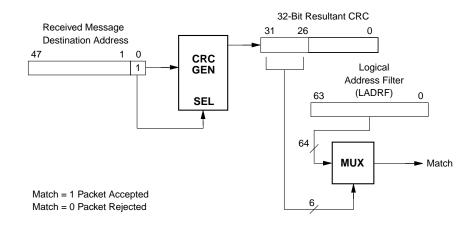

| SWITCHING CHARACTERISTICS: BUS INTERFACE                        |                                 |

|                                                                 |                                 |

| SWITCHING WAVEFORMS                                             |                                 |

|                                                                 |                                 |

|                                                                 |                                 |

|                                                                 |                                 |

|                                                                 |                                 |

|                                                                 |                                 |

| SWITCHING CHARACTERISTICS: MEDIA INDEPENDENT INTERFACE          |                                 |

| SWITCHING CHARACTERISTICS: EXTERNAL ADDRESS DETECTION INTERFACE |                                 |

|                                                                 |                                 |

| SWITCHING WAVEFORMS: EXTERNAL MEMORY INTERFACE                  |                                 |

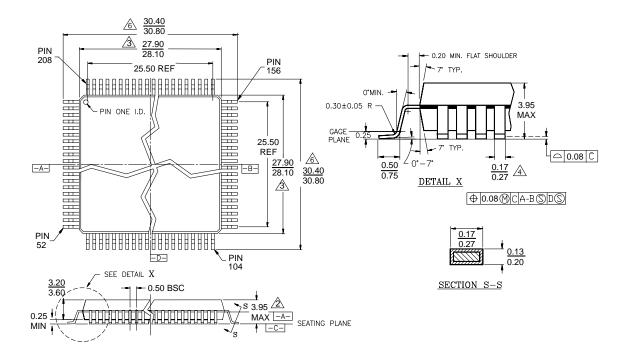

| PHYSICAL DIMENSIONS*                                            |                                 |

| PQFP208                                                         |                                 |

| Plastic Quad Flat Pack Trimmed and Formed                       |                                 |

| APPENDIX A: LOOK-AHEAD PACKET PROCESSING.                       |                                 |

|                                                                 |                                 |

| Outline of LAPP Flow.                                           |                                 |

| Setup                                                           |                                 |

| Flow                                                            |                                 |

| LAPP Software Requirements                                      |                                 |

| LAPP Rules for Parsing Descriptors                              |                                 |

| Some Examples of LAPP Descriptor Interaction                    |                                 |

| Buffer Size Tuning                                              |                                 |

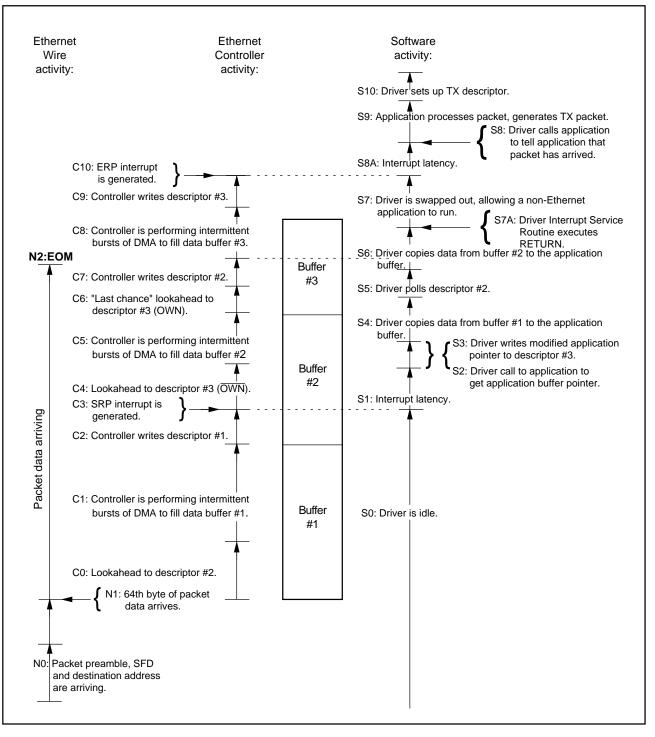

| An Alternative LAPP Flow: Two-Interrupt Method                  |                                 |

|                                                                 | B-1                             |

| Control Register (Register 0)                                   |                                 |

| Status Register (Register 1)                                    | B-1                             |

|                                                                 | B-1<br>B-2                      |

| Auto-Negotiation Advertisement Register (Register 4)            | B-1<br>B-2<br>B-3               |

| Technology Ability Field Bit Assignments                        | B-1<br>B-2<br>B-3<br>B-3        |

|                                                                 | B-1<br>B-2<br>B-3<br>B-3<br>B-4 |

## LIST OF FIGURES

| Figure 1:  | Slave Configuration Read                                      | 34  |

|------------|---------------------------------------------------------------|-----|

| Figure 2:  | Slave Configuration Write                                     | 34  |

| Figure 3:  | Slave Read Using I/O Command                                  |     |

| Figure 4:  | Slave Write Using Memory Command                              |     |

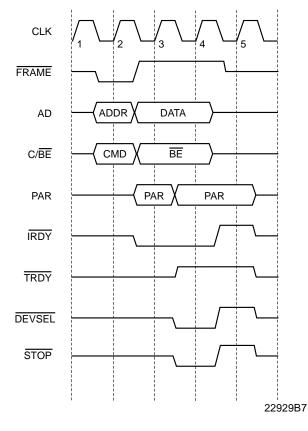

| Figure 5:  | Disconnect Of Slave Cycle When Busy                           |     |

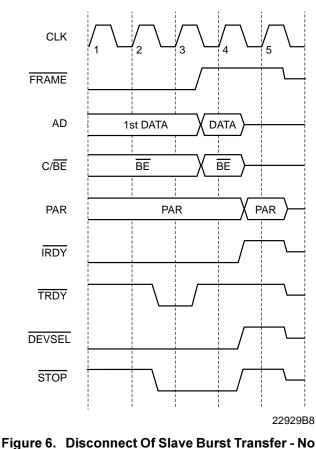

| Figure 6:  | Disconnect Of Slave Burst Transfer - No Host Wait States      |     |

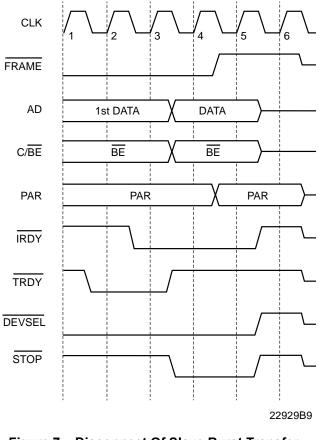

| Figure 7:  | Disconnect Of Slave Burst Transfer - Host Inserts Wait States |     |

| Figure 8:  | Address Parity Error Response                                 |     |

| Figure 9:  | Slave Cycle Data Parity Error Response                        |     |

| Figure 10: | Bus Acquisition                                               |     |

| Figure 11: | Non-Burst Read Transfer                                       |     |

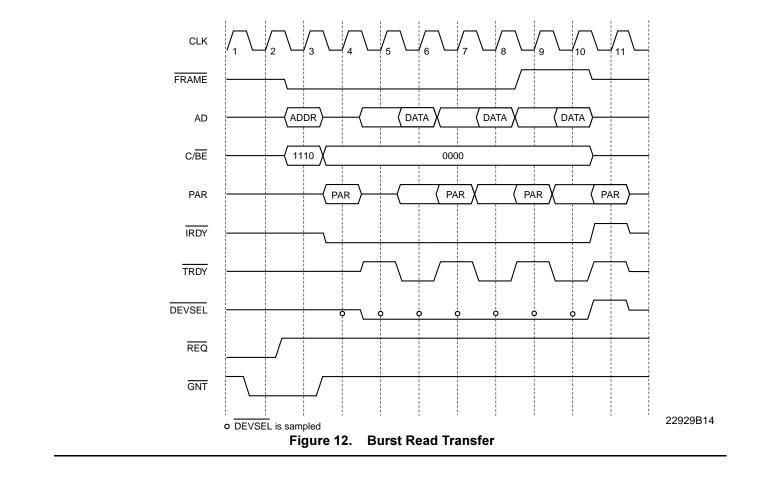

| Figure 12: | Burst Read Transfer                                           |     |

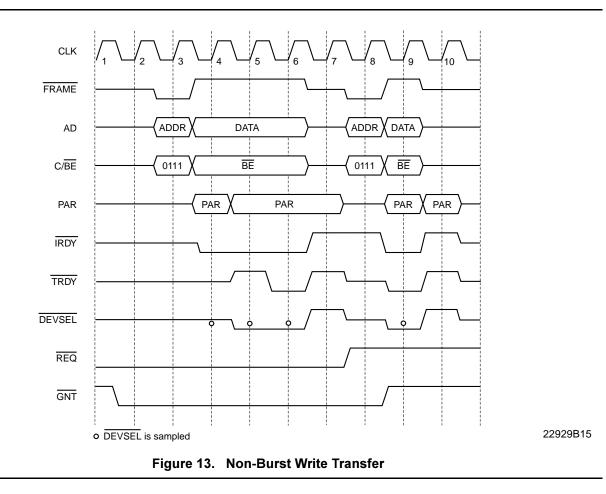

| Figure 13: | Non-Burst Write Transfer                                      |     |

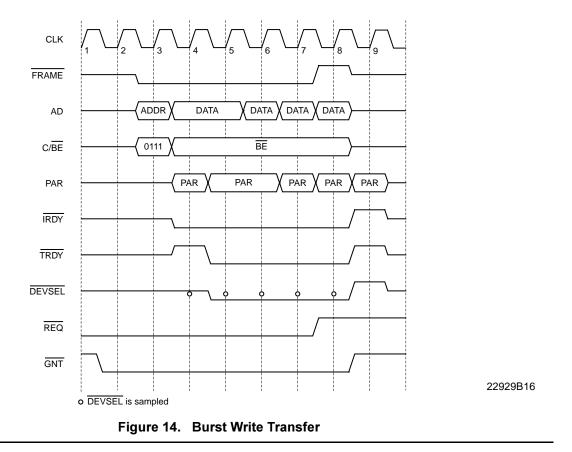

| Figure 14: | Burst Write Transfer                                          |     |

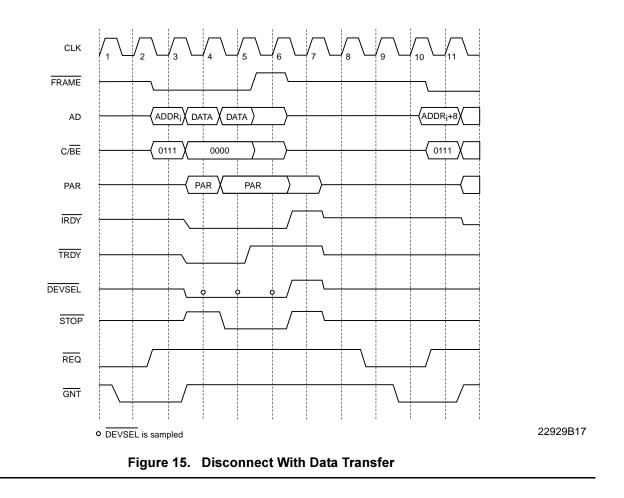

| Figure 15: | Disconnect With Data Transfer                                 |     |

| Figure 16: | Disconnect Without Data Transfer                              |     |

| Figure 17: | Target Abort                                                  |     |

| Figure 18: | Preemption During Non-Burst Transaction                       |     |

| •          |                                                               |     |

| Figure 19: | Preemption During Burst Transaction                           |     |

| Figure 20: |                                                               |     |

| Figure 21: | Master Cycle Data Parity Error Response                       |     |

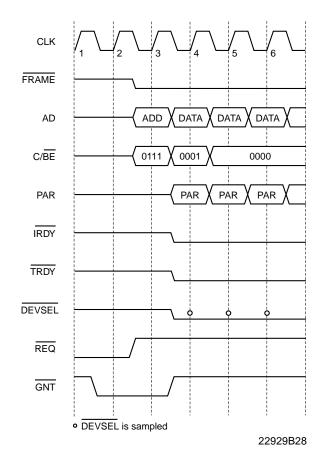

| Figure 22: | Descriptor Ring Read In Non-Burst Mode                        |     |

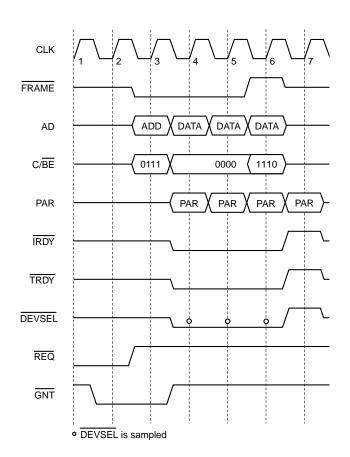

| Figure 23: | Descriptor Ring Read In Burst Mode                            |     |

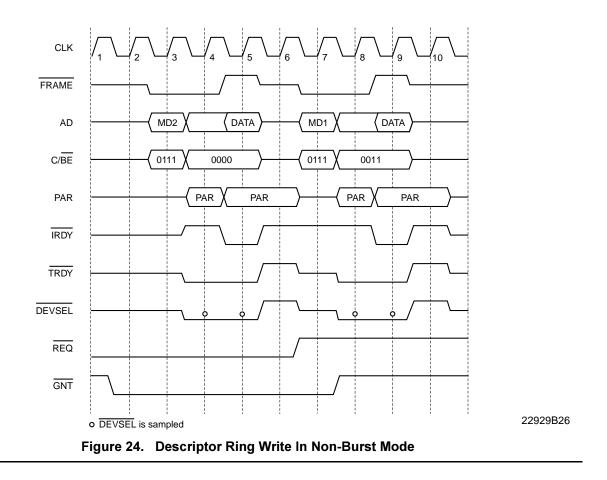

| Figure 24: | Descriptor Ring Write In Non-Burst Mode                       |     |

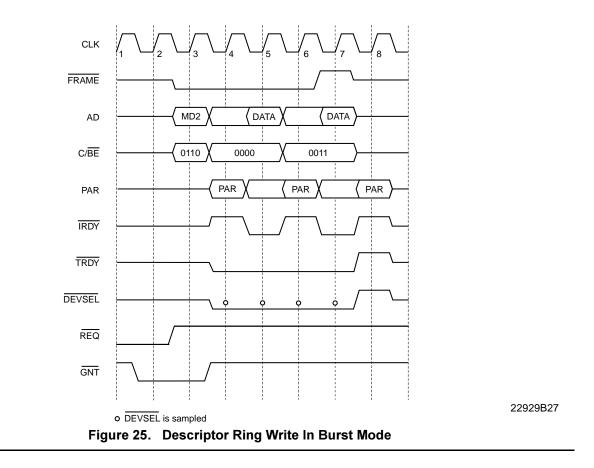

| Figure 25: | Descriptor Ring Write In Burst Mode                           |     |

| Figure 26: | FIFO Burst Write At Start Of Unaligned Buffer                 |     |

| Figure 27: | FIFO Burst Write At End Of Unaligned Buffer                   |     |

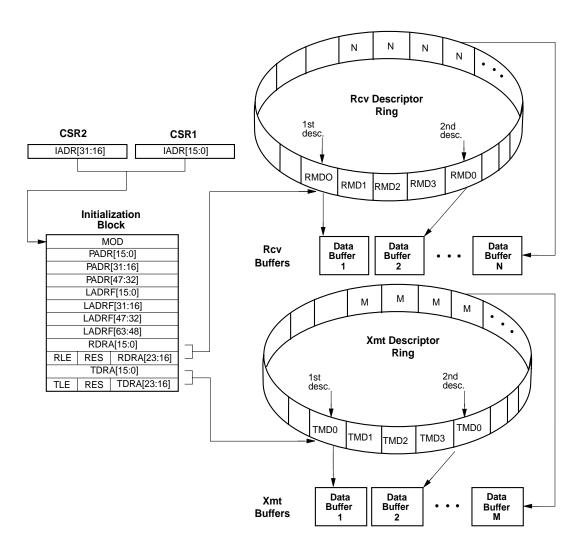

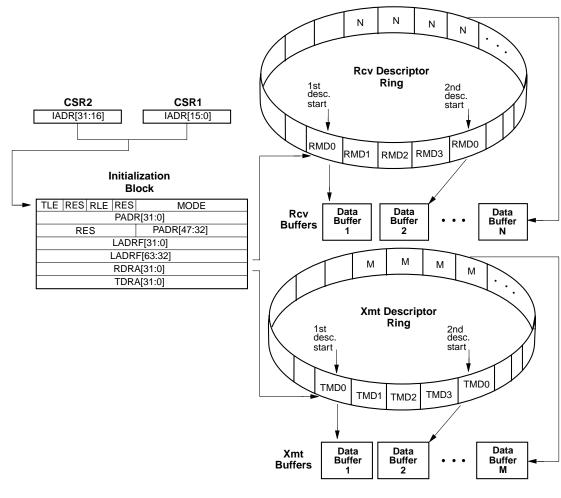

| Figure 28: | 16-Bit Software Model                                         |     |

| Figure 29: | 32-Bit Software Model                                         |     |

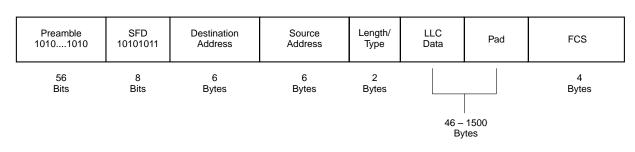

| Figure 30: | ISO 8802-3 (IEEE/ANSI 802.3) Data Frame                       |     |

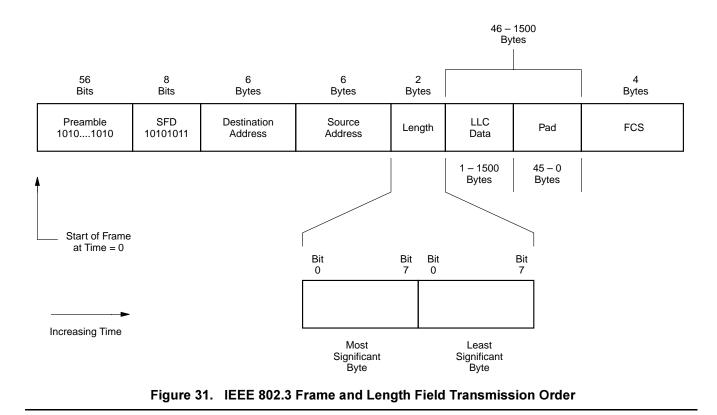

| Figure 31: | IEEE 802.3 Frame and Length Field Transmission Order          |     |

| Figure 32: | VLAN-Tagged Frame Format                                      | 79  |

| Figure 33: | Media Independent Interface                                   |     |

| Figure 34: | Frame Format at the MII Interface Connection                  |     |

| Figure 35: | MII Receive Frame Tagging                                     |     |

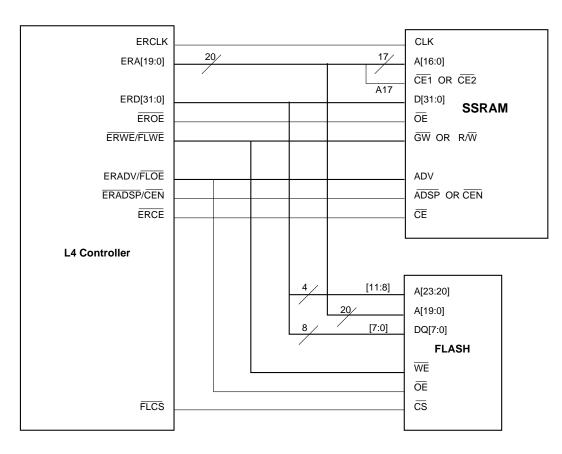

| Figure 36: | External SSRAM and Flash Configuration                        | 92  |

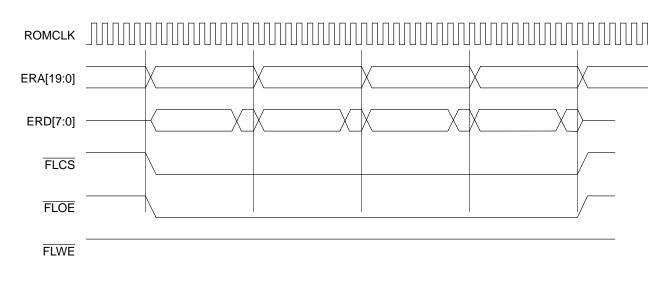

| Figure 37: | Expansion ROM Bus Read Sequence                               |     |

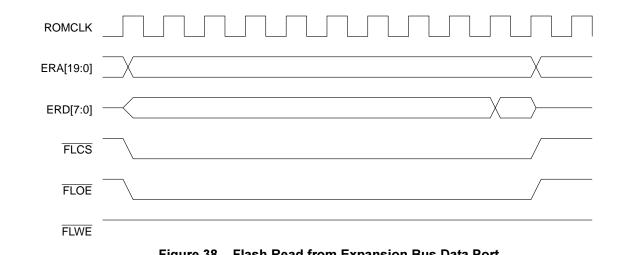

| Figure 38: | Flash Read from Expansion Bus Data Port                       | 95  |

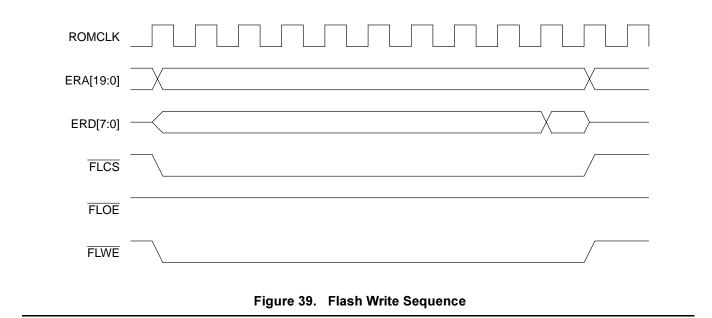

| Figure 39: | Flash Write Sequence                                          | 95  |

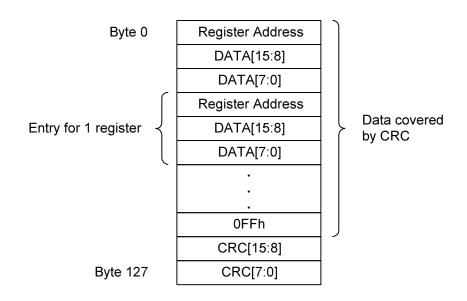

| Figure 40: | EEPROM Data Format                                            | 97  |

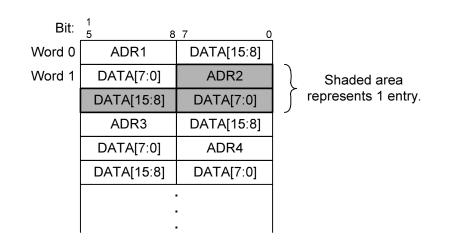

| Figure 41: | EEPROM Entry Positions                                        | 97  |

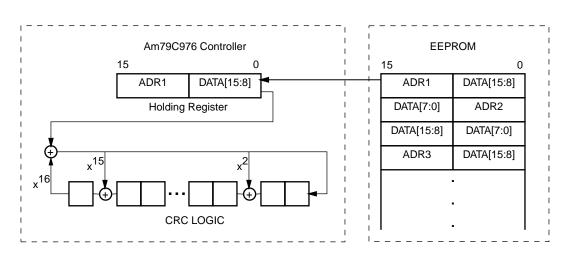

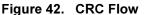

| Figure 42: | CRC Flow                                                      | 98  |

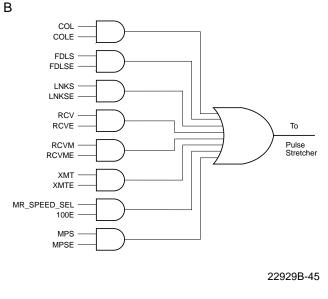

| Figure 43: | LED Control Logic                                             | 99  |

| Figure 44: | OnNow Functional Diagram                                      | 100 |

| Figure 45: | Pattern Match RAM                                             | 103 |

| Figure 46: | PCI Expansion ROM Base Address Register                       | 117 |

| Figure 47: | Address Match Logic                                           |     |

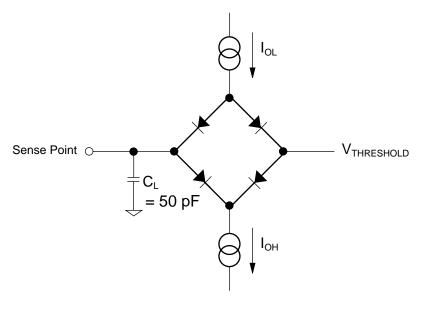

| Figure 48: | Normal and Tri-State Outputs                                  | 271 |

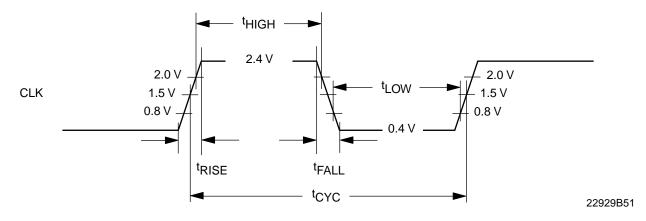

| Figure 49:  | CLK Waveform for 5 V Signaling                            |

|-------------|-----------------------------------------------------------|

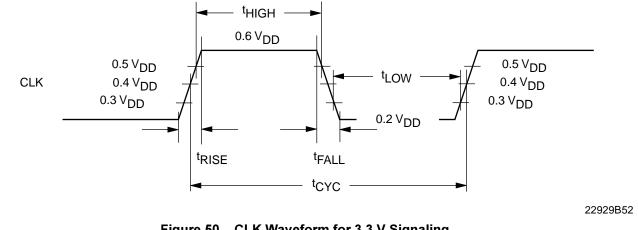

| Figure 50:  | CLK Waveform for 3.3 V Signaling                          |

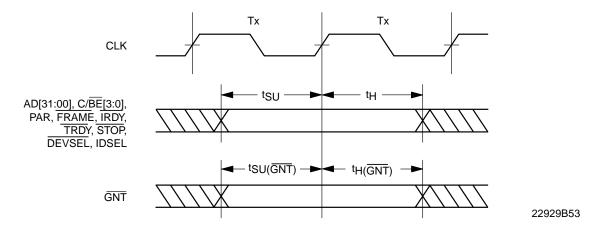

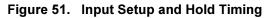

| Figure 51:  | Input Setup and Hold Timing                               |

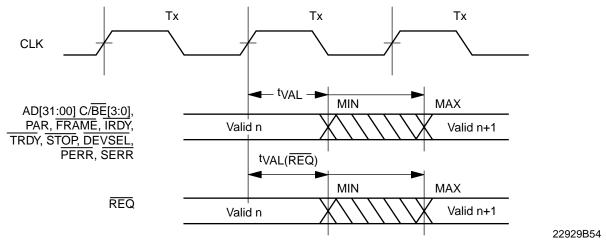

| Figure 52:  | Output Valid Delay Timing                                 |

| Figure 53:  | Output Tri-State Delay Timing                             |

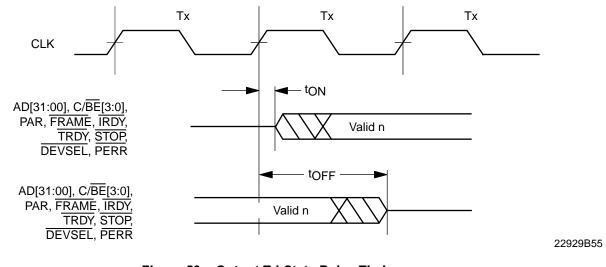

| Figure 54:  | EEPROM Read Functional Timing                             |

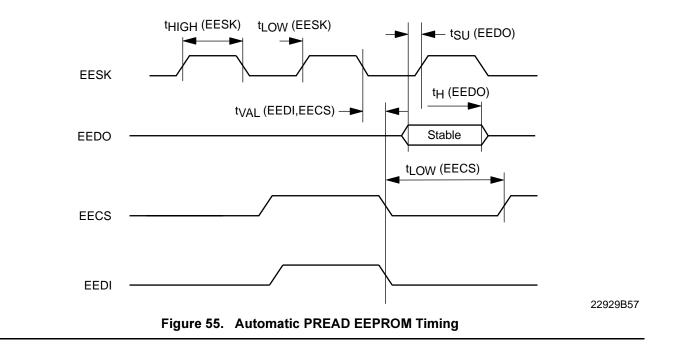

| Figure 55:  | Automatic PREAD EEPROM Timing                             |

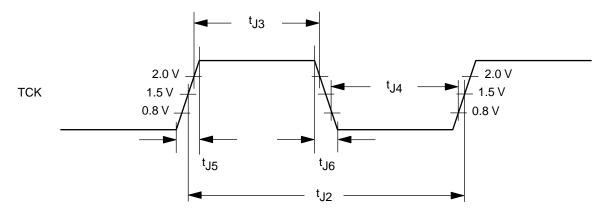

| Figure 56:  | JTAG (IEEE 1149.1) TCK Waveform for 5 V Signaling         |

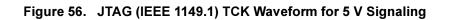

| Figure 57:  | JTAG (IEEE 1149.1) Test Signal Timing                     |

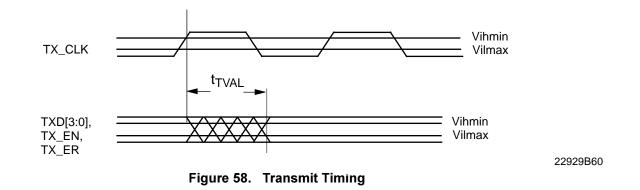

| Figure 58:  | Transmit Timing                                           |

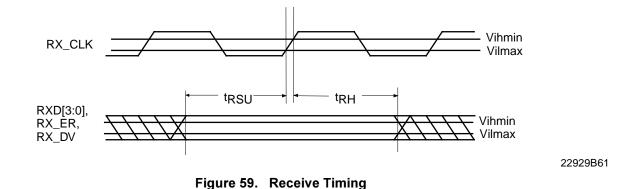

| Figure 59:  | Receive Timing                                            |

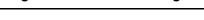

| Figure 60:  | MDC Waveform                                              |

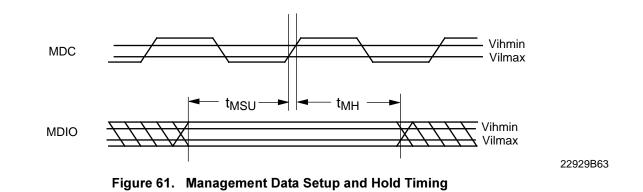

| Figure 61:  | Management Data Setup and Hold Timing                     |

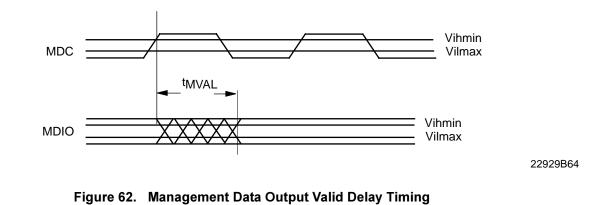

| Figure 62:  | Management Data Output Valid Delay Timing                 |

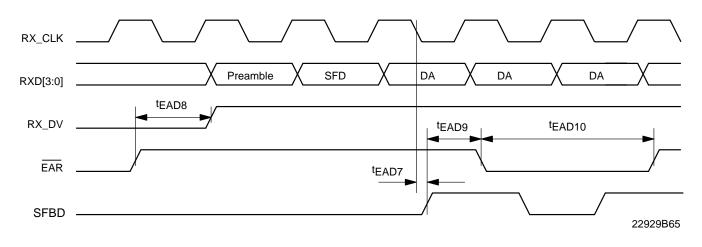

| Figure 63:  | Reject Timing - External PHY MII @ 25 MHz                 |

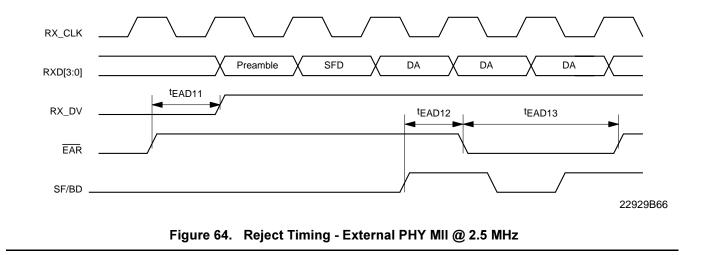

| Figure 64:  | Reject Timing - External PHY MII @ 2.5 MHz                |

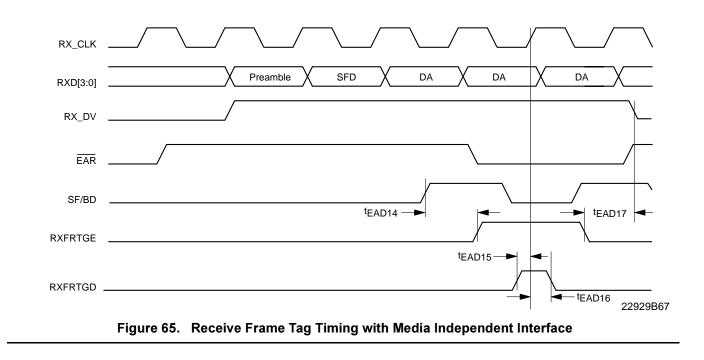

| Figure 65:  | Receive Frame Tag Timing with Media Independent Interface |

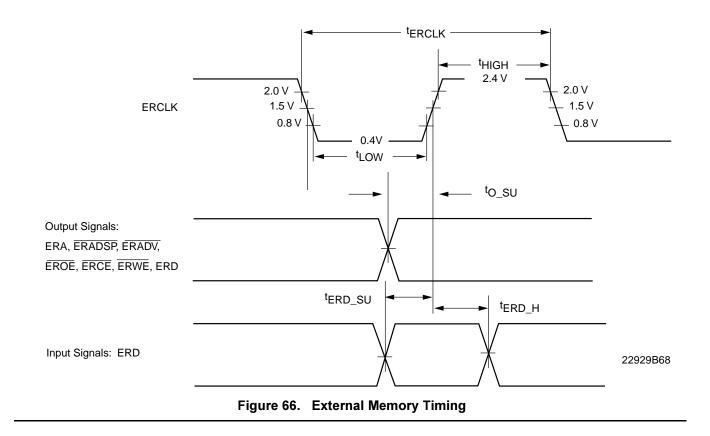

| Figure 66:  | External Memory Timing                                    |

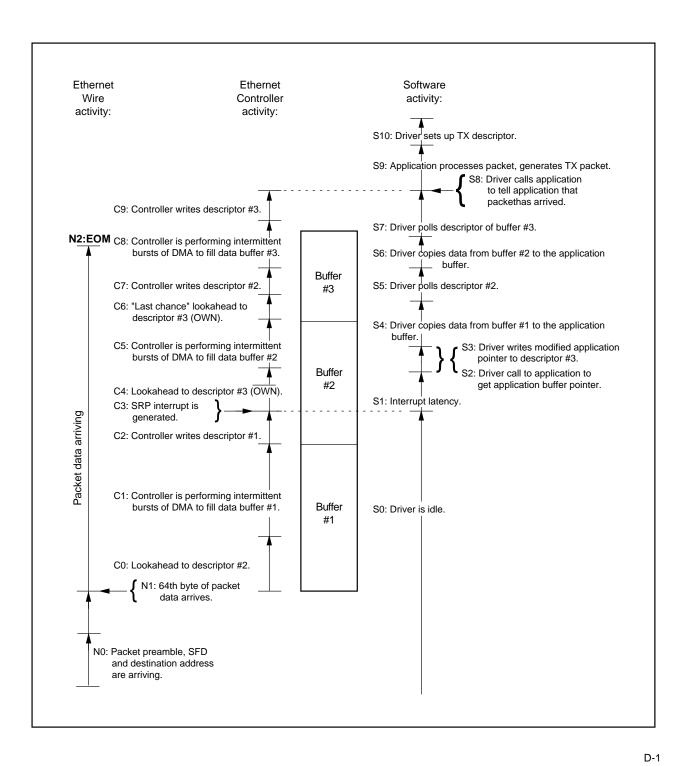

| Figure A-1: | LAPP Timeline                                             |

| Figure A-2: | LAPP 3 Buffer Grouping A-5                                |

| Figure A-3: | LAPP Timeline for Two-Interrupt Method A-9                |

| Figure A-4: | LAPP 3 Buffer Grouping for Two-Interrupt Method           |

## LIST OF TABLES

| Table 1:               | System Clock Selections                                                  | 27    |

|------------------------|--------------------------------------------------------------------------|-------|

| Table 2:               | Slave Commands                                                           |       |

| Table 3:               | PCI Commands                                                             | 41    |

| Table 4:               | Descriptor Read Sequence                                                 |       |

| Table 5:               | Descriptor Write Sequence                                                |       |

| Table 6:               | Receive Address Match                                                    |       |

| Table 7:               | Receive Statistics Counters                                              |       |

| Table 8:               | Transmit Statistics Counters                                             |       |

| Table 9:               | VLAN Tag Control Command                                                 |       |

| Table 10:              | VLAN Tag Type                                                            |       |

| Table 11:              | Auto-Negotiation Capabilities                                            |       |

| Table 12:              | MAC Control Pause Frame Format                                           |       |

| Table 13:              | FC Pin Functions                                                         |       |

| Table 14:              | FCCMD Bit Functions                                                      |       |

| Table 15:              | SRAM_TYPE Field Encoding                                                 |       |

| Table 16:              | LED Default Configuration                                                |       |

| Table 17:              | IEEE 1149.1 Supported Instruction Summary                                |       |

| Table 18:              | BSR Mode Of Operation                                                    | 104   |

| Table 19:              | Device ID Register                                                       |       |

| Table 19.              | PCI Configuration Space Layout                                           |       |

| Table 20:              | Address PROM Space Contents                                              |       |

| Table 21:              | I/O Map In Word I/O Mode (DWIO = 0)                                      |       |

| Table 22:<br>Table 23: |                                                                          |       |

|                        | Legal I/O Accesses in Word I/O Mode (DWIO = 0) $\dots \dots \dots \dots$ |       |

| Table 24:              | I/O Map In DWord I/O Mode (DWIO = 1)                                     |       |

| Table 25:              | Legal I/O Accesses in Double Word I/O Mode (DWIO =1)                     |       |

| Table 26:              | AP_VALUE0: Auto-Poll Value0 Register                                     |       |

| Table 27:              | AP_VALUE1: Auto-Poll Value1 Register                                     |       |

| Table 28:              | AP_VALUE2: Auto-Poll Value2 Register                                     |       |

| Table 29:              | AP_VALUE3: Auto-Poll Value3 Register                                     |       |

| Table 30:              | AP_VALUE4: Auto-Poll Value4 Register                                     |       |

| Table 31:              | AP_VALUE5: Auto-Poll Value5 Register                                     |       |

| Table 32:              | AUTOPOLLO: Auto-Pollo Register                                           |       |

| Table 33:              | AUTOPOLL1: Auto-Poll1 Register                                           |       |

| Table 34:              | AUTOPOLL2: Auto-Poll2 Register                                           |       |

| Table 35:              | AUTOPOLL3: Auto-Poll3 Register                                           |       |

| Table 36:              | AUTOPOLL4: Auto-Poll4 Register                                           |       |

| Table 37:              | AUTOPOLL5: Auto-Poll5 Register                                           | -     |

| Table 38:              | Receive Ring Base Address Register                                       |       |

| Table 39:              | Transmit Ring Base Address Register                                      |       |

| Table 40:              | CHIPID: Chip ID Register                                                 |       |

| Table 41:              | CHPOLLTIME: Chain Polling Interval Register                              |       |

| Table 42:              | CMD0: Command0 Register                                                  |       |

| Table 43:              | CMD2: Command2 Register                                                  | . 131 |

| Table 44:              | CMD3: Command3 Register                                                  | 135   |

| Table 45:              | CMD7: Command7 Register                                                  |       |

| Table 46:              | CTRL0: Control0 Register                                                 | 139   |

| Table 47:              | CTRL1: Control1 Register                                                 | 140   |

| Table 48:              | CTRL2: Control2 Register                                                 | 143   |

| Table 49:              | CTRL3: Control3 Register                             | 144 |

|------------------------|------------------------------------------------------|-----|

| Table 50:              | Software Styles                                      | 144 |

| Table 51:              | DATAMBIST: Memory Built-in Self-Test Access Register | 145 |

| Table 52:              | DELAYED_INT: Delayed Interrupts Register             | 147 |

| Table 53:              | EEPROM_ACC: EEPROM Access Register                   | 148 |

| Table 54:              | Interface Pin Assignment                             | 149 |

| Table 55:              | FLASH_ADDR: Flash Address Register                   | 150 |

| Table 56:              | FLASH_DATA: Flash Data Register                      | 150 |

| Table 57:              | FLOW: Flow Control Register                          | 151 |

| Table 58:              | IFS1: Inter-Frame Spacing Part 1 Register            | 152 |

| Table 59:              | INT0: Interrupt0 Register                            | 153 |

| Table 60:              | INTEN0: Interrupt0 Enable Register                   | 155 |

| Table 61:              | IPG: Inter-Packet Gap Register                       | 157 |

| Table 62:              | Logical Address Filter Register                      |     |

| Table 63:              | LED0 Control Register                                |     |

| Table 64:              | MAX_LAT_A: PCI Maximum Latency Alias Register        | 160 |

| Table 65:              | MIN_GNT_A: PCI Minimum Grant Alias Register          |     |

| Table 66:              | PADR: Physical Address Register                      |     |

| Table 67:              | PAUSE_CNT: Pause Count Register                      |     |

| Table 68:              | PCIDATA0: PCI DATA Register Zero Alias Register      |     |

| Table 69:              | PHY_ACCESS: PHY Access Register                      |     |

| Table 70:              | PMAT0: OnNow Pattern Register 0                      |     |

| Table 71:              | PMAT1: OnNow Pattern Register 1                      |     |

| Table 72:              | Receive Protect Register                             |     |

| Table 73:              | RCV_RING_LEN: Receive Ring Length Register           |     |

| Table 74:              | ROM_CFG: ROM Base Address Configuration Register     |     |

| Table 75:              | SID_A: PCI Subsystem ID Alias Register               |     |

| Table 76:              | SRAM Boundary Register                               |     |

| Table 77:              | SRAM Size Register                                   |     |

| Table 78:              | STAT0: Status0 Register                              |     |

| Table 79:              | Software Timer Value Register                        |     |

| Table 80:              | SVID: PCI Subsystem Vendor ID Shadow Register        |     |

| Table 81:              | TEST0: Test Register                                 |     |

| Table 82:              | VID_A: PCI Vendor ID Alias Register                  |     |

| Table 83:              | XMT_RING_LEN: Transmit Ring Length Register          |     |

| Table 84:              | XMTPOLLTIME: Transmit Polling Interval Register      |     |

| Table 85:              | Software Styles                                      |     |

| Table 86:              | Receive Watermark Programming                        |     |

| Table 87:              | Transmit Start Point Programming                     |     |

| Table 88:              | Transmit Watermark Programming                       |     |

| Table 89:              |                                                      |     |

| Table 90:              | EEDET Setting                                        |     |

| Table 91:              | Interface Pin Assignment                             |     |

| Table 92:              | Software Styles                                      |     |

| Table 93:              | SRAM_BND Programming                                 |     |

| Table 94:<br>Table 95: |                                                      |     |

| Table 95:<br>Table 96: | APDW Values                                          |     |

| Table 96:<br>Table 97: |                                                      |     |

|                        | Initialization Block (SSIZE32 = 1)                   | 223 |

| Table 98:  | R/TLEN Decoding (SSIZE32 = 0)                               | 226 |

|------------|-------------------------------------------------------------|-----|

| Table 99:  | R/TLEN Decoding (SSIZE32 = 1)                               | 226 |

| Table 100: | Receive Descriptor (SWSTYLE = 0)                            | 227 |

| Table 101: | Receive Descriptor (SWSTYLE = 2)                            | 227 |

| Table 102: | Receive Descriptor (SWSTYLE = 3)                            | 228 |

| Table 103: | Receive Descriptor (SWSTYLE = 4)                            | 228 |

| Table 104: | Receive Descriptor (SWSTYLE = 5)                            | 228 |

| Table 105: | Receive Descriptor, SWSTYLE = 0                             | 229 |

| Table 106: | Receive Descriptor, SWSTYLE = 2                             | 230 |

| Table 107: | Receive Descriptor, SWSTYLE = 3                             | 232 |

| Table 108: | Receive Descriptor, SWSTYLE = 4                             | 233 |

| Table 109: | Receive Descriptor, SWSTYLE = 5                             | 235 |

| Table 110: | Transmit Descriptor (SWSTYLE = 0)                           | 238 |

| Table 111: | Transmit Descriptor (SWSTYLE = 2)                           | 238 |

| Table 112: | Transmit Descriptor (SWSTYLE = 3)                           | 238 |

| Table 113: | Transmit Descriptor (SWSTYLE = 4)                           | 238 |

| Table 114: | Transmit Descriptor (SWSTYLE = 5)                           | 239 |

| Table 115: | Transmit Descriptor, SWSTYLE = 0                            |     |

| Table 116: | Transmit Descriptor, SWSTYLE = 2                            | 240 |

| Table 117: | Transmit Descriptor, SWSTYLE = 3                            | 241 |

| Table 118: | Transmit Descriptor, SWSTYLE = 4                            | 242 |

| Table 119: | Transmit Descriptor, SWSTYLE = 5                            | 243 |

| Table 120: | Register Bit Cross Reference                                | 253 |

| Table 121: | Control and Status Registers                                | 262 |

| Table 122: | Bus Configuration Registers                                 | 264 |

| Table B-1: | MII Management Register Set                                 | B-1 |

| Table B-2: | MII Management Control Register (Register 0)                | B-1 |

| Table B-3: | MII Management Status Register (Register 1)                 | B-2 |

| Table B-4: | Auto-Negotiation Advertisement Register (Register 4)        | B-3 |

| Table B-5: | Technology Ability Field Bit Assignments                    | B-3 |

| Table B-6: | Auto-Negotiation Link Partner Ability Register (Register 5) |     |

|            | - Base Page Format                                          | B-4 |

|            |                                                             |     |

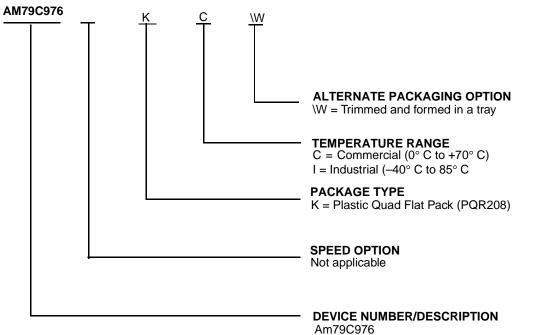

## **ORDERING INFORMATION**

## **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

PCnet-Pro 10/100 Mbps PCI Ethernet Controller

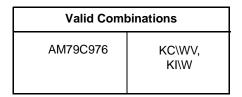

#### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

## **CONNECTION DIAGRAM (PQR208)**

## PIN DESIGNATIONS (PQR208)

## Listed By Pin Number

| Pin No. | Pin Name | Pin No. | Pin Name    | Pin No. | Pin Name    | Pin No. | Pin Name              |

|---------|----------|---------|-------------|---------|-------------|---------|-----------------------|

| 1       | AD30     | 53      | AD5         | 105     | ERD27       | 157     | TX_CLK                |

| 2       | AD29     | 54      | VDD         | 106     | VDD         | 158     | RX_ER                 |

| 3       | VDD      | 55      | AD4         | 107     | ERD26       | 159     | RX_CLK                |

| 4       | AD28     | 56      | AD3         | 108     | VSSB        | 160     | RX_DV                 |

| 5       | AD27     | 57      | VSSB        | 109     | ERCLK       | 161     | RXD0                  |

| 6       | AD26     | 58      | AD2         | 110     | ERD25       | 162     | VDD                   |

| 7       | VSSB     | 59      | AD1         | 111     | ERD24       | 163     | RXD1                  |

| 8       | AD25     | 60      | AD0         | 112     | ERD23       | 164     | VSSB                  |

| 9       | AD24     | 61      | ERCE        | 113     | VDD         | 165     | RXD2                  |

| 10      | C/BE3    | 62      | VDD         | 114     | ERD22       | 166     | RXD3                  |

| 11      | VDD      | 63      | EROE        | 115     | VSSB        | 167     | MDC                   |

| 12      | IDSEL    | 64      | VSSB        | 116     | ERD21       | 168     | MDIO                  |

| 13      | AD23     | 65      | ERWE/FLWE   | 117     | ERD20       | 169     | PHY_RST               |

| 14      | AD22     | 66      | ERADV/FLOE  | 118     | ERD19       | 170     | VAUX_SENSE            |

| 15      | VSSB     | 67      | ERADSP/CEN  | 119     | ERD18       | 171     | TEST                  |

| 16      | AD21     | 68      | VSS         | 120     | VDD         | 172     | CLKSEL0               |

| 17      | VSS      | 69      | FLCS        | 121     | ERD17       | 173     | CLKSEL1               |

| 18      | AD20     | 70      | VDD         | 122     | VSSB        | 174     | VSSB                  |

| 19      | AD19     | 71      | ERA0/FLA0   | 123     | VSS         | 175     | CLKSEL2               |

| 20      | VDD      | 72      | VSSB        | 124     | ERD16       | 176     | VSS                   |

| 21      | AD18     | 73      | ERA1/FLA1   | 125     | ERD15       | 177     | XTAL2                 |

| 22      | AD17     | 74      | ERA2/FLA2   | 126     | ERD14       | 178     | XTAL1                 |

| 23      | AD16     | 75      | ERA3/FLA3   | 127     | ERD13       | 179     | AVDD                  |

| 24      | VSSB     | 76      | ERA4/FLA4   | 128     | VDD         | 180     | XCLK                  |

| 25      | C/BE2    | 77      | VDD         | 129     | ERD12       | 181     | VDD                   |

| 26      | FRAME    | 78      | ERA5/FLA5   | 130     | VSSB        | 182     | LED3/EEDO/<br>RXFRTGD |

| 27      | IRDY     | 79      | VSSB        | 131     | ERD11/FLA23 | 183     | LED2/RXFRTGE          |

| 28      | VDD      | 80      | ERA6/FLA6   | 132     | ERD10/FLA22 | 184     | LED1/EESK             |

| 29      | TRDY     | 81      | ERA7/FLA7   | 133     | ERD9/FLA21  | 185     | LED0/EEDI             |

| 30      | DEVSEL   | 82      | ERA8/FLA8   | 134     | ERD8/FLA20  | 186     | EECS                  |

| 31      | STOP     | 83      | ERA9/FLA9   | 135     | VDD         | 187     | EAR                   |

| 32      | VSSB     | 84      | VDD         | 136     | ERD7/FLD7   | 188     | VSSB                  |

| 33      | PERR     | 85      | ERA10/FLA10 | 137     | VSSB        | 189     | VSS                   |

| 34      | VSS      | 86      | VSS         | 138     | VSS         | 190     | FC                    |

| Pin No. | Pin Name | Pin No. | Pin Name    | Pin No. | Pin Name  | Pin No. | Pin Name |

|---------|----------|---------|-------------|---------|-----------|---------|----------|

| 35      | SERR     | 87      | VSSB        | 139     | ERD6/FLD6 | 191     | VDD      |

| 36      | PAR      | 88      | ERA11/FLA11 | 140     | ERD5/FLD5 | 192     | PME      |

| 37      | VDD      | 89      | ERA12/FLA12 | 141     | ERD4/FLD4 | 193     | WUMI     |

| 38      | C/BE1    | 90      | ERA13/FLA13 | 142     | ERD3/FLD3 | 194     | RWU      |

| 39      | AD15     | 91      | ERA14/FLA14 | 143     | VDD       | 195     | ТСК      |

| 40      | AD14     | 92      | VDD         | 144     | ERD2/FLD2 | 196     | TMS      |

| 41      | VSSB     | 93      | ERA15/FLA15 | 145     | VSSB      | 197     | TDO      |

| 42      | AD13     | 94      | VSSB        | 146     | ERD1/FLD1 | 198     | TDI      |

| 43      | AD12     | 95      | ERA16/FLA16 | 147     | ERD0/FLD0 | 199     | VSSB     |

| 44      | AD11     | 96      | ERA17/FLA17 | 148     | CRS       | 200     | PG       |

| 45      | VDD      | 97      | ERA18/FLA18 | 149     | COL       | 201     | INTA     |

| 46      | AD10     | 98      | ERA19/FLA19 | 150     | VDD       | 202     | RST      |

| 47      | AD9      | 99      | VDD         | 151     | TXD3      | 203     | VDD      |

| 48      | AD8      | 100     | ERD31       | 152     | TXD2      | 204     | CLK      |

| 49      | VSSB     | 101     | VSSB        | 153     | VSSB      | 205     | GNT      |

| 50      | C/BE0    | 102     | ERD30       | 154     | TXD1      | 206     | REQ      |

| 51      | AD7      | 103     | ERD29       | 155     | TXD0      | 207     | VSSB     |

| 52      | AD6      | 104     | ERD28       | 156     | TX_EN     | 208     | AD31     |

## **PIN DESIGNATIONS**

## Listed By Group

| Pin Name          | Pin Function                 | Signal Type <sup>1</sup> | Pin Type <sup>1</sup> | No. of Pins |

|-------------------|------------------------------|--------------------------|-----------------------|-------------|

| Clock Interface   | i                            |                          | •                     |             |

| XTAL1             | Crystal                      | I                        | I                     | 1           |

| XTAL2             | Crystal                      | 0                        | 0                     | 1           |

| XCLK              | External Clock               | I                        | I                     | 1           |

| CLKSEL0           | Clock Select                 | I                        | I                     | 1           |

| CLKSEL1           | Clock Select                 | I                        | I                     | 1           |

| CLKSEL2           | Clock Select                 | I                        | I                     | 1           |

| TEST              | Test Select                  | I                        | I                     | 1           |

| PCI Bus Interface | i                            |                          | •                     |             |

| AD[31:0]          | Address/Data Bus             | IO                       | IO                    | 32          |

| C/BE[3:0]         | Bus Command/Byte Enable      | IO                       | IO                    | 4           |

| CLK               | Bus Clock                    | I                        | I                     | 1           |

| DEVSEL            | Device Select                | IO                       | IO                    | 1           |

| FRAME             | Cycle Frame                  | IO                       | IO                    | 1           |

| GNT               | Bus Grant                    | I                        | I                     | 1           |

| IDSEL             | Initialization Device Select | I                        | I                     | 1           |

| ĪNTĀ              | Interrupt                    | 0                        | TSO                   | 1           |

| IRDY              | Initiator Ready              | IO                       | IO                    | 1           |

| PAR               | Parity                       | IO                       | IO                    | 1           |

| PERR              | Parity Error                 | IO                       | IO                    | 1           |

| REQ               | Bus Request                  | 0                        | TSO                   | 1           |

| RST               | Reset                        | I                        | I                     | 1           |

| SERR              | System Error                 | IO                       | IO                    | 1           |

| STOP              | Stop                         | IO                       | IO                    | 1           |

| TRDY              | Target Ready                 | IO                       | IO                    | 1           |

| Board Interface   |                              |                          |                       |             |

| LED0              | LED0                         | 0                        | TSO                   | 1           |

| LED1              | LED1                         | 0                        | TSO                   | 1           |

| LED2              | LED2                         | 0                        | IO                    | 1           |

| LED3              | LED3                         | 0                        | ю                     | 1           |

| PHY_RST           | Reset to PHY                 | 0                        | 0                     | 1           |

| FC                | Flow Control                 | I                        | I                     | 1           |

| EEPROM Interface  |                              | ļ.                       | ł                     | <u>.</u>    |

| Pin Name                          | Pin Function                                                        | Signal Type <sup>1</sup> | Pin Type <sup>1</sup> | No. of Pins |

|-----------------------------------|---------------------------------------------------------------------|--------------------------|-----------------------|-------------|

| EECS                              | Serial EEPROM Chip Select                                           | 0                        | 0                     | 1           |

| EEDI                              | Serial EEPROM Data In                                               | 0                        | TSO                   | 1           |

| EEDO                              | Serial EEPROM Data Out                                              | I                        | IO                    | 1           |

| EESK                              | Serial EEPROM Clock                                                 | IO                       | TSO                   | 1           |

| External Memory Interface         | ·                                                                   |                          |                       |             |

| ERCLK                             | External Memory Clock                                               | 0                        | 0                     | 1           |

| ERA[19:0]/FLA[19:0]               | External Memory Address[19:0]                                       | 0                        | 0                     | 20          |

| ERD[31:0] / FLA[23:20] / FLD[7:0] | External Memory Data [31:0]/Flash<br>Address[23:20]/Flash Data[7:0] | Ю                        | Ю                     | 32          |

| ERADV/FLOE                        | External Memory Advance                                             | 0                        | 0                     | 1           |