# Diversity IF to Baseband GSM/EDGE Narrowband Receiver

### **Preliminary Technical Data**

**AD6650**

#### **FEATURES**

Digital VGA

I & Q Demodulators

Active Low Pass Filters

Dual Wideband ADC

Programmable Decimation and Channel Filters

Phase Locked Loop Circuitry

Serial Data Output Ports

IF Frequencies 70-300MHz

10 dB Noise Figure

+24 dBm Input IP2

-13 dBm Input IP3

3.3 Volt I/O and CMOS Core

I<sup>2</sup>C and Microprocessor Interface

JTAG Boundary Scan

#### **APPLICATIONS**

GSM/EDGE Single Carrier and Diversity Receivers Micro and Pico Cell Systems Wireless Local Loop Smart Antenna Systems Software Radios In Building Wireless Telephony

#### PRODUCT DESCRIPTION

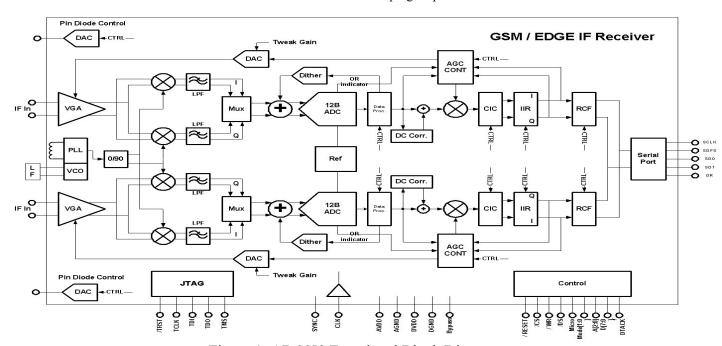

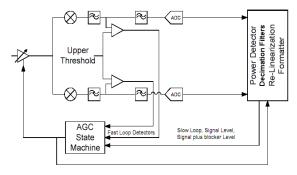

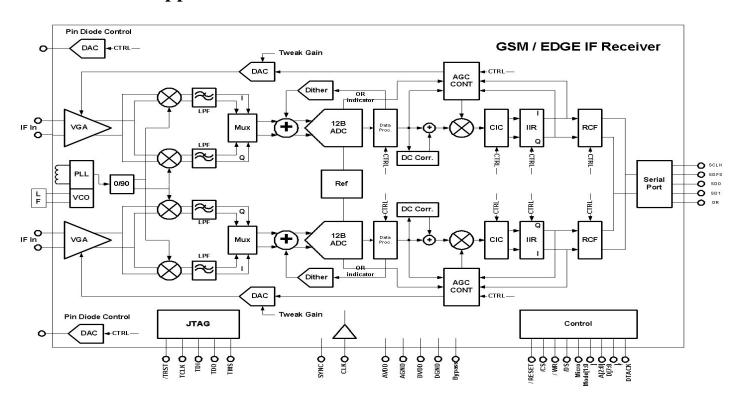

The AD6650 is a diversity, IF to baseband receiver for GSM/EDGE. This narrow band receiver consists of an integrated DVGA, IF-to-baseband I&Q demodulators, low-pass filtering, and a dual wideband ADC. The chip can accommodate IF input frequencies from 70 MHz to 300 MHz. This receiver architecture is designed such that only one external SAW filter(one for main and one for diversity) is required in the entire Rx signal path to meet GSM/EDGE blocking requirements.

Digital decimation and filtering circuitry is embedded on chip to generate serial output I&Q data streams. The decimating filters remove unwanted signals and noise outside the channel of interest. In addition, programmable RAM Coefficient filters allow anti-aliasing, matched filtering, and static equalization functions to be combined in a single, cost-effective filter.

The AD6650 is part of a complete GSM/EDGE receive and transmit chipset. Other components in this chipset are: RF to IF amplifier/mixers, receive and transmit frequency hopping synthesizers, and a baseband to IF transmit modulator and ramping chip.

Figure 1. AD6650 Functional Block Diagram

#### PrJ 02/27/03

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

### **AD6650**

| TABLE OF CONTENTS                                 |

|---------------------------------------------------|

| FEATURES                                          |

| PRODUCT DESCRIPTIONxx                             |

| FUNCTIONAL BLOCK DIAGRAM                          |

| SPECIFICATIONS/CHARACTERISTICS xx                 |

| TIMING DIAGRAMS xx                                |

| ABSOLUTE MAXIMUM RATINGS                          |

| PIN FUNCTION DESCRIPTIONS xx                      |

| ARCHITECTURE                                      |

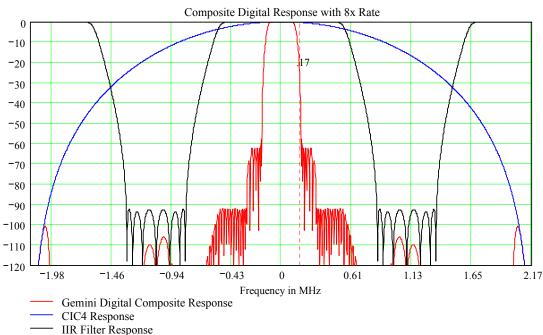

| EXAMPLE FILTER RESPONSE                           |

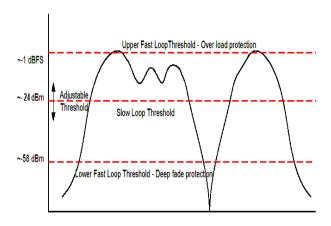

| AGC LOOPxx                                        |

| DC CORRECTIONxx                                   |

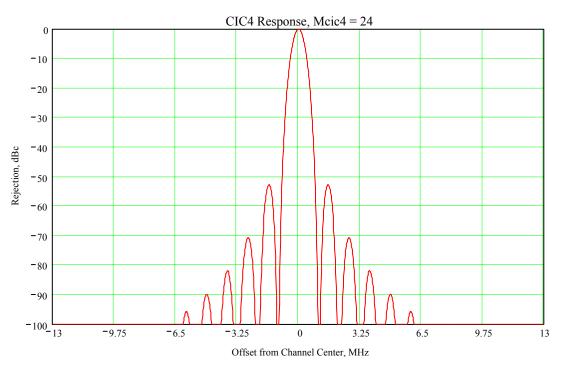

| FOURTH ORDER CASCADED INTEGRATOR COMB             |

| FILTER                                            |

| CIC4 Rejection xx                                 |

| INFINITE IMPULSE RESPONSE xx                      |

| RAM COEFFICIENT FILTER                            |

| RCF Decimation Register xx                        |

| RCF Decimation Phase xx                           |

| RCF Filter Lengthxx                               |

| RCF Output Scale Factor and Control Register . xx |

| USER-CONFIGURABLE BUILT-IN SELF-TEST              |

| CHANNEL BISTxx                                    |

| CHIP SYNCHRONIZATION                              |

| Start                                             |

| SERIAL OUTPUT DATA PORT                           |

| Serial Output Data Format xx                      |

| Serial Data Frame (Serial Bus Master) xx          |

| Serial Data Frame (Serial Cascade) xx             |

| Configuring the Serial Ports xx                   |

| Serial Port Data Rate xx                          |

| Serial Slave Operation xx                         |

| Serial Ports Cascaded xx                          |

| Serial Output Frame Timing (Master and Slave) xx  |

| Serial Port Timing Specifications xx              |

| SCLK                                              |

| SDO0                                              |

| SDO1 xx                                           |

| SDFS                                              |

| Serial Word Length xx                             |

| SDFS Mode                                         |

| Mapping RCF Data to the BIST Registers xx         |

| 0x00: Clock Divider Controlxx                     |

| 0x01-0x05: PLL Register[4:0]xx                    |

| 0x06: Clamp Controlxx                             |

| 0x07: Aux DAC A                    | xx |

|------------------------------------|----|

| 0x08: Aux DAC B                    | xx |

| 0x09: Aux DAC Control              |    |

| 0x0A: ADC Dither Control           |    |

| 0x0B: DC Correction BW             | XX |

| 0x0C: DC Correction Control        | xx |

| 0x0D-0x14: AGC Control[7:0]        |    |

| 0x15: Start Hold-Off Counter       |    |

| 0x16: CIC4 Decimation              |    |

| 0x17: CIC4 Scale                   | XX |

| 0x18: IIR Control Register         | XX |

| 0x19: RCF Decimation Register      | xx |

| 0x1A: RCF Decimation Phase         | xx |

| 0x1B: RCF Coefficient Offset       | xx |

| 0x1C: RCF Taps                     |    |

| 0x1D: RCF Scale Register           | XX |

| 0x1E-0x1F: BIST For A-I/Q          |    |

| 0x20-0x21: BIST for B-I/Q          | XX |

| 0x22: Serial Control Register      | xx |

| 0x23-0x29: Reserved                | xx |

| 0x30-0x5F: Coefficient Memory      |    |

| 0x60-0xFF: Reserved                | XX |

| MICROPORT CONTROL                  | XX |

| External Memory Map                | XX |

| Access Control Register (ACR)      | XX |

| External Memory Map                | XX |

| Channel Address Register (CAR)     | XX |

| SOFT_SYNC Control Register         | XX |

| PIN_SYNC Control Register          | XX |

| SLEEP Control Register             | XX |

| Data Address Registers             | XX |

| Write Sequencing                   |    |

| Read Sequencing                    |    |

| Read/Write Chaining                |    |

| Intel Nonmultiplexed Mode (INM)    |    |

| Motorola Nonmultiplexed Mode (MNM) | XX |

| I <sup>2</sup> C PORT CONTROL      |    |

| JTAG BOUNDARY SCAN                 | XX |

| INTERNAL WRITE ACCESS              |    |

| Write Pseudocode                   | XX |

| INTERNAL READ ACCESS               | XX |

| Read Pseudocode xx                 |    |

| OUTLINE DIMENSIONS                 | (  |

|                                    |    |

# **AC Specifications**

| The specifications              |      | Test  |      | AD6650BBC |      | 1      |

|---------------------------------|------|-------|------|-----------|------|--------|

| Parameter                       | Temp | Level | MIN  | Тур       | Max  | Units  |

| Overall Function                |      |       |      |           |      |        |

| Frequency Range                 |      |       | 70   |           | 300  | MHz    |

| Gain Control                    |      |       |      |           |      |        |

| Gain Step Size                  |      |       |      | .094      |      | dB     |

| Gain Step Accuracy              |      |       |      | +/5       |      | Step   |

| •                               |      |       |      |           |      |        |

| Baseband Filters                |      |       |      |           |      |        |

| Group Delay                     |      |       | 119  | 124       | 127  | ns     |

| Bandwidth                       |      |       | 3.36 | 3.5       | 3.64 | MHz    |

| LO Phase Noise: @ 200KHz Offset |      |       |      | -88       |      | dBc/Hz |

| @ 400KHz Offset                 |      |       |      | -108      |      | dBc/Hz |

| @ 600KHz Offset                 |      |       |      | -120      |      | dBc/Hz |

| @ 800KHz Offset                 |      |       |      | TBD       |      | dBc/Hz |

| @ 1600KHz Offset                |      |       |      | TBD       |      | dBc/Hz |

| @ 3000KHz Offset                |      |       |      | TBD       |      | dBc/Hz |

| F = 70  MHz                     |      |       |      |           |      |        |

| Min Gain                        |      |       |      | 0         |      | dB     |

| Max Gain                        |      |       |      | 36        |      | dB     |

| Noise Figure <sup>1</sup>       |      |       |      | 10.25     |      | dB     |

| Input IP2                       |      |       |      | +24       |      | dBm    |

| Input IP3                       |      |       |      | -13       |      | dBm    |

| Image Rejection                 |      |       |      | 35        |      | dBc    |

| FullScale Input Power           |      |       |      | +4        |      | dBm    |

| Input Impedance                 |      |       |      | 200+jx    |      | Ω      |

| E 150 MI                        |      |       |      |           |      |        |

| F = 150 MHz<br>Min Gain         |      |       |      | 0         |      | dB     |

| Max Gain                        |      |       |      | 36        |      | dB     |

| Noise Figure <sup>1</sup>       |      |       |      | 10.25     |      | dB     |

| Input IP2                       |      |       |      | +24       |      | dBm    |

| Input IP3                       |      |       |      | -13       |      | dBm    |

| Image Rejection                 |      |       |      | 35        |      | dBc    |

| FullScale Input Power           |      |       |      | +4        |      | dBm    |

| Input Impedance                 |      |       |      | 200+jx    |      | Ω      |

| E = 200 MHz                     |      |       |      |           |      |        |

| F = 200 MHz<br>Min Gain         |      |       |      | 0         |      | dB     |

| Max Gain                        |      |       |      | 36        |      | dB     |

| Noise Figure <sup>1</sup>       |      |       |      | 10.25     |      | dB     |

| Input IP2                       |      |       |      | +24       |      | dBm    |

| Input IP3                       |      |       |      | -13       |      | dBm    |

| Image Rejection                 |      |       |      | 35        |      | dBc    |

| FullScale Input Power           |      |       |      | +4        |      | dBm    |

| Input Impedance                 |      |       |      | 200+jx    |      | Ω      |

| F = 250 MHz                     |      |       |      | +         |      |        |

| Min Gain                        |      |       |      | 0         |      | dB     |

| Max Gain                        |      |       |      | 36        |      | dB     |

| Noise Figure <sup>1</sup>       |      |       |      | 10.25     |      | dB     |

| Input IP2                       |      |       |      | +24       |      | dBm    |

|                                 |      |       |      | - 4 1     |      | 4D111  |

**AD6650**

| Input IP3                 | -13    | dBm |

|---------------------------|--------|-----|

| Image Rejection           | 35     | dBc |

| FullScale Input Power     | +4     | dBm |

| Input Impedance           | 200+jx | Ω   |

|                           |        |     |

| F = 300  MHz              |        |     |

| Min Gain                  | 0      | dB  |

| Max Gain                  | 36     | dB  |

| Noise Figure <sup>1</sup> | 10.25  | dB  |

| Input IP2                 | +24    | dBm |

| Input IP3                 | -13    | dBm |

| Image Rejection           | 35     | dBc |

| FullScale Input Power     | +4     | dBm |

| Input Impedance           | 200+jx | Ω   |

|                           |        |     |

|                           |        |     |

<sup>&</sup>lt;sup>1</sup>This Measurement applies in Maximum Gain (+36 dB)

### **AD6650**

### **DIGITAL SPECIFICATIONS**

(TMIN to TMAX, AVDD, CLKVDD, DVDD = +3.3v, unless otherwise noted)

|                      |      | Test  |     | AD6650BBC |     |       |

|----------------------|------|-------|-----|-----------|-----|-------|

| Parameter            | Temp | Level | MIN | Тур       | Max | Units |

| VDD                  |      | IV    | 3.0 | 3.3       | 3.6 | V     |

| VDDIO                |      | IV    | 3.0 | 3.3       | 3.6 | V     |

| AVDD                 |      | IV    | 3.0 | 3.3       | 3.6 | V     |

| T <sub>AMBIENT</sub> |      | IV    | -40 | +25       | +85 | °C    |

#### **ELECTRICAL CHARACTERISTICS**

|                                             |       | Test  |         | AD6650BBC   |     |       |

|---------------------------------------------|-------|-------|---------|-------------|-----|-------|

| Parameter (Conditions)                      | Temp  | Level | Min     | Тур         | Max | Units |

| LOGIC INPUTS                                |       |       |         |             |     |       |

| Logic Compatibility                         | Full  |       |         | 3.3V CMOS   |     |       |

| Logic "1" Voltage                           |       |       | VDD-0.9 |             | VDD | V     |

| Logic "0" Voltage                           |       |       | 0       |             | 0.9 | V     |

| Logic "1" Current                           |       |       | -10     |             | +10 | μA    |

| Logic "0" Current                           |       |       | -10     |             | 10  | μA    |

| Input Capacitance                           |       |       |         | 5           |     | pF    |

| LOGIC OUTPUTS                               |       |       |         |             |     |       |

| Logic Compatibility                         | Full  |       |         | 3.3VCMOS/T7 | ΓL  |       |

| Logic "1" Voltage (I <sub>OH</sub> =0.25mA) | Full  | IV    | 2.4     | VDD-0.2     |     | V     |

| Logic "0" Voltage (I <sub>OL</sub> =0.25mA) | Full  | IV    |         | 0.2         | 0.4 | V     |

| IDD SUPPLY CURRENT                          |       |       |         |             |     |       |

| CLK=104 MHz (GSM Example)                   | +25°C | V     |         |             |     |       |

| $ m I_{VDD}$                                |       |       |         |             |     | mA    |

| $I_{ m VDDIO}$                              |       |       |         |             |     | mA    |

| I <sub>AVDD</sub>                           |       |       |         |             |     | mA    |

| POWER DISSIPATION                           |       |       |         |             |     |       |

| CLK=104 MHz GSM/EDGE Example                |       | V     |         | 1.2         |     | W     |

### **AD6650**

### **GENERAL TIMING CHARACTERISTICS**

|                   |                                                                    |      | Test  |      | AD6650               |      |       |

|-------------------|--------------------------------------------------------------------|------|-------|------|----------------------|------|-------|

|                   | (Conditions)                                                       | Temp | Level | Min  | Тур                  | Max  | Units |

| CLK Timing        | Requirements:                                                      |      |       |      |                      |      |       |

| $t_{CLK}$         | CLK Period                                                         | Full | I     | 9.6  |                      |      | ns    |

| $t_{CLKL}$        | CLK Width Low                                                      | Full | IV    |      | $0.5 \times t_{CLK}$ |      | ns    |

| t <sub>CLKH</sub> | CLK Width High                                                     | Full | IV    |      | $0.5 \times t_{CLK}$ |      | ns    |

| /RESET Tim        | ing Requirements:                                                  |      |       |      |                      |      |       |

| t <sub>RESL</sub> | /RESET Width Low                                                   | Full | IV    | 30   |                      |      | ns    |

|                   | g Requirements:                                                    |      |       |      |                      |      |       |

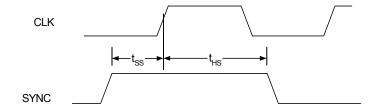

| $t_{SS}$          | SYNC to ↑CLK Setup Time                                            | Full | IV    |      |                      |      | ns    |

| $t_{HS}$          | SYNC to ↑CLK Hold Time                                             | Full | IV    |      |                      |      | ns    |

|                   | e Serial Port Timing Requirements (SBM=1):                         |      |       |      |                      |      |       |

| _                 | haracteristics <sup>2</sup>                                        |      |       |      |                      |      |       |

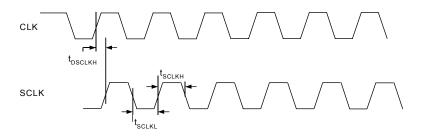

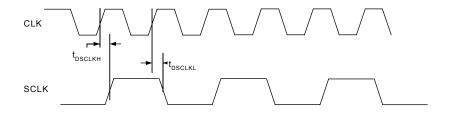

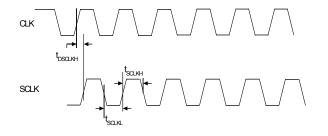

| $t_{DSCLK1}$      | ↑CLK to ↑SCLK Delay (divide by 1)                                  | Full | IV    | 3.9  |                      | 13.4 | ns    |

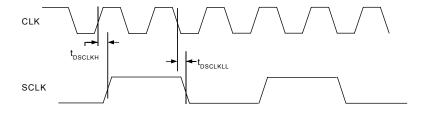

| $t_{DSCLKH}$      | ↑CLK to ↑SCLK Delay (for any other divisor)                        | Full | IV    | 4.4  |                      | 14.0 | ns    |

| $t_{DSCLKL}$      | $\uparrow$ CLK to $\downarrow$ SCLK Delay (divide by 2 or even #)  | Full | IV    | 3.25 |                      | 6.7  | ns    |

| $t_{DSCLKLL}$     | $\downarrow$ CLK to $\downarrow$ SCLK Delay (divide by 3 or odd #) | Full | IV    | 3.8  |                      | 6.9  | ns    |

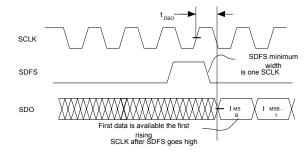

| $t_{DSDFS}$       | ↑SCLK to SDFS Delay                                                | Full | IV    |      | 3.02                 |      | ns    |

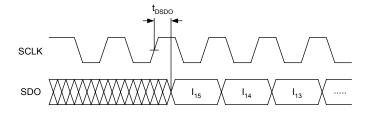

| $t_{ m DSDO}$     | ↑SCLK to SDO Delay                                                 | Full | IV    |      | 2.7                  |      | ns    |

| $t_{DSD1}$        | ↑SCLK to SD1 Delay                                                 | Full | IV    |      | 2.6                  |      | ns    |

| $t_{DSDR}$        | ↑SCLK to DR Delay                                                  | Full | IV    |      | 2.7                  |      | ns    |

| Slave Mode        | Serial Port Timing Requirements (SBM=0):                           |      |       |      |                      |      |       |

|                   | haracteristics <sup>2</sup>                                        |      |       |      |                      |      |       |

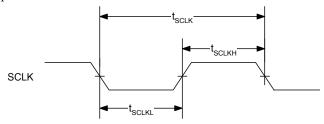

| $t_{ m SCLK}$     | SCLK Period                                                        | Full | IV    | 16.0 |                      |      | ns    |

| $t_{SCLKL}$       | SCLK low time (when SDIV=1, divide by 1)                           | Full | IV    | 5.0  |                      |      | ns    |

| $t_{SCLKH}$       | SCLK high time (when SDIV=1, divide by 1)                          | Full | IV    | 5.0  |                      |      | ns    |

| $t_{ m DSDO}$     | ↑SCLK to SDO Delay                                                 | Full | IV    |      | 6.8                  |      | ns    |

| $t_{DSD1}$        | ↑SCLK to SD1 Delay                                                 | Full | IV    |      | 6.8                  |      | ns    |

| $t_{DSDR}$        | ↑SCLK to DR Delay                                                  | Full | IV    |      | 6.9                  |      | ns    |

|                   | Input Characteristics                                              |      |       |      |                      |      |       |

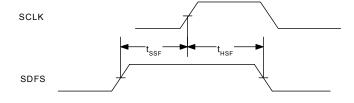

| $t_{SSF}$         | SDFS to ↑SCLK Setup Time                                           | Full | IV    |      | 2.6                  |      | ns    |

| $t_{HSF}$         | SDFS to ↑SCLK Hold Time                                            | Full | IV    |      | -1.15                |      | ns    |

|                   |                                                                    |      |       |      |                      |      |       |

|                   |                                                                    |      |       |      |                      |      |       |

|                   |                                                                    |      |       |      |                      |      |       |

<sup>&</sup>lt;sup>1</sup>All Timing Specifications valid over VDD range of 3.0V to 3.6V and VDDIO range of 3.0V to 3.6V.

<sup>&</sup>lt;sup>2</sup>The timing parameters for SCLK, SDFS, SDO0, SDO1, and DR apply to both channels (0, 1). The Slave serial port's (SCLK) operating frequency is limited to 52 MHz.

<sup>&</sup>lt;sup>3</sup>Specification pertains to control signals: RW, (/WR), /DS, (/RD), /CS

<sup>&</sup>lt;sup>4</sup>(C<sub>LOAD</sub>=40pF on all outputs unless otherwise specified)

### **AD6650**

### MICROPROCESSOR PORT TIMING CHARACTERISTICS<sup>1</sup>

|                                |                                                    |      | Test  | AD6650             |          |                    |       |

|--------------------------------|----------------------------------------------------|------|-------|--------------------|----------|--------------------|-------|

|                                |                                                    | Temp | Level | Min                | Тур      | Max                | Units |

| MICROPR                        | OCESSOR PORT, MODE INM (MODE=0)                    |      |       |                    |          |                    |       |

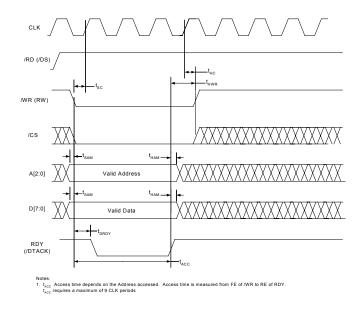

| MODE INM                       | Write Timing:                                      |      |       |                    |          |                    |       |

| $t_{SC}$                       | Control <sup>3</sup> to ↑CLK Setup Time            | Full | IV    | 5.5                |          |                    | ns    |

| $t_{HC}$                       | Control <sup>3</sup> to ↑CLK Hold Time             | Full | IV    | 1.0                |          |                    | ns    |

| $t_{HWR}$                      | /WR(RW) to RDY(/DTACK) Hold Time                   | Full | IV    | 8.0                |          |                    | ns    |

| $t_{SAM}$                      | Address/Data to /WR(RW) Setup Time                 | Full | IV    | -0.5               |          |                    | ns    |

| $t_{HAM}$                      | Address/Data to RDY(/DTACK) Hold Time              | Full | IV    | 7.0                |          |                    | ns    |

| $t_{\mathrm{DRDY}}$            | /WR(RW) to RDY(/DTACK) Delay                       | Full | IV    | 4.0                |          |                    | ns    |

| $t_{ACC}$                      | /WR(RW) to RDY(/DTACK) High Delay                  | Full | IV    | 4*t <sub>CLK</sub> |          | 5*t <sub>CLK</sub> | ns    |

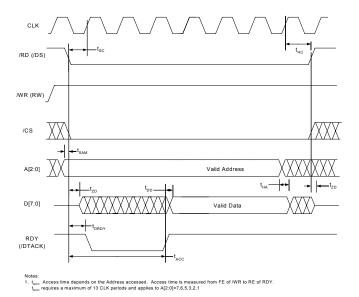

|                                | Read Timing:                                       |      |       |                    |          |                    |       |

| $t_{SC}$                       | Control <sup>3</sup> to ↑CLK Setup Time            | Full | IV    | 4.0                |          |                    | ns    |

| $t_{HC}$                       | Control <sup>3</sup> to ↑CLK Hold Time             | Full | IV    | 2.0                |          |                    | ns    |

| $t_{SAM}$                      | Address to /RD(/DS) Setup Time                     | Full | IV    | 0.0                |          |                    | ns    |

| $t_{HAM}$                      | Address to Data Hold Time                          | Full | IV    | 7.0                |          |                    | ns    |

| t <sub>ZD</sub>                | Data Tri-state Delay                               | Full | IV    |                    |          |                    | ns    |

| $t_{DD}$                       | RDY(/DTACK) to Data Delay                          | Full | IV    |                    |          |                    | ns    |

| $t_{DRDY}$                     | /RD(/DS) to RDY(/DTACK) Delay                      | Full | IV    | 4.0                |          |                    | ns    |

| $t_{ACC}$                      | /RD(/DS) to RDY(/DTACK) High Delay                 | Full | IV    | 4*t <sub>CLK</sub> |          | $7*t_{CLK}$        | ns    |

|                                | , , , , , , , , , , , , , , , , , , , ,            |      | Test  |                    |          |                    |       |

| MICROPR                        | OCESSOR PORT, MODE MNM (MODE=1)                    | Temp | Level | Min                | AD6650   | Max                | Units |

|                                |                                                    |      |       |                    | Тур      |                    |       |

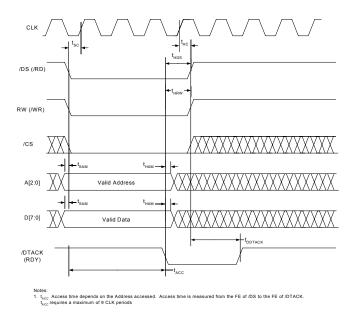

| MODE MN                        | M Write Timing:                                    |      |       |                    | <b>.</b> |                    |       |

| $t_{SC}$                       | Control <sup>3</sup> to ↑CLK Setup Time            | Full | IV    | 5.5                |          |                    | ns    |

| $t_{HC}$                       | Control <sup>3</sup> to ↑CLK Hold Time             | Full | IV    | 1.0                |          |                    | ns    |

| $t_{HDS}$                      | /DS(/RD) to /DTACK(RDY) Hold Time                  | Full | IV    | 8.0                |          |                    | ns    |

| $t_{HRW}$                      | RW(/WR) to /DTACK(RDY) Hold Time                   | Full | IV    | 8.0                |          |                    | ns    |

| $t_{SAM}$                      | Address/Data To RW(/WR) Setup Time                 | Full | IV    | -0.5               |          |                    | ns    |

| $t_{HAM}$                      | Address/Data to RW(/WR) Hold Time                  | Full | IV    | 7.0                |          |                    | ns    |

| $t_{\rm DDTACK}$               | /DS(/RD) to /DTACK(RDY) Delay                      | Full | IV    |                    |          |                    | ns    |

| $t_{ACC}$                      | RW(/WR) to /DTACK(RDY) Low Delay                   | Full | IV    | 4*t <sub>CLK</sub> |          | 5*t <sub>CLK</sub> | ns    |

|                                | M Read Timing:                                     |      |       |                    |          |                    |       |

| $t_{SC}$                       | Control <sup>3</sup> to ↑CLK Setup Time            | Full | IV    | 4.0                |          |                    | ns    |

| $t_{HC}$                       | Control <sup>3</sup> to ↑CLK Hold Time             | Full | IV    | 2.0                |          |                    | ns    |

| $t_{HDS}$                      | /DS(/RD) to /DTACK(RDY) Hold Time                  | Full | IV    | 8.0                |          |                    | ns    |

| $t_{SAM}$                      | Address to /DS(/RD) Setup Time                     | Full | IV    | 0.0                |          |                    | ns    |

| $t_{HAM}$                      | Address to Data Hold Time                          | Full | IV    | 7.0                |          |                    | ns    |

| $t_{ZD}$                       | Data Tri-State Delay                               | Full | IV    |                    |          |                    | ns    |

| $t_{\rm DD}$                   | /DTACK(RDY) to Data Delay                          | Full | IV    |                    |          |                    | ns    |

| t <sub>DDTACK</sub>            | /DS(/RD) to /DTACK(RDY) Delay                      | Full | IV    |                    |          |                    | ns    |

| t <sub>ACC</sub>               | /DS(/RD) to /DTACK(RDY) Low Delay                  | Full | IV    | 4*t <sub>CLK</sub> |          | 7*t <sub>CLK</sub> | ns    |

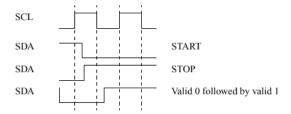

| MODE I <sup>2</sup> C          |                                                    |      |       | CLIK               |          | CLIC               |       |

| $t_{DSCL}$                     | ↑SCL to SDA Delay                                  | Full | IV    |                    | 61       |                    | ns    |

| t <sub>DSDA</sub>              | SDA to ↑SCL Delay                                  | Full | IV    |                    | 57       |                    | ns    |

| t <sub>SSCL</sub> <sup>5</sup> | ↑CLK to ↑SCL Delay                                 | Full | IV    |                    | 5        |                    | ns    |

| 1 11 m: :                      | Specifications valid over VDD range of 3 0V to 3 6 |      |       | 62.017             |          |                    | 1     |

<sup>&</sup>lt;sup>1</sup>All Timing Specifications valid over VDD range of 3.0V to 3.6V and VDDIO range of 3.0V to 3.6V.

<sup>&</sup>lt;sup>2</sup>The timing parameters for SCLK, SDFS, SDO0, SDO1, and DR apply to both channels (0, 1)

<sup>&</sup>lt;sup>3</sup>Specification pertains to control signals: RW, (/WR), /DS, (/RD), /CS <sup>4</sup>(C<sub>LOAD</sub>=40pF on all outputs unless otherwise specified)

<sup>&</sup>lt;sup>5</sup>There is no hold time for SDA because as this waits for a negative transition ( $\downarrow$ ) on SCL to transition.

### **TIMING DIAGRAMS**

Figure x. Reset Timing Requirements

Figure x. SCLK Switching Characteristics (Divide by 1)

Figure x. SCLK Switching Characteristics (Divide by 2 or EVEN integer)

Figure x. SCLK Switching Characteristics (Divide by 3 or ODD integer)

TIMING DIAGRAMS

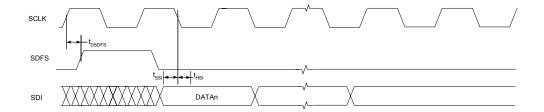

Figure x. Serial Port Switching Characteristics

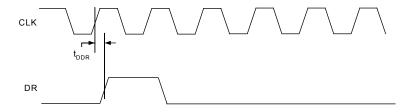

Figure x. CLK, DR Switching Characteristics

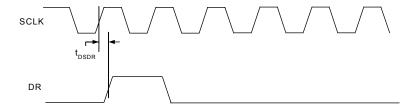

Figure x. SCLK, DR Switching Characteristics

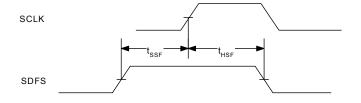

Figure x. SDFS Timing Requirements (SBM=0)

TIMING DIAGRAMS

Figure x. SYNC Timing Inputs

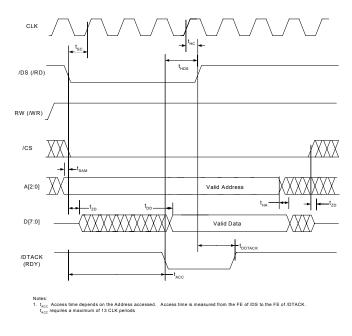

#### **TIMING DIAGRAMS – INM Microport Mode**

Figure 16. INM Microport Write Timing Requirements.

Figure 17. INM Microport Read Timing Requirements.

### **TIMING DIAGRAMS – MNM Microport Mode**

Figure x. MNM Microport Write Timing Requirements.

Figure x. MNM Microport Read Timing Requirements.

### **AD6650**

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage                  | 0.3V to 3.3v         |

|---------------------------------|----------------------|

| Input Voltage                   | 0.3 to 3.6V          |

| Output Voltage Swing            | -0.3V to VDDIO +0.3V |

| Load Capacitance                | 200pF                |

| Junction Temperature Under Bias | s+125°C              |

| Storage Temperature Range       | 65°C to +150°C       |

| Lead Temperature (5 sec)        | +280°C               |

| 3.T /                           |                      |

Notes

#### **Thermal Characteristics**

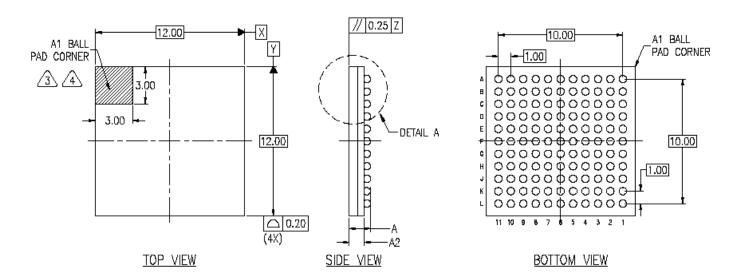

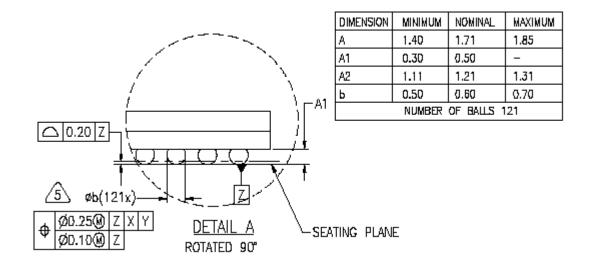

121-Pin Ball Grid Array:

$\theta_{JA}$ =28.1°C /Watt, no airflow

θ<sub>JA</sub>=XX°C/Watt, 200-lfpm airflow

Thermal measurements made in the horizontal position on a 4-layer board.

#### EXPLANATION OF TEST LEVELS

I 100% Production Tested.

II 100% Production Tested at 25°C, and Sampled Tested at Specified Temperatures.

III Sample Tested Only

IV Parameter Guaranteed by Design and Analysis

V Parameter is Typical Value Only

VI 100% Production Tested at 25°C, and Sampled Tested at Temperature Extremes

#### **ORDERING GUIDE**

| Model                  | Temperature Range        | Package Description                       | Package<br>Option |

|------------------------|--------------------------|-------------------------------------------|-------------------|

| AD6650BBC <sup>1</sup> | -40°C to +85°C (Ambient) | 121- Pin Ball Grid Array                  |                   |

| AD6650/PCB             |                          | Evaluation Board with AD6650 and Software |                   |

Notes

#### **ESD SENSITIVITY**

The AD6650 is an ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD6650 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>1</sup>Stresses greater than those listed above may cause permanent damage to the device These are stress ratings only; functional operation of the devices at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>&</sup>lt;sup>1</sup>X-Grade Material is Pre-Production material, normally shipped during product characterization and qualification.

# **Pin Configuration**

|   | 1    | 2      | 3     | 4     | 5        | 6    | 7    | 8      | 9    | 10    | 11   |   |

|---|------|--------|-------|-------|----------|------|------|--------|------|-------|------|---|

| Α | DGND | TDI    | TMS   | /TRST | /RESET   | DNC  | AVDD | CLK    | /CLK | AGND  | AGND | Α |

| В | SDFS | SCLK   | TDO   | TCLK  | SYNC     | DNC  | AVDD | AVDD   | AGND | AGND  | /BIN | В |

| С | SD1  | SD0    | DVDD  | DVDD  | DVDD     | DVDD | AVDD | AVDD   | AGND | AGND  | BIN  | С |

| D | D7   | DR     | DVDD  | DGND  | DGND     | DGND | AVDD | AVDD   | AGND | AGND  | AGND | D |

| Ε | D5   | D6     | DVDD  | DGND  | DGND     | DGND | AVDD | AVDD   | AGND | AGND  | LF   | E |

| F | D3   | D4     | DVDD  | DGND  | DGND     | DGND | AVDD | AVDD   | AGND | XVCOB | XVCO | F |

| G | D1   | D2     | DVDD  | DGND  | DGND     | DGND | AVDD | AVDD   | AGND | AGND  | CP   | G |

| Н | /DS  | D0     | DVDD  | DGND  | DGND     | DGND | AVDD | AVDD   | AGND | AGND  | AGND | Н |

| J | RW   | /DTACK | DVDD  | DVDD  | DVDD     | DVDD | AVDD | AVDD   | AGND | AGND  | AIN  | J |

| K | A2   | A1     | /CS   | MODE1 | CHIP_ID1 | DNC  | AVDD | REFGND | REFT | AGND  | /AIN | K |

| L | DGND | A0     | MODE2 | MODE0 | CHIP_ID0 | DNC  | AVDD | VREF   | REFB | AGND  | AGND | L |

|   | 1    | 2      | 3     | 4     | 5        | 6    | 7    | 8      | 9    | 10    | 11   |   |

Pin Function Descriptions

| Pin Function Desc         | <u> </u>       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | # of Pins |

|---------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                           | Туре           | runction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | # OI PINS |

| POWER SUPPLY              | T <sub>n</sub> | la avente de la constante de l |           |

| DVDD                      | P              | 3.3V Digital Core/IO Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13        |

| AVDD                      | P              | 3.3V Analog Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9         |

| DGND                      | G              | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17        |

| AGND                      | G              | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22        |

| INPUTS                    |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| /RESET                    | I              | Active Low Reset Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1         |

| SYNC                      | I              | Synchronizes Digital Filters and AGC loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1         |

| CHIP_ID[1:0]              | I              | Chip ID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2         |

| SERIAL DATA PO            | ORT            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |

| SCLK                      | I/O            | Bi-directional Serial Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1         |

| SDFS                      | I/O            | Bi-directional Serial Data Frame Sync                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1         |

| SD0                       | O/T            | Serial Data Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1         |

| SD1                       | O/T            | Serial Data Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1         |

| DR                        | O              | Output Data Ready Indicator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1         |

| <sup>1</sup> MICROPORT/SE | RIAL CONTRO    | DL .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |

| <sup>2</sup> D[7:0]       | I/O/T          | Bi-directional Microport Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8         |

| A[2:1]                    | I              | Microport Address Bits 2 and 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2         |