## Freescale Semiconductor Technical Data

## MM908E624 Internal Rev 4.0, 12/2004

## Integrated Triple High-Side Switch with Embedded MCU and LIN Serial Communication for Relay Drivers

The 908E624 is an integrated single-package solution that includes a high-performance HC08 microcontroller with a *SMARTMOS*<sup>™</sup> analog control IC. The HC08 includes flash memory, a timer, enhanced serial communications interface (ESCI), an analog-to-digital converter (ADC), serial peripheral interface (SPI) (only internal), and an internal clock generator module. The analog control die provides three high-side outputs with diagnostic functions, voltage regulator, watchdog, operational amplifier, and local interconnect network (LIN) physical layer.

The single-package solution, together with LIN, provides optimal application performance adjustments and space-saving PCB design. It is well suited for the control of automotive high-current motors applications using relays (e.g., window lifts, fans, and sun roofs).

## Features

- High-Performance M68HC908EY16 Core

- 16 K Bytes of On-Chip Flash Memory

- 512 Bytes of RAM

- Internal Clock Generator Module

- Two 16-Bit, 2-Channel Timers

- 10-Bit Analog-to-Digital Converter (ADC)

- LIN Physical Layer Interface

- Low Dropout Voltage Regulator

- Three High-Side Outputs

- Two Wake-Up Inputs

- 16 Microcontroller I/Os

## TRIPLE HIGH-SIDE SWITCH WITH EMBEDDED MCU AND LIN

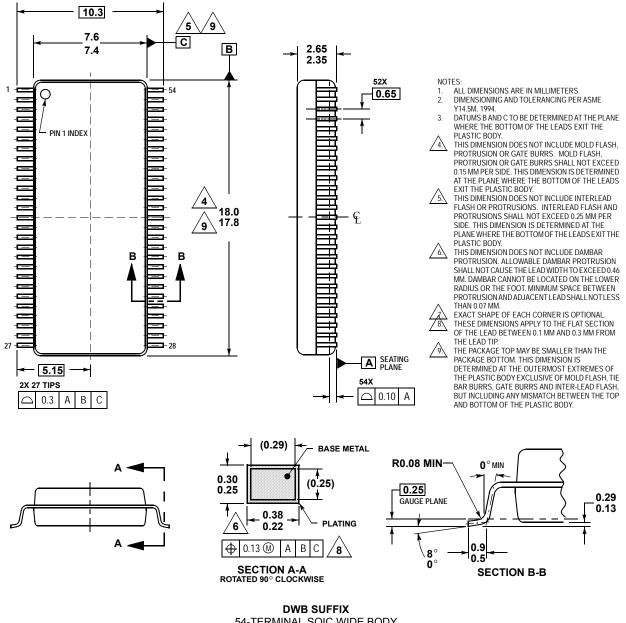

| ORDERING INFORMATION                          |               |          |  |  |  |

|-----------------------------------------------|---------------|----------|--|--|--|

| Device Temperature<br>Range (T <sub>A</sub> ) |               | Package  |  |  |  |

| MM908E624ACDWB/R                              | -40°C to 85°C | 54 SOICW |  |  |  |

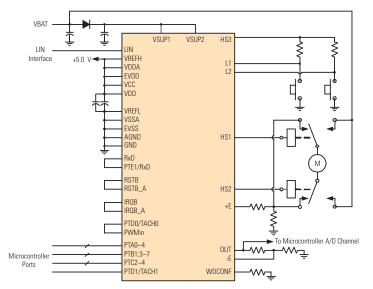

Figure 1. 908E624 Simplified Application Diagram

This document contains certain information on a new product. Specifications and information herein are subject to change without notice. © Freescale Semiconductor, Inc., 2004. All rights reserved.

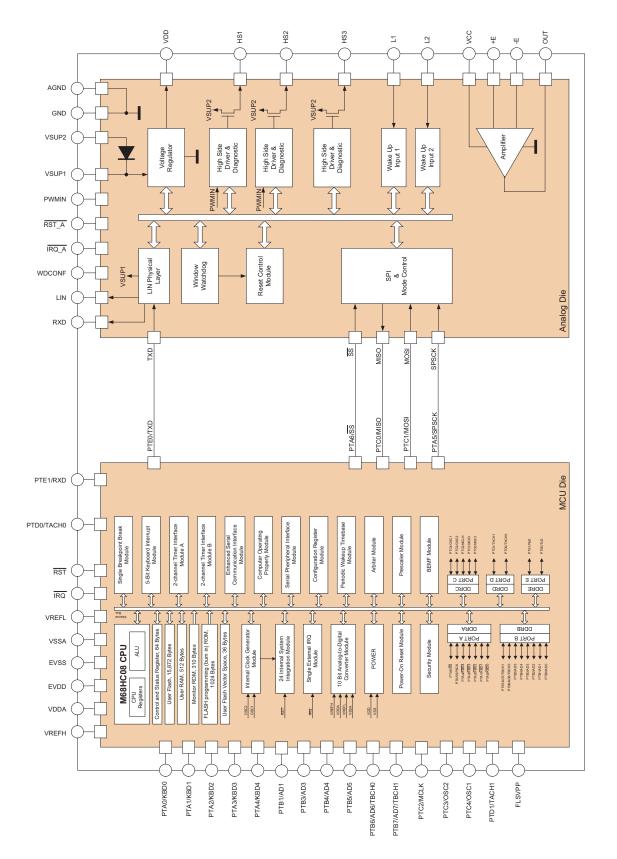

## INTERNAL BLOCK DIAGRAM

## 908E624

Figure 2. 908E624 Simplified Internal Block

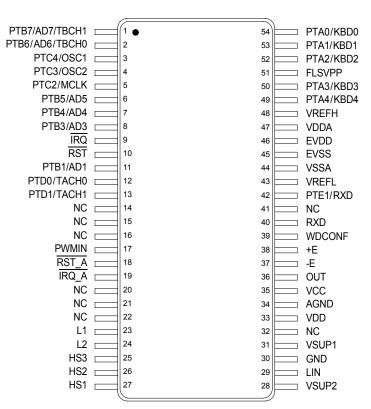

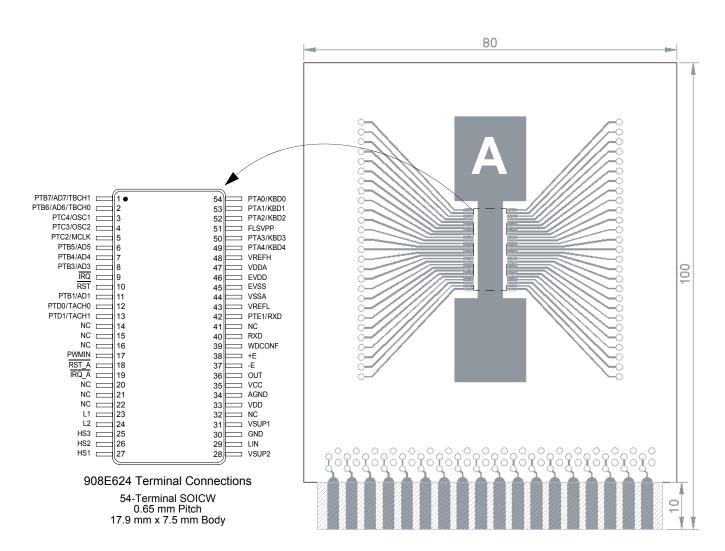

## **TERMINAL CONNECTIONS**

**Figure 3. Terminal Connections**

## Table 1. Terminal Definitions

A functional description of each terminal can be found in the Functional Terminal Description section beginning on page 17.

| Die | Terminal                             | Terminal Name                                                                    | Formal Name                 | Definition                                                                                                                          |

|-----|--------------------------------------|----------------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| MCU | 1<br>2<br>6<br>7<br>8<br>11          | PTB7/AD7/TBCH1<br>PTB6/AD6/TBCH0<br>PTB5/AD5<br>PTB4/AD4<br>PTB3/AD3<br>PTB1/AD1 | Port B I/Os                 | These terminals are special-function, bidirectional I/O port terminals that are shared with other functional modules in the MCU.    |

| MCU | 3<br>4<br>5                          | PTC4/OSC1<br>PTC3/OSC2<br>PTC2/MCLK                                              | Port C I/Os                 | These terminals are special-function, bidirectional I/O port terminals that are shared with other functional modules in the MCU.    |

| MCU | 9                                    | ĪRQ                                                                              | External Interrupt<br>Input | This terminal is an asynchronous external interrupt input terminal.                                                                 |

| MCU | 10                                   | RST                                                                              | External Reset              | This terminal is bidirectional, allowing a reset of the entire system. It is driven low when any internal reset source is asserted. |

| MCU | 12<br>13                             | PTD0/TACH0<br>PTD1/TACH1                                                         | Port D I/Os                 | These terminals are special-function, bidirectional I/O port terminals that are shared with other functional modules in the MCU.    |

| _   | 14, 15, 16,<br>20, 21, 22,<br>32, 41 | NC                                                                               | No Connect                  | Not connected.                                                                                                                      |

| MCU | 42                                   | PTE1/RXD                                                                         | Port E I/O                  | This terminal is a special-function, bidirectional I/O port terminal that can is shared with other functional modules in the MCU.   |

## Table 1. Terminal Definitions (continued)

A functional description of each terminal can be found in the Functional Terminal Description section beginning on page 17.

| Die    | Terminal                   | Terminal Name                                                 | Formal Name                           | Definition                                                                                                                       |

|--------|----------------------------|---------------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| MCU    | 43<br>48                   | VREFL<br>VREFH                                                | ADC References                        | These terminals are the reference voltage terminals for the analog-to-<br>digital converter (ADC).                               |

| MCU    | 44<br>47                   | VSSA<br>VDDA                                                  | ADC Supply<br>Terminals               | These terminals are the power supply terminals for the analog-to-digital converter.                                              |

| MCU    | 45<br>46                   | EVSS<br>EVDD                                                  | MCU Power Supply<br>Terminals         | These terminals are the ground and power supply terminals, respectively. The MCU operates from a single-power supply.            |

| MCU    | 49<br>50<br>52<br>53<br>54 | PTA4/KBD4<br>PTA3/KBD3<br>PTA2/KBD2<br>PTA1/KBD1<br>PTA0/KBD0 | Port A I/Os                           | These terminals are special-function, bidirectional I/O port terminals that are shared with other functional modules in the MCU. |

| MCU    | 51                         | FLSVPP                                                        | Test Terminal                         | For test purposes only. Do not connect in the application.                                                                       |

| Analog | 17                         | PWMIN                                                         | Direct High-Side<br>Control Input     | This terminal allows the enabling and PWM control of the high-side HS1 and HS2 terminals.                                        |

| Analog | 18                         | RST_A                                                         | Internal Reset Output                 | This terminal is the reset output terminal of the analog die.                                                                    |

| Analog | 19                         | IRQ_A                                                         | Internal Interrupt<br>Output          | This terminal is the interrupt output terminal of the analog die indicating errors or wake-up events.                            |

| Analog | 23<br>24                   | L1<br>L2                                                      | Wake-Up Inputs                        | These terminals are the wake-up inputs of the analog chip.                                                                       |

| Analog | 25<br>26<br>27             | HS3<br>HS2<br>HS1                                             | High-Side Output                      | These output terminals are low $R_{DS(ON)}$ high-side switches.                                                                  |

| Analog | 31<br>28                   | VSUP1<br>VSUP2                                                | Power Supply<br>Terminals             | These terminals are device power supply terminals.                                                                               |

| Analog | 29                         | LIN                                                           | LIN Bus                               | This terminal represents the single-wire bus transmitter and receiver.                                                           |

| Analog | 30<br>34                   | GND<br>AGND                                                   | Power Ground<br>Terminals             | These terminals are device power ground connections.                                                                             |

| Analog | 33                         | VDD                                                           | Voltage Regulator<br>Output           | The +5.0 V voltage regulator output terminal is intended to supply the embedded microcontroller.                                 |

| Analog | 35                         | VCC                                                           | Amplifier Power<br>Supply             | This terminal is the single +5.0 V power supply for the operational amplifier.                                                   |

| Analog | 36                         | OUT                                                           | Amplifier Output                      | This terminal is the output of the operational amplifier.                                                                        |

| Analog | 37<br>38                   | -E<br>+E                                                      | Amplifier Inputs                      | These terminals are the amplifier inverted and non-inverted inputs.                                                              |

| Analog | 39                         | WDCONF                                                        | Watchdog<br>Configuration<br>Terminal | This input terminal is for configuration of the watchdog period and allows the disabling of the watchdog.                        |

| Analog | 40                         | RXD                                                           | LIN Transceiver<br>Output             | This terminal is the output of LIN transceiver.                                                                                  |

## **MAXIMUM RATINGS**

## Table 2. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding limits on any terminal may cause permanent damage to the device.

| Rating                                                                                                                                                                                                  | Symbol                                                                         | Value                                                                        | Unit               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------|

| Electrical Ratings                                                                                                                                                                                      |                                                                                |                                                                              |                    |

| Supply Voltage<br>Analog Chip Supply Voltage under Normal Operation (Steady-State)<br>Analog Chip Supply Voltage under Transient Conditions<br>MCU Chip Supply Voltage                                  | V <sub>SUP(SS)</sub><br>V <sub>SUP(PK)</sub><br>V <sub>DD</sub>                | -0.3 to 27<br>-0.3 to 40<br>-0.3 to 5.5                                      | V                  |

| Input Terminal Voltage<br>Analog Chip<br>Microcontroller Chip                                                                                                                                           | V <sub>IN(ANALOG)</sub><br>V <sub>IN(MCU)</sub>                                | -0.3 to V <sub>DD</sub> +0.3<br>V <sub>SS</sub> -0.3 to V <sub>DD</sub> +0.3 | V                  |

| Maximum Microcontroller Current per Terminal<br>All Terminals except VDD, VSS, PTA0:PTA6, PTC0:PTC1<br>PTA0:PTA6, PTC0:PTC1 Terminals                                                                   | I <sub>PIN(1)</sub><br>I <sub>PIN(2)</sub>                                     | ±15<br>±25                                                                   | mA                 |

| Maximum Microcontroller VSS Output Current                                                                                                                                                              | I <sub>MVSS</sub>                                                              | 100                                                                          | mA                 |

| Maximum Microcontroller VDD Input Current                                                                                                                                                               | I <sub>MVDD</sub>                                                              | 100                                                                          | mA                 |

| Current Sense Amplifier<br>Maximum Input Voltage, +E, -E Terminals<br>Maximum Input Current, +E, -E Terminals<br>Maximum Output Voltage, OUT Terminal<br>Maximum Output Current, OUT Terminal           | V <sub>+E-E</sub><br>I <sub>+E-E</sub><br>V <sub>OUT</sub><br>I <sub>OUT</sub> | -0.3 to 7.0<br>±20<br>-0.3 to V <sub>CC</sub> +0.3<br>±20                    | V<br>mA<br>V<br>mA |

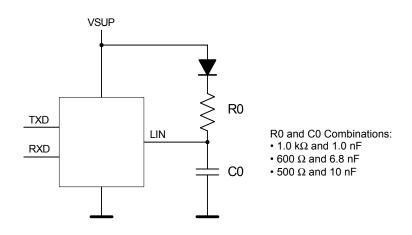

| LIN Supply Voltage<br>Normal Operation (Steady-State)<br>Transient Input Voltage (per ISO7637 Specification) and with<br>External Components ( <u>Figure 4</u> , page 15)                               | V <sub>BUS(SS)</sub><br>V <sub>BUS(PK)</sub>                                   | -18 to 40<br>-150 to 100                                                     | V                  |

| L1 and L2 Terminal Voltage<br>Normal Operation with a 33 kΩ resistor (Steady-State)<br>Transient Input Voltage (per ISO7637 Specification) and with<br>External Components ( <u>Figure 4</u> , page 15) | V <sub>WAKE(SS)</sub><br>V <sub>WAKE(PK)</sub>                                 | -18 to 40<br>-100 to 100                                                     | V                  |

| ESD Voltage<br>Human Body Model <sup>(1)</sup><br>Machine Model <sup>(2)</sup><br>Charge Device Model <sup>(3)</sup>                                                                                    | V <sub>ESD1</sub><br>V <sub>ESD2</sub><br>V <sub>ESD3</sub>                    | ±2000<br>±100<br>±500                                                        | V                  |

Notes

1. ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ).

2. ESD2 testing is performed in accordance with the Machine Model (C<sub>ZAP</sub> = 200 pF, R<sub>ZAP</sub> = 0  $\Omega$ ).

3. ESD3 testing is performed in accordance with Charge Device Model, Robotic ( $C_{ZAP}$  = 4.0 pF).

## Table 2. Maximum Ratings (continued)

All voltages are with respect to ground unless otherwise noted. Exceeding limits on any terminal may cause permanent damage to the device.

| Rating                                                                | Symbol                                         | Value                    | Unit     |

|-----------------------------------------------------------------------|------------------------------------------------|--------------------------|----------|

| Thermal Ratings                                                       |                                                |                          |          |

| Operating Ambient Temperature                                         | T <sub>A</sub>                                 | -40 to 85                | °C       |

| Operating Junction Temperature <sup>(4)</sup><br>Analog<br>MCU        | T <sub>J</sub> (ANALOG)<br>T <sub>J(MCU)</sub> | -40 to 150<br>-40 to 125 | °C<br>°C |

| Storage Temperature                                                   | T <sub>STG</sub>                               | -40 to 150               | °C       |

| Peak Package Reflow Temperature During Solder Mounting <sup>(5)</sup> | T <sub>SOLDER</sub>                            | 245                      | °C       |

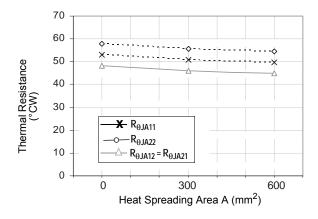

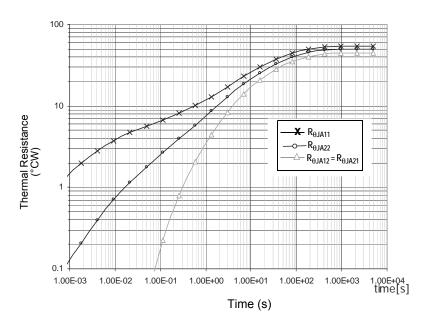

| Thermal Resistance, Junction to Ambient <sup>(6), (7)</sup>           | R <sub>θJA</sub>                               | 36                       | °C/W     |

Notes

4. Die temperature of analog and MCU is linked via the package. High temperature on analog die can lead to a high MCU temperature.

5. Terminal soldering temperature is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

6. All power outputs ON and dissipating equal power.

7. Per JEDEC JESD51-2 at natural convection, still air condition; and 2s2p thermal test board per JEDEC JESD51-7.

908E624

## STATIC ELECTRICAL CHARACTERISTICS

## **Table 3. Static Electrical Characteristics**

All characteristics are for the analog chip only. Refer to the 68HC908EY16 datasheet for characteristics of the microcontroller chip. Characteristics noted under conditions 9.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  16 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  125°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                                                                 | Symbol              | Min  | Тур | Мах  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-----|------|------|

| Supply Voltage Range                                                                                                                                           |                     |      |     |      | •    |

| Nominal Operating Voltage                                                                                                                                      | V <sub>SUP</sub>    | 5.5  |     | 18   | V    |

| Functional Operating Voltage <sup>(8)</sup>                                                                                                                    | V <sub>SUPOP</sub>  | _    | _   | 27   | V    |

| Supply Current Range                                                                                                                                           |                     | •    |     |      |      |

| Normal Mode <sup>(9)</sup>                                                                                                                                     | I <sub>RUN</sub>    |      |     |      | mA   |

| V <sub>SUP</sub> = 13.5 V, Analog Chip in Normal Mode, MCU Operating Using<br>Internal Oscillator at 32 MHz (8.0 MHz Bus Frequency), SPI, ESCI, ADC<br>Enabled | I <sub>STOP</sub>   | _    | 20  | _    |      |

| Stop Mode <sup>(9), (10)</sup>                                                                                                                                 |                     | _    | 60  | 75   | μA   |

| $V_{SUP} = 13.5 V$                                                                                                                                             | I <sub>SLEEP</sub>  |      |     |      |      |

| Sleep Mode <sup>(9), (10)</sup>                                                                                                                                |                     | _    | 35  | 45   | μA   |

| V <sub>SUP</sub> = 13.5 V                                                                                                                                      |                     |      |     |      |      |

| Digital Interface Ratings (Analog Die)                                                                                                                         |                     |      |     |      |      |

| Output Terminal RST_A                                                                                                                                          |                     |      |     |      |      |

| Low-State Output Voltage (I <sub>OUT</sub> = -1.5 mA)                                                                                                          | V <sub>OL</sub>     | —    | _   | 0.4  | V    |

| High-State Output Current (V <sub>OUT</sub> > 3.5 V)                                                                                                           | I <sub>ОН</sub>     | —    | 250 | —    | μA   |

| Pulldown Current Limitation                                                                                                                                    | I <sub>OL_MAX</sub> | -1.5 | —   | -8.0 | mA   |

| Output Terminal IRQ_A                                                                                                                                          |                     |      |     |      | V    |

| Low-State Output Voltage (I <sub>OUT</sub> = -1.5 mA)                                                                                                          | V <sub>OL</sub>     | —    | _   | 0.4  |      |

| High-State Output Voltage (I <sub>OUT</sub> = 250 μA)                                                                                                          | V <sub>OH</sub>     | 3.85 | —   | —    |      |

| Output Terminal RXD                                                                                                                                            |                     |      |     |      |      |

| Low-State Output Voltage (I <sub>OUT</sub> = -1.5 mA)                                                                                                          | V <sub>OL</sub>     | —    | _   | 0.4  | V    |

| High-State Output Voltage (I <sub>OUT</sub> = 250 μA)                                                                                                          | V <sub>OH</sub>     | 3.85 | _   | _    | V    |

| Capacitance <sup>(11)</sup>                                                                                                                                    | C <sub>IN</sub>     | —    | 4.0 | —    | pF   |

| Input Terminal PWMIN                                                                                                                                           |                     |      |     |      | 1    |

| Input Logic Low Voltage                                                                                                                                        | V <sub>IL</sub>     | _    | _   | 1.5  | V    |

| Input Logic High Voltage                                                                                                                                       | V <sub>IH</sub>     | 3.5  | —   | —    | V    |

| Input Current                                                                                                                                                  | I <sub>IN</sub>     | -10  | —   | 10   | μA   |

| Capacitance <sup>(11)</sup>                                                                                                                                    | C <sub>IN</sub>     | —    | 4.0 | —    | pF   |

| Terminal TXD, SS–Pullup Current                                                                                                                                | I <sub>PULLUP</sub> |      | 40  |      | μA   |

Notes

8. Device is fully functional. All functions are operating. Overtemperature may occur.

9. Total current (I<sub>VSUP1</sub> + I<sub>VSUP2</sub>) measured at GND terminal.

10. Stop and Sleep mode current will increase if  $V_{\mbox{\scriptsize SUP}}$  exceeds 15 V.

11. This parameter is guaranteed by process monitoring but is not production tested.

All characteristics are for the analog chip only. Refer to the 68HC908EY16 datasheet for characteristics of the microcontroller chip. Characteristics noted under conditions 9.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  16 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  125°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                         | Symbol               | Min  | Тур   | Мах  | Unit |

|------------------------------------------------------------------------|----------------------|------|-------|------|------|

| System Resets and Interrupts                                           | · · ·                |      |       |      |      |

| Low-Voltage Reset (LVR)                                                |                      |      |       |      | V    |

| Threshold                                                              | V <sub>LVRON</sub>   | 3.6  | 4.0   | 4.4  |      |

| Low-Voltage Interrupt (LVI)                                            |                      |      |       |      | V    |

| Threshold                                                              | V <sub>LVI</sub>     | 5.7  | 6.0   | 6.6  |      |

| Hysteresis                                                             | V <sub>LVI_HYS</sub> | —    | 1.0   | —    |      |

| High-Voltage Interrupt (HVI)                                           |                      |      |       |      |      |

| Threshold                                                              | V <sub>HVI</sub>     | 18   | 19.25 | 20.5 | V    |

| Hysteresis                                                             | V <sub>HVI_HYS</sub> | _    | 220   | —    | mV   |

| Voltage Regulator <sup>(12)</sup>                                      |                      |      |       |      |      |

| Normal Mode Output Voltage                                             | V <sub>DDRUN</sub>   |      |       |      | V    |

| 2.0 mA < I <sub>DD</sub> < 50 mA, 5.5 V < V <sub>SUP</sub> < 27 V      |                      | 4.75 | 5.0   | 5.25 |      |

| Normal Mode Output Current Limitation (13)                             | I <sub>DDRUN</sub>   | 50   | 110   | 200  | mA   |

| Dropout Voltage <sup>(14)</sup>                                        | V <sub>DDDROP</sub>  |      |       |      | V    |

| I <sub>DD</sub> = 50 mA                                                |                      | _    | 0.1   | 0.2  |      |

| Stop Mode Output Voltage <sup>(15)</sup>                               | V <sub>DDSTOP</sub>  | 4.75 | 5.0   | 5.25 | V    |

| Stop Mode Regulator Current Limitation                                 | IDDSTOP              | 4.0  | 8.0   | 14   | mA   |

| Line Regulation                                                        |                      |      |       |      | mV   |

| Normal Mode, 5.5 V < V <sub>SUP</sub> < 27 V, $I_{DD}$ = 10 mA         | LR <sub>RUN</sub>    | _    | 20    | 150  |      |

| Stop Mode, 5.5 V < V <sub>SUP</sub> < 27 V, I <sub>DD</sub> = 2.0 mA   | LR <sub>STOP</sub>   | —    | 10    | 100  |      |

| Load Regulation                                                        |                      |      |       |      | mV   |

| Normal Mode, 1.0 mA < I <sub>DD</sub> < 50 mA, V <sub>SUP</sub> = 18 V | LD <sub>RUN</sub>    | _    | 40    | 150  |      |

| Stop Mode, 1.0 mA < I $_{DD}$ < 5 mA, V $_{SUP}$ = 18 V                | LD <sub>STOP</sub>   | —    | 40    | 150  |      |

| Overtemperature Pre-Warning (Junction) (16)                            | T <sub>PRE</sub>     | 120  | 135   | 160  | °C   |

| Thermal Shutdown Temperature (Junction) (16)                           | T <sub>SD</sub>      | 155  | 170   |      | °C   |

| Temperature Threshold Difference                                       | $\Delta_{TSD}$ -TPRE |      |       |      | °C   |

| T <sub>SD</sub> -T <sub>PRE</sub>                                      |                      | 20   | 30    | 45   |      |

Notes

12. Specification with external capacitor 1.0  $\mu$ F < C < 10  $\mu$ F and 200 m $\Omega$   $\leq$  ESR  $\leq$  1.0  $\Omega$ . Capacitor value up to 47  $\mu$ F can be used.

13. Total VDD regulator current. A 5.0 mA current for operational amplifier is included. Digital output supplied from VDD.

14. Measured when voltage has dropped 100 mV below its nominal value.

15. When switching from Normal to Stop mode or from Stop mode to Normal mode, the output voltage can vary within the output voltage specification.

16. This parameter is guaranteed by process monitoring but not production tested

All characteristics are for the analog chip only. Refer to the 68HC908EY16 datasheet for characteristics of the microcontroller chip. Characteristics noted under conditions 9.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  16 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  125°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                | Symbol                        | Min                 | Тур | Max   | Unit             |

|-----------------------------------------------------------------------------------------------|-------------------------------|---------------------|-----|-------|------------------|

| Window Watchdog Configuration Terminal (WDCONF)                                               |                               |                     |     |       |                  |

| External Resistor Range                                                                       | R <sub>EXT</sub>              | 10                  | _   | 100   | kΩ               |

| Watchdog Period Accuracy with External Resistor (Excluding Resistor Accuracy) <sup>(17)</sup> | WD <sub>CACC</sub>            | -15                 | _   | 15    | %                |

| LIN Physical Layer                                                                            |                               |                     |     |       |                  |

| LIN Transceiver Output Level                                                                  |                               |                     |     |       | V                |

| Recessive State, TXD HIGH, I <sub>OUT</sub> = 1.0 μA                                          | V <sub>LIN_REC</sub>          | V <sub>SUP</sub> -1 | —   | —     |                  |

| Dominant State, TXD LOW, 500 $\Omega$ External Pullup Resistor                                | $V_{\text{LIN}_{\text{DOM}}}$ | —                   | —   | 1.4   |                  |

| Normal Mode Pullup Resistor to V <sub>SUP</sub>                                               | R <sub>PU</sub>               | 20                  | 30  | 60    | kΩ               |

| Stop, Sleep Mode Pullup Current Source                                                        | I <sub>PU</sub>               | _                   | 2.0 | _     | μA               |

| Output Current Shutdown Threshold                                                             | I <sub>OV-CUR</sub>           | 50                  | 75  | 150   | mA               |

| Output Current Shutdown Delay                                                                 | I <sub>OV-DELAY</sub>         | —                   | 10  | _     | μs               |

| Leakage Current to GND                                                                        | I <sub>BUS</sub>              |                     |     |       | μA               |

| VSUP Disconnected, V <sub>BUS</sub> at 18 V                                                   |                               | —                   | 1.0 | 10    |                  |

| Recessive State, $V_{SUP}$ 8.0 V to 18 V, $V_{BUS}$ 8.0 V to 18 V, $V_{BUS} \ge V_{SUP}$      |                               | 0                   | 3.0 | 20    |                  |

| GND Disconnected, $V_{GND} = V_{SUP}$ , $V_{BUS}$ at -18 V                                    |                               | -1.0                | —   | 1.0   |                  |

| LIN Receiver                                                                                  |                               |                     |     |       | V <sub>SUP</sub> |

| Receiver Threshold Dominant                                                                   | V <sub>BUS_DOM</sub>          | —                   | —   | 0.4   |                  |

| Receiver Threshold Recessive                                                                  | V <sub>BUS_REC</sub>          | 0.6                 | —   | —     |                  |

| Receiver Threshold Center                                                                     | V <sub>BUS_CNT</sub>          | 0.475               | 0.5 | 0.525 |                  |

| Receiver Threshold Hysteresis                                                                 | V <sub>BUS_HYS</sub>          | —                   | —   | 0.175 |                  |

Notes

17. Watchdog timing period calculation formula:  $P_{WD}$  = 0.991 \*  $R_{EXT}$ +0.648 ( $R_{EXT}$  in k $\Omega$  and  $P_{WD}$  in ms).

All characteristics are for the analog chip only. Refer to the 68HC908EY16 datasheet for characteristics of the microcontroller chip. Characteristics noted under conditions 9.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  16 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  125°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                               | Symbol              | Min  | Тур | Мах | Unit |

|------------------------------------------------------------------------------|---------------------|------|-----|-----|------|

| High-Side Outputs HS1 and HS2                                                |                     |      |     |     |      |

| Switch On Resistance                                                         | R <sub>DS(ON)</sub> |      |     |     | Ω    |

| $T_J$ = 25°C, I <sub>LOAD</sub> = 150 mA, V <sub>SUP</sub> > 9.0 V           |                     | —    | 2.0 | 2.5 |      |

| $T_J$ = 125°C, I <sub>LOAD</sub> = 150 mA, V <sub>SUP</sub> > 9.0 V          |                     | —    | —   | 4.5 |      |

| $T_{J}$ = 125°C, $I_{LOAD}$ = 120 mA, 5.5 V < $V_{SUP}$ > 9.0 V              |                     | —    | 3.0 | —   |      |

| Output Current Limit                                                         | I <sub>LIM</sub>    | 300  | —   | 600 | mA   |

| Overtemperature Shutdown <sup>(18),</sup> <sup>(19)</sup>                    | T <sub>HSSD</sub>   | 155  | —   | 190 | °C   |

| Leakage Current                                                              | I <sub>LEAK</sub>   | —    | —   | 10  | μΑ   |

| High-Side Output HS3                                                         | ·                   |      | ·   |     |      |

| Switch On Resistance                                                         | R <sub>DS(ON)</sub> |      |     |     | Ω    |

| $T_J$ = 25°C, I <sub>LOAD</sub> = 50 m A, V <sub>SUP</sub> > 9.0 V           |                     | _    | —   | 7.0 |      |

| $T_J$ = 125°C, I <sub>LOAD</sub> = 50 mA, V <sub>SUP</sub> > 9.0 V           |                     | —    | —   | 10  |      |

| $T_{J}$ = 125°C, I <sub>LOAD</sub> = 30 mA, 5.5 V < V <sub>SUP</sub> > 9.0 V |                     | —    | —   | 14  |      |

| Output Current Limitation                                                    | I <sub>LIM</sub>    | 60   | 100 | 200 | mA   |

| Overtemperature Shutdown <sup>(18),</sup> <sup>(19)</sup>                    | T <sub>HSSD</sub>   | 155  | —   | 190 | °C   |

| Leakage Current                                                              | I <sub>LEAK</sub>   | —    | —   | 10  | μA   |

| Output Clamp Voltage                                                         | V <sub>CL</sub>     |      |     |     | V    |

| I <sub>OUT</sub> = -100 mA                                                   |                     | -6.0 | —   | —   |      |

Notes

18. This parameter is guaranteed by process monitoring but it is not production tested

19. When overtemperature occurs, switch is turned off and latched off. Flag is set in SPI.

All characteristics are for the analog chip only. Refer to the 68HC908EY16 datasheet for characteristics of the microcontroller chip. Characteristics noted under conditions 9.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  16 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  125°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                 | Symbol            | Min  | Тур | Max                  | Unit |

|----------------------------------------------------------------|-------------------|------|-----|----------------------|------|

| Sense Current Amplifier                                        |                   |      |     | •                    |      |

| Rail to Rail Input Voltage                                     | V <sub>IMC</sub>  | -0.1 | —   | V <sub>CC</sub> +0.1 | V    |

| Output Voltage Range                                           |                   |      |     |                      | V    |

| Output Current ±1.0 mA                                         | V <sub>OUT1</sub> | 0.1  | _   | V <sub>CC</sub> -0.1 |      |

| Output Current ±5.0 mA                                         | V <sub>OUT2</sub> | 0.3  | _   | V <sub>CC</sub> -0.3 |      |

| Input Bias Current                                             | Ι <sub>Β</sub>    | _    | —   | 250                  | nA   |

| Input Offset Current                                           | Ι <sub>Ο</sub>    | -100 | —   | 100                  | nA   |

| Input Offset Voltage                                           | V <sub>IO</sub>   | -25  | —   | 25                   | mV   |

| Supply Voltage Rejection Ratio <sup>(20)</sup>                 | SVR               | 60   | —   | _                    | dB   |

| Common Mode Rejection Ratio <sup>(20)</sup>                    | CMR               | 70   | _   | -                    | dB   |

| Gain Bandwidth <sup>(20)</sup>                                 | GBP               | 1.0  | _   | _                    | MH   |

| Slew Rate                                                      | SR                | 0.5  | —   | _                    | V/μ  |

| Phase Margin (for Gain = 1, Load 100 pF//5.0 k $\Omega^{(20)}$ | РНМО              | 40   | _   | -                    | ٥    |

| Open Loop Gain                                                 | OLG               | —    | 85  | -                    | dB   |

| L1 and L2 Inputs                                               |                   |      |     |                      |      |

| Negative Switching Threshold                                   | V <sub>THN</sub>  |      |     |                      | V    |

| 5.5 V < V <sub>SUP</sub> < 6.0 V                               |                   | 2.0  | 2.5 | 3.0                  |      |

| 6.0 V < V <sub>SUP</sub> < 18 V                                |                   | 2.5  | 3.0 | 3.5                  |      |

| 18 V < V <sub>SUP</sub> < 27 V                                 |                   | 2.7  | 3.2 | 3.7                  |      |

| Positive Switching Threshold                                   | V <sub>THP</sub>  |      |     |                      | V    |

| 5.5 V < V <sub>SUP</sub> < 6.0 V                               |                   | 2.7  | 3.3 | 3.8                  |      |

| 6.0 V < V <sub>SUP</sub> < 18 V                                |                   | 3.0  | 4.0 | 4.5                  |      |

| 18 V < V <sub>SUP</sub> < 27 V                                 |                   | 3.5  | 4.2 | 4.7                  |      |

| Hysteresis                                                     | V <sub>HYST</sub> |      |     |                      | V    |

| 5.5 V < V <sub>SUP</sub> < 27 V                                |                   | 0.5  | —   | 1.3                  |      |

$I_{IN}$

-10

-0.2 V < V<sub>IN</sub> < 40 V

Input Current

Notes

20. This parameter is guaranteed by process monitoring but is not production tested.

μΑ

10

## DYNAMIC ELECTRICAL CHARACTERISTICS

## **Table 4. Dynamic Electrical Characteristics**

All characteristics are for the analog chip only. Please refer to the 68HC908EY16 datasheet for characteristics of the microcontroller chip. Characteristics noted under conditions 9.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  16 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  125°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                          | Symbol               | Min    | Тур | Max | Unit |

|-------------------------------------------------------------------------|----------------------|--------|-----|-----|------|

| LIN Physical Layer                                                      | ·                    |        |     |     |      |

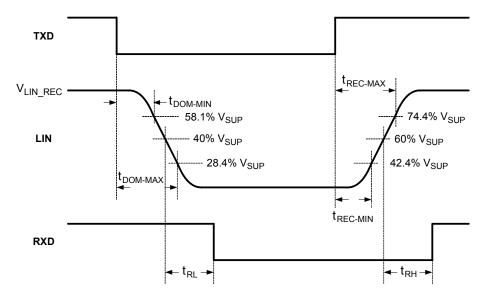

| Driver Characteristics for Normal Slew Rate <sup>(21), (22)</sup>       |                      |        |     |     |      |

| Dominant Propagation Delay TXD to LIN                                   | t <sub>DOM-MIN</sub> | —      | —   | 50  | μs   |

| Dominant Propagation Delay TXD to LIN                                   | t <sub>DOM-MAX</sub> | —      | _   | 50  | μs   |

| Recessive Propagation Delay TXD to LIN                                  | t <sub>REC-MIN</sub> | —      | _   | 50  | μs   |

| Recessive Propagation Delay TXD to LIN                                  | t <sub>REC-MAX</sub> | —      | _   | 50  | μs   |

| Propagation Delay Symmetry: t <sub>DOM-MIN</sub> - t <sub>REC-MAX</sub> | dt1                  | -10.44 |     | —   | μs   |

| Propagation Delay Symmetry: t <sub>DOM-MAX</sub> - t <sub>REC-MIN</sub> | dt2                  | _      | _   | 11  | μs   |

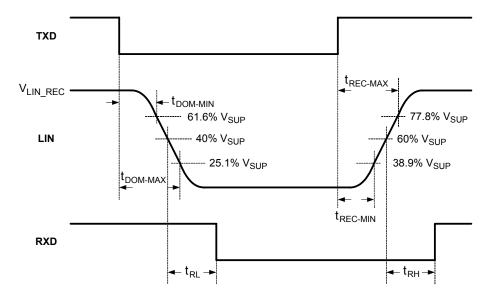

| Driver Characteristics for Slow Slew Rate <sup>(21), (23)</sup>         | ·                    |        |     |     | •    |

| Dominant Propagation Delay TXD to LIN                                   | t <sub>DOM-MIN</sub> | —      | _   | 100 | μs   |

| Dominant Propagation Delay TXD to LIN                                   | t <sub>DOM-MAX</sub> | —      | _   | 100 | μs   |

| Recessive Propagation Delay TXD to LIN                                  | t <sub>REC-MIN</sub> | —      | _   | 100 | μs   |

| Recessive Propagation Delay TXD to LIN                                  | t <sub>REC-MAX</sub> | _      | _   | 100 | μs   |

| Propagation Delay Symmetry: t <sub>DOM-MIN</sub> - t <sub>REC-MAX</sub> | dt1s                 | -22    | -   | _   | μs   |

| Propagation Delay Symmetry: t <sub>DOM-MAX</sub> - t <sub>REC-MIN</sub> | dt2s                 | _      | _   | 23  | μs   |

| Driver Characteristics for Fast Slew Rate                               |                      |        |     |     |      |

| LIN High Slew Rate (Programming Mode)                                   | SR <sub>FAST</sub>   | —      | 15  | _   | V/µs |

| Receiver Characteristics and Wake-Up Timings                            |                      |        |     |     |      |

| Receiver Dominant Propagation Delay (24)                                | t <sub>RL</sub>      | —      | 3.5 | 6.0 | μs   |

| Receiver Recessive Propagation Delay (24)                               | t <sub>RH</sub>      | —      | 3.5 | 6.0 | μs   |

| Receiver Propagation Delay Symmetry                                     | t <sub>R-SYM</sub>   | -2.0   | _   | 2.0 | μs   |

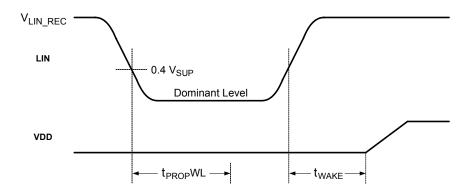

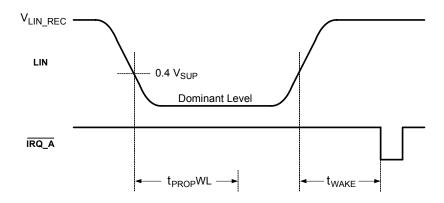

| Bus Wake-Up Deglitcher                                                  | t <sub>PROP</sub> WL | 35     |     | 80  | μs   |

| Bus Wake-Up Event Reported <sup>(25)</sup>                              | twake                | _      | 20  | _   | μs   |

Notes

V<sub>SUP</sub> from 7.0 V to 18 V, bus load R0 and C0 1.0 nF/1.0 kΩ, 6.8 nF/660 Ω, 10 nF/500 Ω. Measurement thresholds: 50% of TXD signal to LIN signal threshold defined at each parameter.

22. See Figure 6, page 15.

23. See <u>Figure 7</u>, page 16.

24. Measured between LIN signal threshold  $V_{\text{IL}}$  or  $V_{\text{IH}}$  and 50% of RXD signal.

25. t<sub>WAKE</sub> is typically 2 internal clock cycles after LIN rising edge detected. See Figure 8 and Figure 9, page 16. In Sleep mode the V<sub>DD</sub> rise time is strongly dependent upon the decoupling capacitor at VDD terminal.

All characteristics are for the analog chip only. Please refer to the 68HC908EY16 datasheet for characteristics of the microcontroller chip. Characteristics noted under conditions 9.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  16 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  125°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

|                                                                                                                              | <u> </u>              |      | -      |      |      |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|--------|------|------|

| Characteristic                                                                                                               | Symbol                | Min  | Тур    | Max  | Unit |

| SPI Interface Timing                                                                                                         |                       |      |        |      |      |

| SPI Operating Recommended Frequency                                                                                          | f <sub>SPIOP</sub>    | 0.25 | —      | 4.0  | MHz  |

| L1 AND L2 INPUTS                                                                                                             |                       |      |        |      |      |

| Wake-Up Filter Time <sup>(26)</sup>                                                                                          | t <sub>WUF</sub>      | 8.0  | 20     | 38   | μs   |

| Window Watchdog Configuration Terminal (WDCONF)                                                                              |                       |      |        |      |      |

| Watchdog Period                                                                                                              | P <sub>WD</sub>       |      |        |      | ms   |

| External Resistor R <sub>EXT</sub> = 10 kΩ (1%)                                                                              |                       | —    | 10.558 | —    |      |

| External Resistor R <sub>EXT</sub> = 100 k $\Omega$ (1%)                                                                     |                       | —    | 99.748 | —    |      |

| Without External Resistor R <sub>EXT</sub> (WDCONF Terminal Open)                                                            |                       | 97   | 150    | 205  |      |

| State Machine Timing                                                                                                         |                       |      |        |      |      |

| Reset Low-Level Duration after V <sub>DD</sub> High                                                                          | t <sub>RST</sub>      | 0.65 | 1.0    | 1.35 | ms   |

| Interrupt Low-Level Duration                                                                                                 | t <sub>INT</sub>      | 7.0  | 10     | 13   | μs   |

| Normal Request Mode Timeout                                                                                                  | NR <sub>TOUT</sub>    | 97   | 150    | 205  | ms   |

| Delay Between SPI Command and HS1/HS2/HS3 Turn On <sup>(27), (28)</sup>                                                      | t <sub>S-HSON</sub>   | —    | 3.0    | 10   | μs   |

| Delay Between SPI Command and HS1/HS2/HS3 Turn Off <sup>(27), (28)</sup>                                                     | t <sub>S-HSOFF</sub>  | —    | 3.0    | 10   | μs   |

| Delay Between Normal Request and Normal Mode After W/D Trigger Command $^{\rm (29)}$                                         | t <sub>S-NR2N</sub>   | 6.0  | 35     | 70   | μs   |

| Delay Between $\overline{\rm SS}$ Wake-Up ( $\overline{\rm SS}$ LOW to HIGH) and Normal Request Mode (VDD On and Reset High) | t <sub>W-SSB</sub>    | 15   | 40     | 80   | μs   |

| Delay Between $\overline{SS}$ Wake-Up ( $\overline{SS}$ LOW to HIGH) and First Accepted SPI Command                          | t <sub>W-SPI</sub>    | 90   | _      | N/A  | μs   |

| Delay Between Interrupt Pulse and First SPI Command Accepted                                                                 | t <sub>S-1STSPI</sub> | 30   | —      | N/A  | μs   |

| Minimum Time Between Two Rising Edges on $\overline{SS}$                                                                     | t <sub>2SSB</sub>     | 15   | —      | —    | μs   |

Notes

26. This parameter is guaranteed by process monitoring but is not production tested.

27. Delay between turn-on or turn-off command and high-side on or high-side off, excluding rise or fall time due to external load.

28. Delay between the end of the SPI command (rising edge of the SS) and start of device activation/deactivation.

29. This parameter is guaranteed by process monitoring but it is not production tested.

## **MICROCONTROLLER PARAMETRICS**

## Table 5. Microcontroller

For a detailed microcontroller description, refer to the MC68HC908EY16 datasheet.

| Module | Description                                                                                                                             |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Core   | High-Performance HC08 Core with a Maximum Internal Bus Frequency of 8.0 MHz                                                             |

| Timer  | Two 16-Bit Timers with 2 Channels (TIM A and TIM B)                                                                                     |

| Flash  | 16 K Bytes                                                                                                                              |

| RAM    | 512 Bytes                                                                                                                               |

| ADC    | 10-Bit Analog-to-Digital Converter                                                                                                      |

| SPI    | SPI Module                                                                                                                              |

| ESCI   | Standard Serial Communication Interface (SCI) Module<br>Bit-Time Measurement<br>Arbitration<br>Prescaler with Fine Baud-Rate Adjustment |

| ICG    | Internal Clock Generation Module                                                                                                        |

## TIMING DIAGRAMS

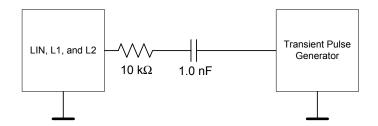

Note Waveform in accordance with ISO7637 Part 1, Test Pulses 1, 2, 3a, and 3b.

Figure 4. Test Circuit for Transient Test Pulses

Figure 5. Test Circuit for LIN Timing Measurements

Figure 6. LIN Timing Measurements for Normal Slew Rate

Figure 7. LIN Timing Measurements for Slow Slew Rate

Figure 8. Wake-Up Sleep Mode Timing

Figure 9. Wake-Up Stop Mode Timing

## FUNCTIONAL DESCRIPTION

## **INTRODUCTION**

The 908E624 was designed and developed as a highly integrated and cost-effective solution for automotive and industrial applications. For automotive body electronics, the 908E624 is well suited to perform relay control in applications like window lift, sunroof, etc., via a three-wire LIN bus.

The device combines an HC908EY16 MCU core with flash memory together with a SmartMOS IC chip. The SmartMOS IC chip combines power and control in one chip. Power switches are provided on the SmartMOS IC configured as

## FUNCTIONAL TERMINAL DESCRIPTION

## See Figure 1, 908E624 Simplified Application Diagram,

page 1, for a graphic representation of the various terminals referred to in the following paragraphs. Also, see the terminal diagram on page 3 for a depiction of the terminal locations on the package.

## **PORT A I/O TERMINALS**

These terminals are special-function, bidirectional I/O port terminals that are shared with other functional modules in the MCU. PTA0: PTA4 are shared with the keyboard interrupt terminals KBD0: KBD4.

The PTA5/SPSCK terminal is not accessible in this device and is internally connected to the SPI clock terminal of the analog die. The PTA6/SS terminal is likewise not accessible.

For details refer to the 68HC908EY16 datasheet.

## PORT B I/O TERMINALS

These terminals are special-function, bidirectional I/O port terminals that are shared with other functional modules in the MCU. All terminals are shared with the ADC module. The PTB6:PTB7 terminals are also shared with the Timer B module.

The PTB0/AD0 and PTB2/AD2 terminals are not accessible in this device.

For details refer to the 68HC908EY16 datasheet.

## PORT C I/O TERMINALS

These terminals are special-function, bidirectional I/O port terminals that are shared with other functional modules in the MCU. For example, PTC2:PTC4 are shared with the ICG module.

PTC0/MISO and PTC1/MOSI are not accessible in this device and are internally connected to the MISO and MOSI SPI terminals of the analog die.

For details refer to the 68HC908EY16 datasheet.

high-side outputs. Other ports are also provided, which include an operational amplifier port and two wake-up terminals. An internal voltage regulator provides power to the MCU chip.

Also included in this device is a LIN physical layer, which communicates using a single wire. This enables this device to be compatible with three-wire bus systems, where one wire is used for communication, one for battery, and one for ground.

## PORT D I/O TERMINALS

PTD1/TACH1 and PTD0/TACH0/BEMF are specialfunction, bidirectional I/O port terminals that can also be programmed to be timer terminals.

For details refer to the 68HC908EY16 datasheet.

## PORT E I/O TERMINAL

PTE1/RXD and PTE0/TXD are special-function, bidirectional I/O port terminals that can also be programmed to be enhanced serial communication.

PTE0/TXD is internally connected to the TXD terminal of the analog die. The connection for the receiver must be done externally.

For details refer to the 68HC908EY16 datasheet.

## EXTERNAL INTERRUPT TERMINAL (IRQ)

The IRQ terminal is an asynchronous external interrupt terminal. This terminal contains an internal pullup resistor that is always activated, even when the IRQ terminal is pulled LOW.

For details refer to the 68HC908EY16 datasheet.

## **EXTERNAL RESET TERMINAL (RST)**

A logic [0] on the RST terminal forces the MCU to a known startup state. It is driven LOW when any internal reset source is asserted.

This terminal contains an internal pullup resistor that is always activated, even when the reset terminal is pulled LOW.

Important To ensure proper operation, do not add any external pullup resistor.

For details refer to the 68HC908EY16 datasheet.

## MCU POWER SUPPLY TERMINALS (EVDD AND EVSS)

EVDD and EVSS are the power supply and ground terminals, respectively. The MCU operates from a singlepower supply.

Fast signal transitions on MCU terminals place high, shortduration current demands on the power supply. To prevent noise problems, take special care to provide power supply bypassing at the MCU.

For details refer to the 68HC908EY16 datasheet.

## ADC SUPPLY TERMINALS (VDDA AND VSSA)

VDDA and VSSA are the power supply terminals for the analog-to-digital converter (ADC). It is recommended that a high-quality ceramic decoupling capacitor be placed between these terminals.

**Important** VDDA is the supply for the ADC and should be tied to the same potential as EVDD via separate traces. VSSA is the ground terminal for the ADC and should be tied to the same potential as EVSS via separate traces.

For details refer to the 68HC908EY16 datasheet.

# ADC REFERENCE TERMINALS (VREFL AND VREFH)

VREFL and VREFH are the reference voltage terminals for the ADC. It is recommended that a high-quality ceramic decoupling capacitor be placed between these terminals.

**Important** VREFH is the high reference supply for the ADC and should be tied to the same potential as VDDA via separate traces. VREFL is the low reference supply for the ADC and should be tied to the same potential as VSSA via separate traces.

For details refer to the 68HC908EY16 datasheet.

## **TEST TERMINAL (FLSVPP)**

This terminal is for test purposes only. Do not connect in the application.

## **PWMIN TERMINAL**

This terminal is the direct PWM input for high-side outputs 1 and 2 (HS1 and HS2). If no PWM control is required, PWMIN must be connected to VDD to enable the HS1 and HS2 outputs.

## LIN TRANSCEIVER OUTPUT TERMINAL (RXD)

This terminal is the output of LIN transceiver. The terminal must be connected to the microcontroller's Enhanced Serial Communications Interface (ESCI) module (RXD terminal).

## RESET TERMINAL (RST\_A)

RST\_A is the reset output terminal of the analog die and must be connected to the RST terminal of the MCU.

**Important** To ensure proper operation, do not add any external pullup resistor.

## INTERRUPT TERMINAL (IRQ\_A)

IRQ\_A is the interrupt output terminal of the analog die indicating errors or wake-up events. This terminal must be connected to the IRQ terminal of the MCU.

# WINDOW WATCHDOG CONFIGURATION TERMINAL (WDCONF)

This terminal is the configuration terminal for the internal watchdog. A resistor is connected to this terminal. The resistor value defines the watchdog period. If the terminal is open, the watchdog period is fixed to its default value.

The watchdog can be disabled (e.g., for flash programming or software debugging) by connecting this terminal to GND.

## POWER SUPPLY TERMINALS (VSUP1 AND VSUP2)

This VSUP1 power supply terminal supplies the voltage regulator, the internal logic, and LIN transceiver.

This VSUP2 power supply terminal is the positive supply for the high-side switches.

## POWER GROUND TERMINAL (GND)

This terminal is the device ground connection.

## HIGH-SIDE OUTPUT TERMINALS (HS1 AND HS2)

These terminals are high-side switch outputs to drive loads such as relays or lamps. Each switch is protected with overtemperature and current limit (overcurrent). The output has an internal clamp circuitry for inductive load. The HS1 and HS2 outputs are controlled by SPI and have a direct enabled input (PWMIN) for PWM capability.

## **HIGH-SIDE OUTPUT TERMINAL (HS3)**

This high-side switch can be used to drive small lamps, Hall-effect sensors, or switch pullup resistors. The switch is protected with overtemperature and current limit (overcurrent). The output is controlled only by SPI.

## LIN BUS TERMINAL (LIN)

The LIN terminal represents the single-wire bus transmitter and receiver. It is suited for automotive bus systems and is based on the LIN bus specification.

## WAKE-UP TERMINALS (L1 AND L2)

These terminals are high-voltage capable inputs used to sense external switches and to wake up the device from Sleep or Stop mode. During Normal mode the state of these terminals can be read through SPI.

## SENSE AMPLIFIER TERMINALS (E+, E-, OUT, VCC)

These are the terminals of the single-supply sense amplifier.

- The E+ and E- input terminals are the non-inverting and inverting inputs of the amplifier, respectively.

- The OUT terminal is the output terminal of the current sense amplifier.

- The VCC terminal is the +5.0 V single-supply connection.

## +5.0 V VOLTAGE REGULATOR OUTPUT TERMINAL (VDD)

The VDD terminal is needed to place an external capacitor to stabilize the regulated output voltage. The VDD terminal is

intended to supply the embedded microcontroller. The terminal is protected against shorts to GND with an integrated current limit (temperature shutdown could occur).

**Important** The VDD, EVDD, VDDA, and VREFH terminals must be connected together.

## VOLTAGE REGULATOR AND SENSE AMPLIFIER GROUND TERMINAL (AGND)

The AGND terminal is the ground terminal of the voltage regulator and the Sense Amplifier.

**Important** GND, AGND, VSS, EVSS, VSSA, and VREFL terminals must be connected together.

## FUNCTIONAL DEVICE OPERATION

## **OPERATIONAL MODES**

## 908E624 ANALOG DIE MODES OF OPERATION

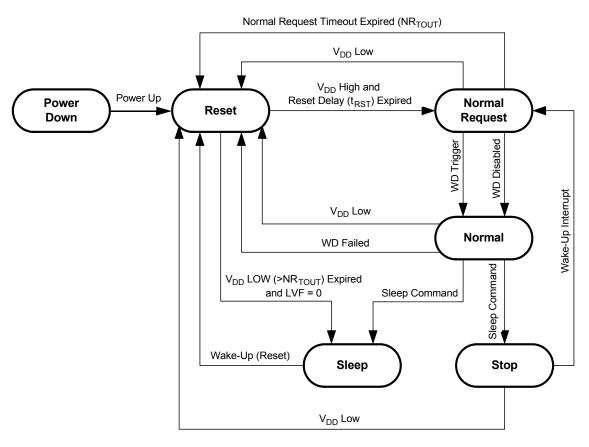

The 908E624 offers three operating modes: Normal (Run), Stop, and Sleep. In Normal mode the device is active and is operating under normal application conditions. The Stop and Sleep modes are low-power modes with wake-up capabilities.

In Stop mode the voltage regulator still supplies the MCU with  $V_{DD}$  (limited current capability) and in Sleep mode the voltage regulator is turned off ( $V_{DD} = 0$  V).

Wake-up from Stop mode is initiated by a wake-up interrupt. Wakeup from Sleep mode is done by a reset and the voltage regulator is turned back on.

The selection of the different modes is controlled by the MODE1:2 bits in the SPI Control register.

Figure 10 describes how transitions are done between the different operating modes and <u>Table 6</u>, page 21, gives an overview of the operating mode.

Legend

WD: Watchdog

WD Disabled: Watchdog disabled (WDCONF terminal connected to GND)

WD Trigger: Watchdog is triggered by SPI command

WD Failed: No watchdog trigger or trigger occurs in closed window

Stop Command: Stop command sent via SPI

Sleep Command: Sleep command sent via SPI

Wake-Up: L1 or L2 state change or LIN bus wake-up or SS rising edge

#### Figure 10. Operating Modes and Transitions

| Device<br>Mode    | Voltage Regulator                                  | Wake-Up<br>Capabilities                                | RST_A<br>Output | Watchdog<br>Function             | HS1, HS2,<br>and HS3 | LIN Interface                           | Sense<br>Amplifier |

|-------------------|----------------------------------------------------|--------------------------------------------------------|-----------------|----------------------------------|----------------------|-----------------------------------------|--------------------|

| Reset             | V <sub>DD</sub> ON                                 | N/A                                                    | LOW             | Disabled                         | Disabled             | Recessive only                          | Not active         |

| Normal<br>Request | V <sub>DD</sub> ON                                 | N/A                                                    | HIGH            | 150 ms time out if<br>WD enabled | Enabled              | Transmit and receive                    | Not active         |

| Normal<br>(Run)   | V <sub>DD</sub> ON                                 | N/A                                                    | HIGH            | Window WD if<br>enabled          | Enabled              | Transmit and receive                    | Active             |

| Stop              | V <sub>DD</sub> ON with limited current capability | LIN wake-up,<br>L1, L2 state change,<br>SS rising edge | HIGH            | Disabled                         | Disabled             | Recessive state with wake-up capability | Not active         |

| Sleep             | V <sub>DD</sub> OFF                                | LIN wake-up<br>L1, L2 state change                     | LOW             | Disabled                         | Disabled             | Recessive state with wake-up capability | Not active         |

## Table 6. Operating Modes Overview

## INTERRUPTS

In Normal (Run) mode the 908E624 has four different interrupt sources. An interrupt pulse on the IRQ\_A terminal is generated to report a fault to the MCU. All interrupts are not maskable and cannot be disabled.

After an Interrupt the INTSRC bit in the SPI Status register is set, indicating the source of the event. This interrupt source information is only transferred once, and the INTSRC bit is cleared automatically.

## Low-Voltage Interrupt

Low-voltage interrupt (LVI) is related to external supply voltage VSUP1. If this voltage falls below the LVI threshold, it will set the LVF bit in the SPI Status register and an interrupt will be initiated. The LVF bit remains set as long as the Lowvoltage condition is present.

During Sleep and Stop mode the low-voltage interrupt circuitry is disabled.

## **High-Voltage Interrupt**

High-voltage interrupt (HVI) is related to external supply voltage VSUP1. If this voltage rises above the HVI threshold, it will set the HVF bit in the SPI Status register and an interrupt will be initiated. The HVF bit remains set as long as the high-voltage condition is present.

During Sleep and Stop mode the low-voltage interrupt circuitry is disabled.

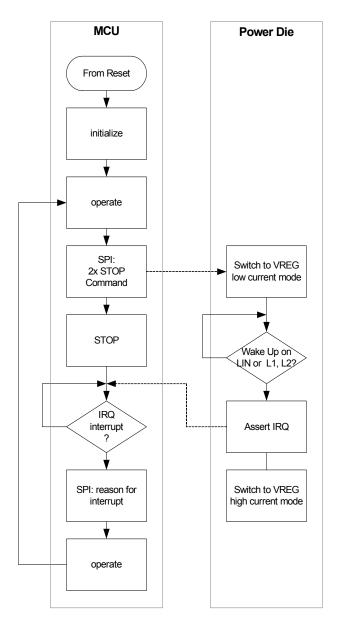

## Wake-Up Interrupts

In Stop mode the IRQ\_A terminal reports wake-up events on the L1, L2, or the LIN bus to the MCU. All wake-up interrupts are not maskable and cannot be disabled. After a wake-up interrupt, the INTSRC bit in the Serial Peripheral Interface (SPI) Status register is set, indicating the source of the event. This wake-up source information is only transferred once, and the INTSRC bit is cleared automatically.

Figure 11, page 22, describes the Stop/Wake-Up procedure.

## VOLTAGE REGULATOR TEMPERATURE PREWARNING (VDDT)

Voltage regulator temperature prewarning (VDDT) is generated if the voltage regulator temperature is above the  $T_{PRE}$  threshold, it will set the VDDT bit in the SPI Status register and an interrupt will be initiated. The VDDT bit remains set as long as the error condition is present.

During Sleep and Stop mode the voltage regulator temperature prewarning circuitry is disabled.

## HIGH-SIDE SWITCH THERMAL SHUTDOWN (HSST)

The high-side switch thermal shutdown HSST is generated if one of the high-side switches HS1: HS3 is above the HSST threshold, it will shutdown the corresponding Highside switch, set the HSST flag in the SPI Status register and an interrupt will be initiated. The HSST bit remains set as long as the error condition is present.

During Sleep and Stop mode the high-side switch thermal shutdown circuitry is disabled.

## ANALOG DIE INPUTS/OUTPUTS

#### High-Side Output Terminals HS1 and HS2

These are two high-side switches used to drive loads such as relays or lamps. They are protected with overtemperature and current limit (overcurrent) and include an active internal clamp circuitry for inductive load drive. Control is done using the SPI Control register. PWM capability is offered through the PWMIN input terminal.

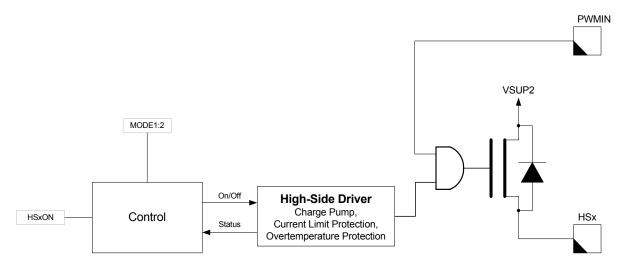

The high-side switch is turned on if both the HSxON bit in the SPI Control register is set and the PWMIN input is HIGH (refer to Figure 12, page 23). In order to have HS1 on, the PWMIN must be HIGH and bit HS1ON must be set. The same applies to the HS2 output.

If no PWM control is required, PWMIN must be connected to the VDD terminal.

#### **Current Limit (Overcurrent) Protection**

These high-side switches feature current limit to protect them against overcurrent and short circuit conditions.

#### **Overtemperature Protection**

If an overtemperature condition occurs on any of the three high-side switches, the faulty switch is turned off and latched off until the HS1 (or HS2 or HS3) bit is set to "1" in the SPI Control register. The failure is reported by the HSST bit in the SPI Control register.

## Sleep and Stop Mode

In Sleep and Stop modes the high-sides are disabled.

## **High-Side Output HS3**

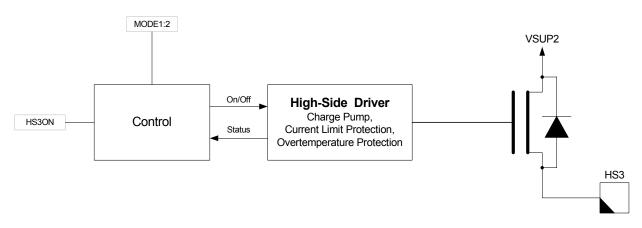

This high-side switch can be used to drive small lamps, Hall-effect sensors, or switch pullup resistors. Control is done using the SPI Control register. No direct PWM control is possible on this terminal (refer to <u>Figure 13</u>, page 23).

## Current Limit (Overcurrent) Protection

This high-side feature switch feature current limit to protect it against overcurrent and short circuit conditions.

## **Overtemperature Protection**

If an overtemperature condition occurs on any of the three high-side switches, the faulty switch is turned off and latched off until the HS3 (or HS1 or HS2) bit is set to "1" in the SPI Control register. The failure is reported by the HSST bit in the SPI Control register.

## Sleep and Stop Mode

In Sleep and Stop mode the high-side is disabled.

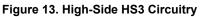

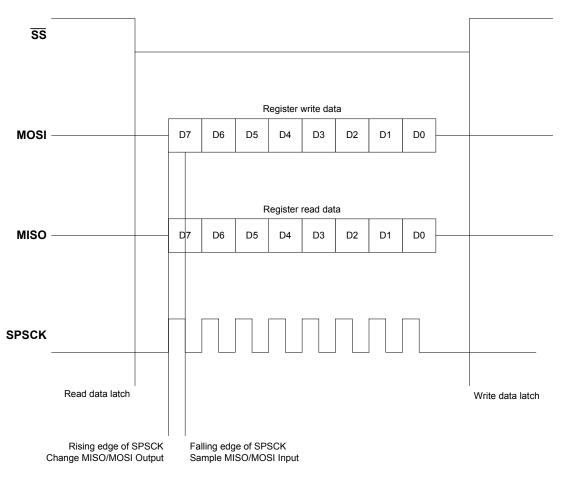

## WINDOW WATCHDOG

The window watchdog is configurable using an external resistor at the WDCONF terminal. The watchdog is cleared through by the MODE1:2 bits in the SPI Control register (refer to <u>Table 8</u>, page 26).

A watchdog clear is only allowed in the open window. If the watchdog is cleared in the closed window or has not been cleared at the end of the open window, the watchdog will generate a reset on the RST\_A terminal and reset the whole device.

**Note** The watchdog clear in Normal request mode (150 ms) (first watchdog clear) has no window.

## Watchdog Configuration

If the WDCONF terminal is left open, the default watchdog period is selected (typ. 150 ms). If no watchdog function is required, the WDCONF terminal must be connected to GND.

The watchdog period is calculated using the following formula:

## **VOLTAGE REGULATOR**

The 908E624 chip contains a low-power, low dropout voltage regulator to provide internal power and external power for the MCU. The on-chip regulator consist of two elements, the main voltage regulator and the low-voltage reset circuit.

The V<sub>DD</sub> regulator accepts an unregulated input supply and provides a regulated V<sub>DD</sub> supply to all digital sections of the device. The output of the regulator is also connected to the VDD terminal to provide the 5.0 V to the microcontroller.

## **Current Limit (Overcurrent) Protection**

The voltage regulator has current limit to protect the device against overcurrent and short circuit conditions.

## **Overtemperature Protection**

The voltage regulator also features an overtemperature protection having an overtemperature warning (Interrupt - VDDT) and an overtemperature shutdown.

## Stop Mode

During Stop mode the Stop mode regulator supplies a regulated output voltage. The Stop mode regulator has a limited output current capability.

## Sleep Mode

In Sleep mode the voltage regulator external  $\mathsf{V}_{\mathsf{D}\mathsf{D}}$  is turned off.

## FACTORY TRIMMING AND CALIBRATION

To enhance the ease-of-use of the 908E624, various parameters (e.g., ICG trim value) are stored in the flash memory of the device. The following flash memory locations are reserved for this purpose and might have a value different from the "empty" (0xFF) state:

- 0xFD80:0xFDDF Trim and Calibration Values

- 0xFFFE:0xFFFF Reset Vector

In the event the application uses these parameters, one has to take care not to erase or override these values. If these parameters are not used, these flash locations can be erased and otherwise used.

## **OPERATING MODES OF THE MCU**

For a detailed description of the operating modes of the MCU, refer to the MC68HC908EY16 datasheet.

## LOGIC COMMANDS AND REGISTERS

## 908E624 SPI INTERFACE AND CONFIGURATION

The serial peripheral interface creates the communication link between the microcontroller and the analog die of the 908E624.

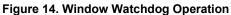

The interface consists of four terminals (see Figure 15):

- SS—Slave Select

- MOSI—Master-Out Slave-In

- MISO—Master-In Slave-Out

- SPSCK—Serial Clock

A complete data transfer via the SPI consists of 1 byte. The master sends 8 bits of control information and the slave replies with 8 bits of status data.

## Figure 15. SPI Protocol

During the inactive phase of the  $\overline{\text{SS}}$  (High), the new data transfer is prepared.

The falling edge of the  $\overline{SS}$  indicates the start of a new data transfer and puts the MISO in the low-impedance state and latches the analog status data (Register read data).

With the rising edge of the SPI clock, SPSCK the data is moved to MISO/MOSI terminals. With the falling edge of the SPI clock SPSCK the data is sampled by the Receiver.

The data transfer is only valid if exactly 8 sample clock edges are present in the active (low) phase of  $\overline{\text{SS}}$ .

The rising edge of the slave select  $\overline{SS}$  indicates the end of the transfer and latches the write data (MOSI) into the register The  $\overline{SS}$  high forces MISO to the high impedance state.

## SPI REGISTER OVERVIEW

<u>Table 7</u> summarizes the SPI Register bit meaning, reset value, and bit reset condition.

## Table 7. SPI Register Overview

| Read/Write            |                        | Bit                    |        |                                      |               |               |       |       |  |  |

|-----------------------|------------------------|------------------------|--------|--------------------------------------|---------------|---------------|-------|-------|--|--|

| Information           | D7                     | D6                     | D5     | D4                                   | D3            | D2            | D1    | D0    |  |  |

| Write                 | LINSL2                 | LINSL1                 | LIN-PU | HS3ON                                | HS2ON         | HS1ON         | MODE2 | MODE1 |  |  |

| Read                  | INTSRC <sup>(30)</sup> | LINWU<br>or<br>LINFAIL | HVF    | LVF<br>or<br>BATFAIL <sup>(31)</sup> | VDDT          | HSST          | L2    | L1    |  |  |

| Write Reset Value     | 0                      | 0                      | 0      | 0                                    | 0             | 0             | —     | _     |  |  |

| Write Reset Condition | POR,<br>RESET          | POR,<br>RESET          | POR    | POR, RESET                           | POR,<br>RESET | POR,<br>RESET | _     | _     |  |  |

Notes

30. D7 signals interrupts and wake-up interrupts, D6:D0 indicated the source.

31. The first SPI read after reset returns the BATFAIL flag state on bit D4.

#### SPI Control Register (Write)

Table 8 shows the SPI Control register bits by name.

## Table 8. Control Bits Function (Write Operation)

| D7     | D6     | D5     | D4    | D3    | D2    | D1    | D0    |

|--------|--------|--------|-------|-------|-------|-------|-------|

| LINSL2 | LINSL1 | LIN-PU | HS3ON | HS2ON | HS10N | MODE2 | MODE1 |

## LINSL2:1—LIN Baud Rate and Low-Power Mode Selection Bits

These bits select the LIN slew rate and requested lowpower mode in accordance with <u>Table 9</u>. Reset clears the LINSL2:1 bits.

## Table 9. LIN Baud Rate and Low-Power Mode Selection Bits

| LINSL2 | LINSL1 | Description                                       |

|--------|--------|---------------------------------------------------|

| 0      | 0      | Baud Rate up to 20 kbps (normal)                  |

| 0      | 1      | Baud Rate up to 10 kbps (slow)                    |

| 1      | 0      | Fast Program Download<br>Baud Rate up to 100 kbps |

| 1      | 1      | Low-Power Mode (Sleep or Stop) Request            |

## LIN-PU—LIN Pullup Enable Bit

This bit controls the LIN pullup resistor during Sleep and Stop modes.