# 82091AA ADVANCED INTEGRATED PERIPHERAL (AIP)

- Single-Chip PC Compatible I/O Solution for Notebook and Desktop Platforms:

- 82078 Floppy Disk Controller Core

- Two 16550 Compatible UARTs

- One Multi-Function Parallel Port

- IDE Interface

- Integrated Back Power Protection

- Integrated Game Port Chip Select

- 5V or 3.3V Supply Operation with 5V Tolerant Drive Interface

- Full Power Management Support

- Supports Type F DMA Transfers for Faster I/O Performance

- No Wait-State Host I/O Interface

- Programmable Interrupt Interfaces

- Single Crystal/Oscillator Clock (24 MHz)

- Software Detectable Device ID

- Comprehensive Powerup Configuration

- The 82091AA is 100 Percent Compatible with EISA, ISA and AT

- Host Interface Features

- 8-Bit Zero Wait-State ISA Bus Interface

- DMA with Type F Transfers

- Five Programmable ISA Interrupt Lines

- Internal Address Decoder

- Parallel Port Features

- All IEEE Standard 1284 Protocols Supported (Compatibility, Nibble, Byte, EPP, and ECP)

- Peak Bi-Directional Transfer Rate of 2 MB/sec

- Provides Interface for Low-Cost Engineless Laser Printer

- 16-Byte FIFO for ECP

- Interface Backpower Protection

- **■** Floppy Disk Controller Features

- 100 Percent Software Compatible with Industry Standard 82077SL and 82078

- Integrated Analog Data Separator 250K, 300K, 500K, and 1 MBits/sec

- Programmable Powerdown Command

- Auto Powerdown and Wakeup Modes

- Integrated Tape Drive Support

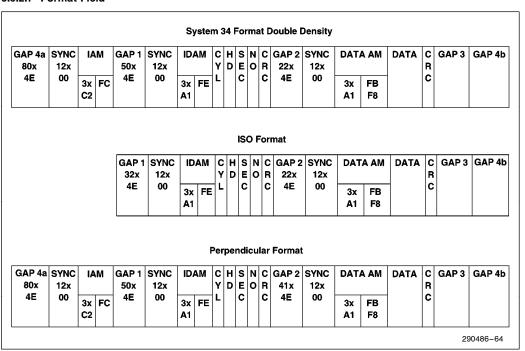

- Perpendicular Recording Support for 4 MB Drives

- Programmable Write Pre-Compensation Delays

- 256 Track Direct Address, Unlimited Track Support

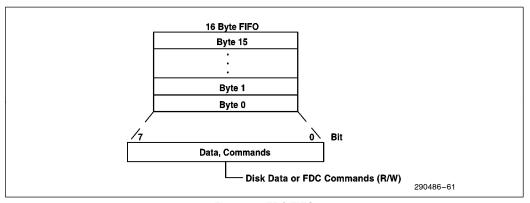

- 16-Byte FIFO

- Supports 2 or 4 Drives

- 16550 Compatible UART Features

- Two Independent Serial Ports

- Software Compatible with 8250 and 16450 UARTs

- 16-Byte FIFO per Serial Port

- Two UART Clock Sources, Supports

MIDI Baud Rate

- IDE Interface Features

- Generates Chip Selects for IDE

Drives

- Integrated Buffer Control Logic

- Dual IDE Interface Support

- Power Management Features

- Transparent to Operating Systems and Applications Programs

- Independent Power Control for Each Integrated Device

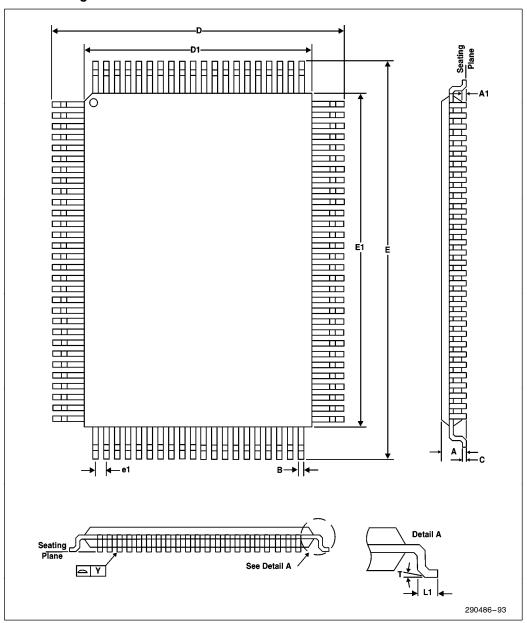

- 100-Pin QFP Package

(See Packaging Spec. 240800)

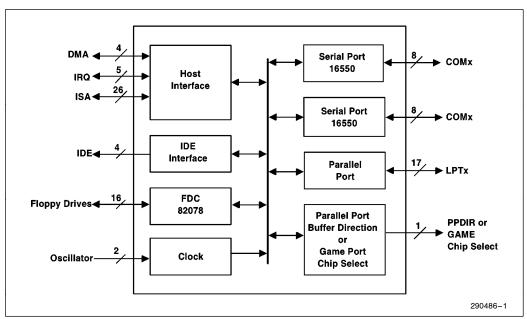

The 82091AA Advanced Integrated Peripheral (AIP) is an integrated I/O solution containing a floppy disk controller, 2 serial ports, a multi-function parallel port, an IDE interface, and a game port on a single chip. The integration of these I/O devices results in a minimization of form factor, cost and power consumption. The

floppy disk controller is the 82078 core. The serial ports are 16550 compatible. The parallel port supports all of the IEEE Standard 1284 protocols (ECP, EPP, Byte, Compatibility, and Nibble). The IDE interface supports 8- or 16-bit programmed I/O and 16-bit DMA. The Host Interface is an 8-bit ISA interface optimized for type "F" DMA and no wait-state I/O accesses. Improved throughput and performance, the 82091AA contains six 16-byte FIFOs—two for each serial port, one for the parallel port, and one for the floppy disk controller. The 82091AA also includes power management and 3.3V capability for power sensitive applications such as notebooks. The 82091AA supports both motherboard and add-in card configurations.

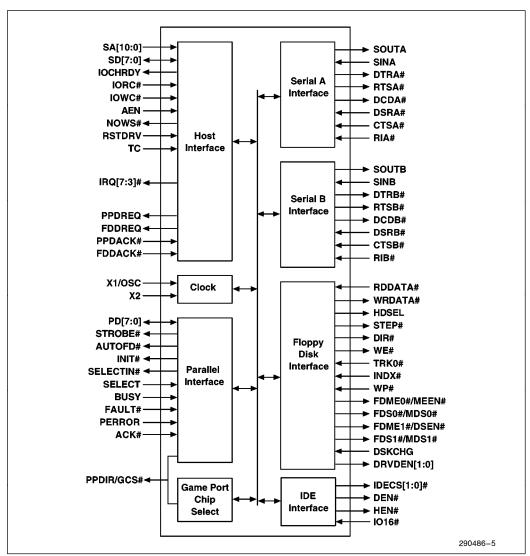

Figure 1. 82091AA Advanced Integrated Peripheral Block Diagram

# 82091AA ADVANCED INTEGRATED PERIPHERAL (AIP)

| CONTENTS                                                            | PAGE |

|---------------------------------------------------------------------|------|

| 1.0 OVERVIEW                                                        | 8    |

| 1.1 3.3/5V Operating Modes                                          | 11   |

| 2.0 SIGNAL DESCRIPTION                                              | 11   |

| 2.1 Host Interface Signals                                          | 13   |

| 2.2 Floppy Disk Controller Interface                                | 15   |

| 2.3 Serial Port Interface                                           | 17   |

| 2.4 IDE Interface                                                   | 18   |

| 2.5 Parallel Port External Buffer Control/Game Port                 | 19   |

| 2.6 Parallel Port Interface                                         |      |

| 2.6.1 COMPATIBILITY PROTOCOL SIGNAL DESCRIPTION                     | 21   |

| 2.6.2 NIBBLE PROTOCOL SIGNAL DESCRIPTION                            |      |

| 2.6.3 BYTE MODE SIGNAL DESCRIPTION                                  |      |

| 2.6.4 ENHANCED PARALLEL PORT (EPP) PROTOCOL SIGNAL DESCRIPTION      |      |

| 2.6.5 EXTENDED CAPABILITIES PORT (ECP) PROTOCOL SIGNAL DESCRIPTION  |      |

| 2.7 Hard Reset Signal Conditions                                    |      |

| 2.8 Power And Ground                                                | 27   |

| 3.0 I/O ADDRESS ASSIGNMENTS                                         | 27   |

| 4.0 AIP CONFIGURATION                                               | 29   |

| 4.1 Configuration Registers                                         | 29   |

| 4.1.1 CFGINDX, CFGTRGT—CONFIGURATION INDEX REGISTER AND TARGET PORT | 30   |

| 4.1.2 AIPID—AIP IDENTIFICATION REGISTER                             |      |

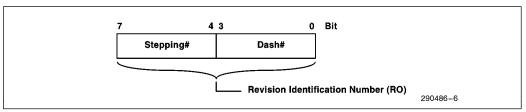

| 4.1.3 AIPREV—AIP REVISION IDENTIFICATION                            |      |

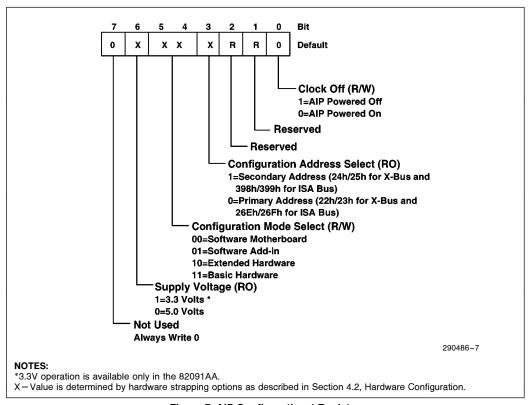

| 4.1.4 AIPCFG1—AIP CONFIGURATION 1 REGISTER                          | 33   |

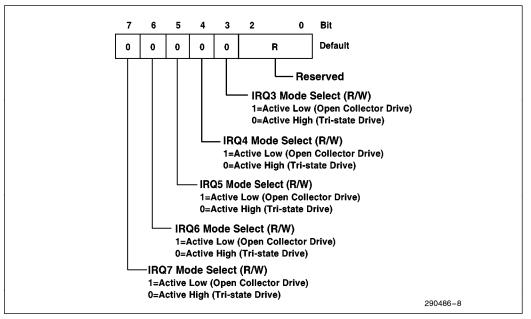

| 4.1.5 AIPCFG2—AIP CONFIGURATION 2 REGISTER                          | 34   |

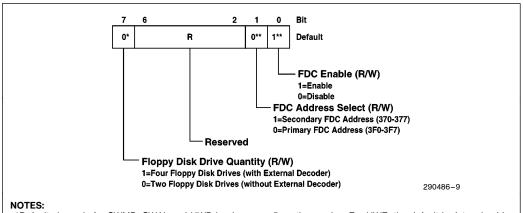

| 4.1.6 FCFG1—FDC CONFIGURATION REGISTER                              | 36   |

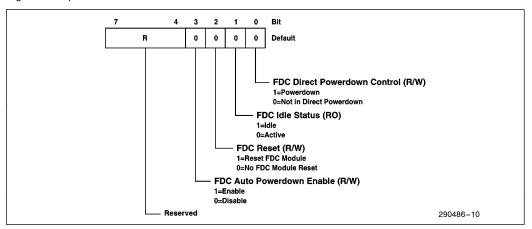

| 4.1.7 FCFG2—FDC POWER MANAGEMENT AND STATUS REGISTER                | 37   |

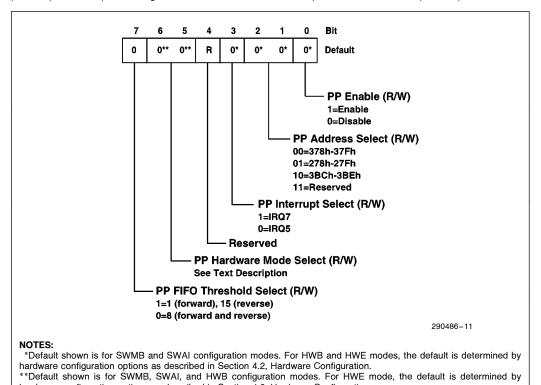

| 4.1.8 PCFG1—PARALLEL PORT CONFIGURATION REGISTER                    | 38   |

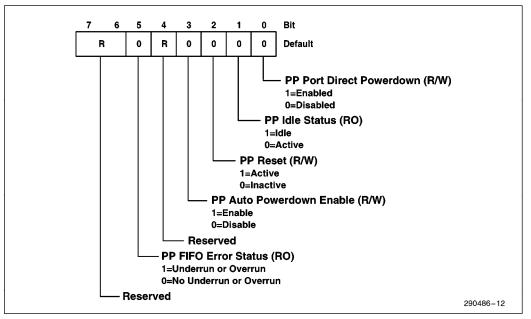

| 4.1.9 PCFG2—PARALLEL PORT POWER MANAGEMENT AND STATUS REGISTER      | 40   |

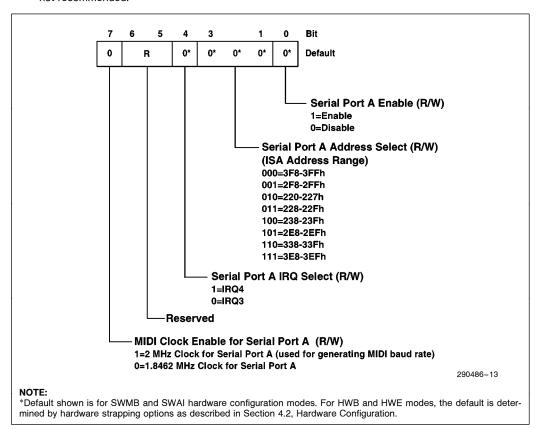

| 4.1.10 SACFG1—SERIAL PORT A CONFIGURATION REGISTER                  |      |

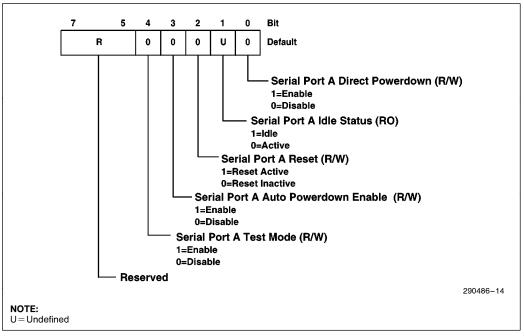

| 4.1.11 SACFG2—SERIAL PORT A POWER MANAGEMENT AND STATUS             |      |

| REGISTER                                                            |      |

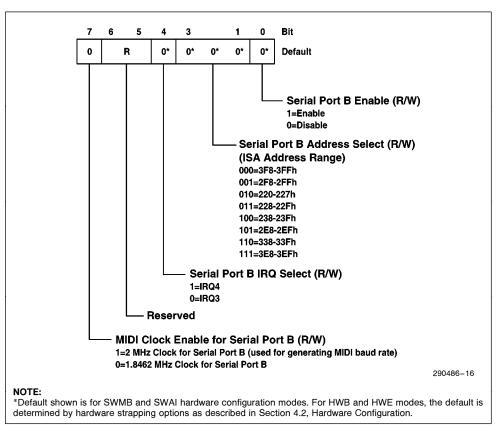

| 4.1.12 SBCFG1—SFRIAL PORT B CONFIGURATION REGISTER                  | 46   |

| <b>CONTENTS</b> PA                                                            | GE   |

|-------------------------------------------------------------------------------|------|

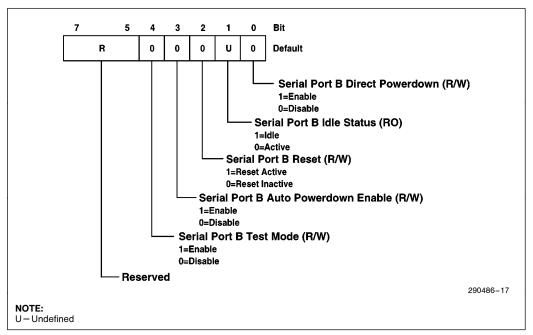

| 4.1.13 SBCFG2—SERIAL PORT B POWER MANAGEMENT AND STATUS                       |      |

| REGISTER                                                                      |      |

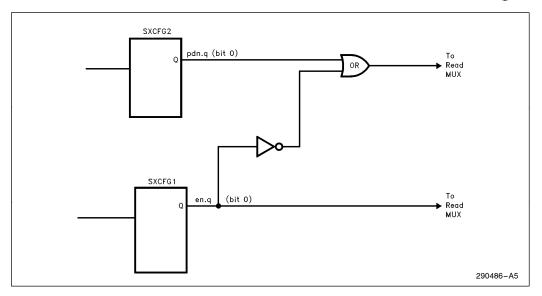

| 4.1.13.1 Serial Port A/B Configuration Registers SxEN and SxDPDN Bits         |      |

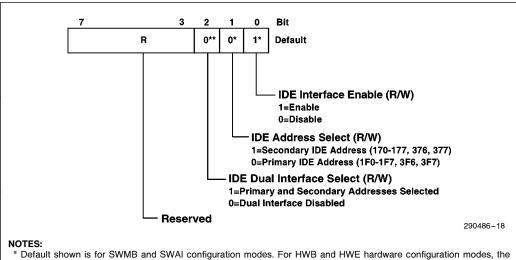

| 4.1.14 IDECFG—IDE CONFIGURATION REGISTER                                      |      |

| 4.2 Hardware Configuration                                                    |      |

| 4.2.1 SELECTING THE HARDWARE CONFIGURATION MODE                               |      |

| 4.2.2 SELECTING HARDWARE CONFIGURATION MODE OPTIONS                           |      |

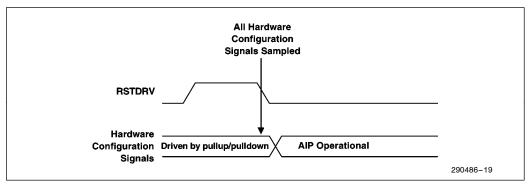

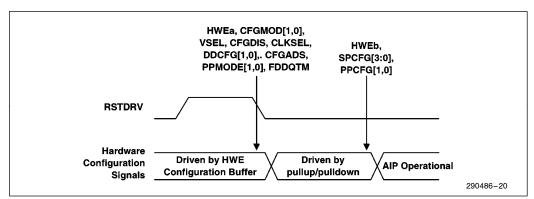

| 4.2.3 HARDWARE CONFIGURATION TIMING RELATIONSHIPS                             |      |

| 4.2.4 HARDWARE BASIC CONFIGURATION                                            |      |

| 4.2.5 HARDWARE EXTENDED CONFIGURATION MODE                                    |      |

| 4.2.6 SOFTWARE ADD-IN CONFIGURATION                                           |      |

| 4.2.7 SOFTWARE MOTHERBOARD CONFIGURATION                                      | . 60 |

| 5.0 HOST INTERFACE                                                            | . 61 |

| 6.0 PARALLEL PORT                                                             | 62   |

| 6.1 Parallel Port Registers                                                   |      |

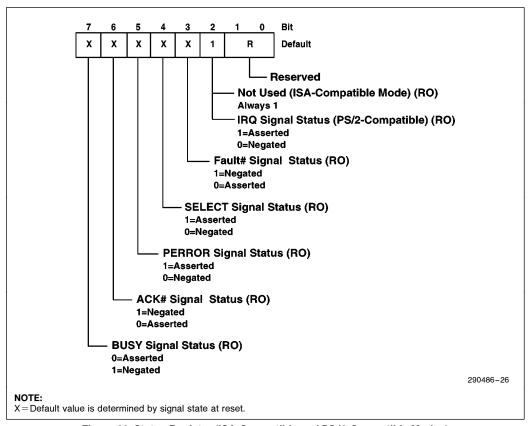

| 6.1.1 ISA-COMPATIBLE AND PS/2-COMPATIBLE MODES                                |      |

| 6.1.1.1 PDATA—Parallel Port Data Register (ISA-Compatible and PS/2-Compatible | . 03 |

| Modes)                                                                        | . 64 |

| 6.1.1.2 PSTAT—Status Register (ISA-Compatible and PS/2-Compatible Modes)      |      |

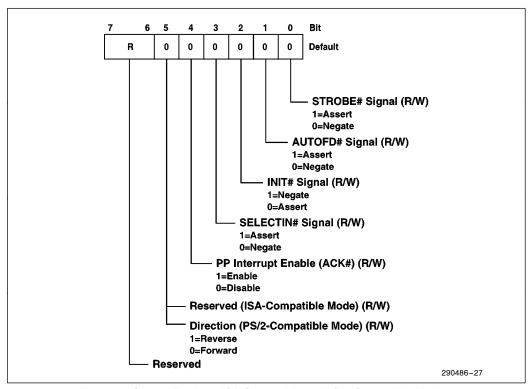

| 6.1.1.3 PCON—Control Register (ISA-Compatible and PS/2-Compatible Mode)       |      |

| 6.1.2 EPP MODE                                                                | . 69 |

| 6.1.2.1 PDATA—Parallel Port Data Register (EPP Mode)                          | . 69 |

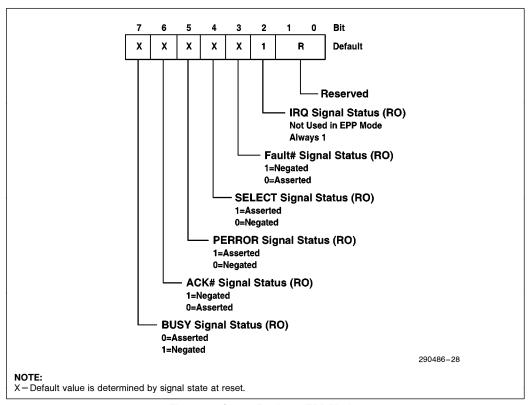

| 6.1.2.2 PSTAT—Status Register (EPP Mode)                                      | . 70 |

| 6.1.2.3 PCON—Control Register (EPP Mode)                                      | . 72 |

| 6.1.2.4 ADDSTR—EPP Auto Address Strobe Register (EPP Mode)                    | . 73 |

| 6.1.2.5 DATASTR—Auto Data Strobe Register (EPP Mode)                          | . 74 |

| 6.1.3 ECP MODE                                                                | . 74 |

| 6.1.3.1 ECPAFIFO—ECP Address/RLE FIFO Register (ECP Mode)                     | . 75 |

| 6.1.3.2 PSTAT—Status Register (ECP Mode)                                      | . 76 |

| 6.1.3.3 PCON—Control Register (ECP Mode)                                      | . 78 |

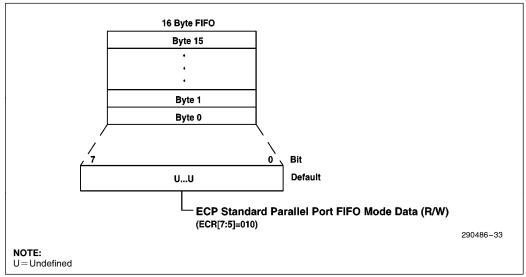

| 6.1.3.4 SDFIFO—Standard Parallel Port Data FIFO                               | . 80 |

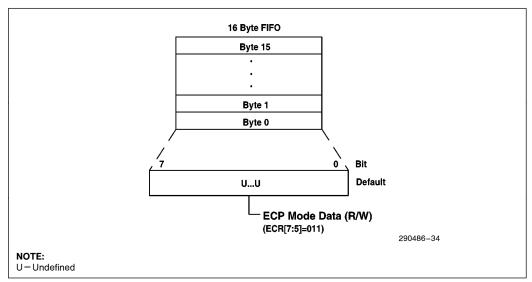

| 6.1.3.5 DFIFO—Data FIFO (ECP Mode)                                            | . 81 |

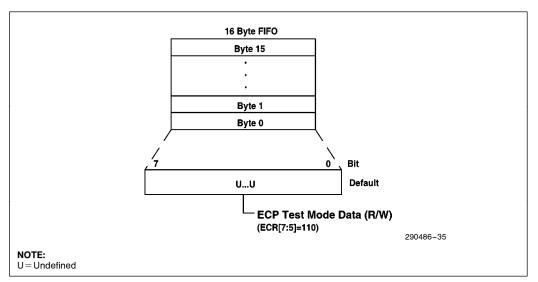

| 6.1.3.6 TFIFO—ECP Test FIFO Register (ECP Mode)                               | . 82 |

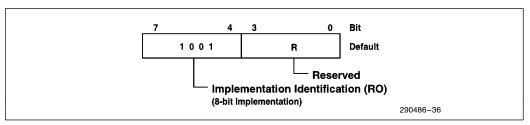

| 6.1.3.7 ECPCFGA—ECP Configuration A Register (ECP Mode)                       | . 83 |

| 6.1.3.8 ECPCFGB—ECP Configuration B Register (ECP Mode)                       | . 84 |

| 6.1.3.9 ECR ECP—Extended Control Register (ECP Mode)                          | . 85 |

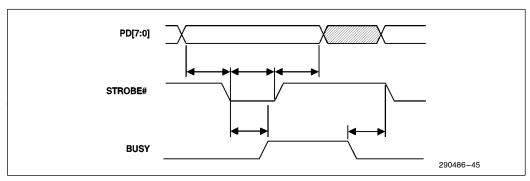

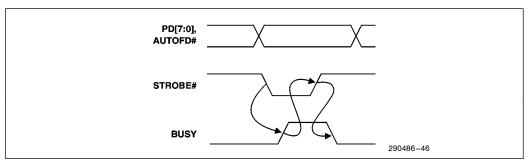

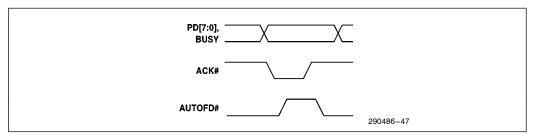

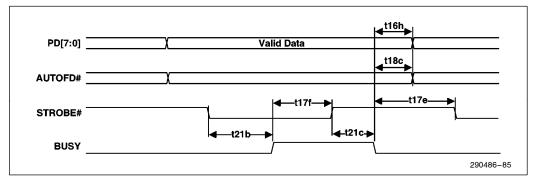

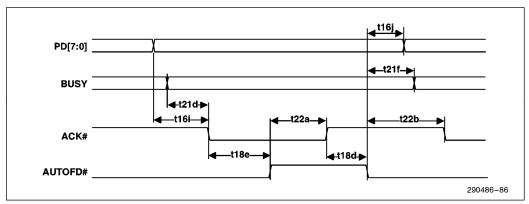

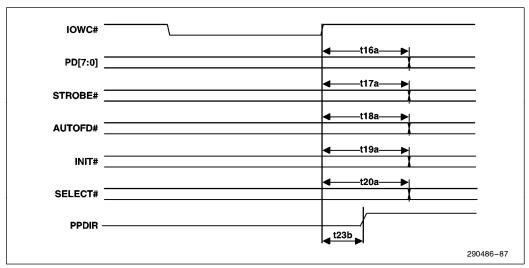

| 6.2 Parallel Port Operations                                                  | . 88 |

| 6.2.1 ISA-COMPATIBLE AND PS/2-COMPATIBLE MODES                                | . 88 |

| 6.2.2 EPP MODE                                                                | . 90 |

| 6.2.3 ECP MODE                                                                | . 92 |

| CONTENTS                                                          |

|-------------------------------------------------------------------|

| 6.2.3.1 FIFO Operations95                                         |

| 6.2.3.2 DMA Transfers95                                           |

| 6.2.3.3 Reset FIFO and DMA Terminal Count Interrupt95             |

| 6.2.3.4 Programmed I/O Transfers95                                |

| 6.2.3.5 Data Compression                                          |

| 6.2.4 PARALLEL PORT EXTERNAL BUFFER CONTROL 96                    |

| 6.2.5 PARALLEL PORT SUMMARY96                                     |

| <b>7.0 SERIAL PORT</b>                                            |

| 7.1 Register Description 97                                       |

| 7.1.1 THR(A,B)—TRANSMITTER HOLDING REGISTER                       |

| 7.1.2 RBR(A,B)—RECEIVER BUFFER REGISTER                           |

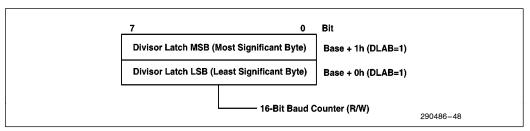

| 7.1.3 DLL(A,B), DLM(A,B)—DIVISOR LATCHES (LSB AND MSB) REGISTERS  |

| 7.1.3 DEL(A,B), DEM(A,B)—DIVISION EATONES (ESBAND MISB) REGISTERS |

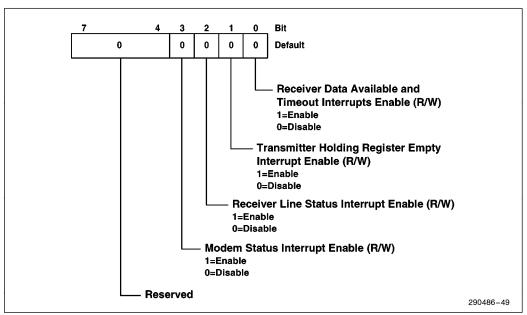

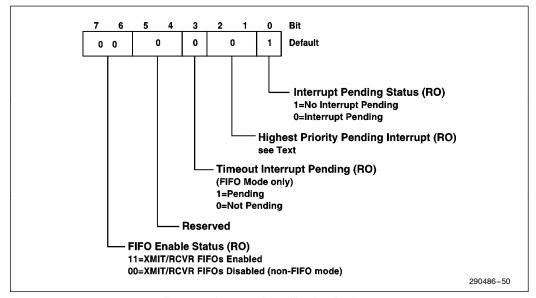

| 7.1.4 IER(A,B)—INTERRUPT IDENTIFICATION REGISTER                  |

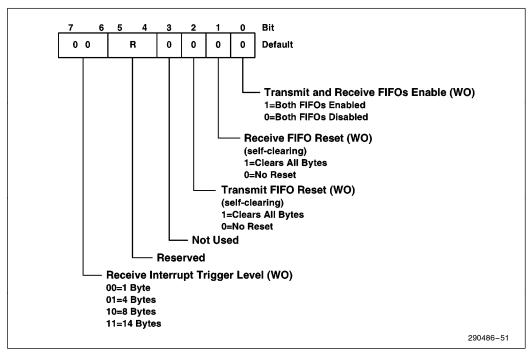

| 7.1.6 FCR(A,B)—FIFO CONTROL REGISTER                              |

| 7.1.6 FCR(A,B)—FIFO CONTROL REGISTER                              |

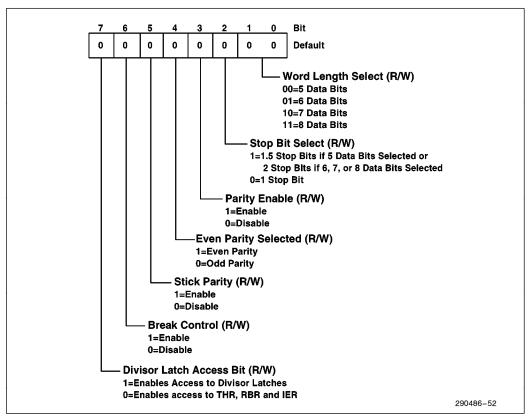

| 7.1.7 LCR(A,B)—LINE CONTROL REGISTER                              |

|                                                                   |

| 7.1.9 LSR(A,B)—LINE STATUS REGISTER                               |

| 7.1.10 MSH(A,B)—MODEM STATUS REGISTER                             |

| 7.1.11 3Ch(A,b)—3ChA1ChPAD REGISTEN                               |

| 7.2.1 FIFO INTERRUPT MODE OPERATION                               |

| 7.2.1 FIFO INTERROPT MODE OPERATION                               |

|                                                                   |

| 8.0 FLOPPY DISK CONTROLLER                                        |

| 8.1 Floppy Disk Controller Registers                              |

| 8.1.1 SRB—STATUS REGISTER B (EREG EN = 1)                         |

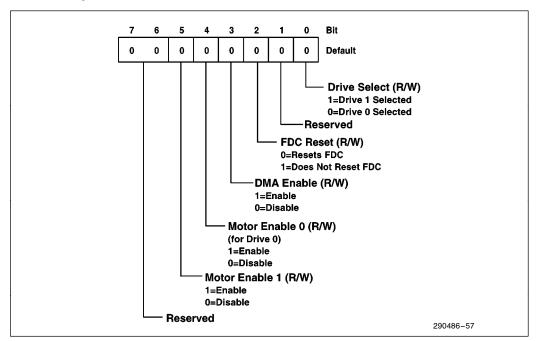

| 8.1.2 DOR—DIGITAL OUTPUT REGISTER                                 |

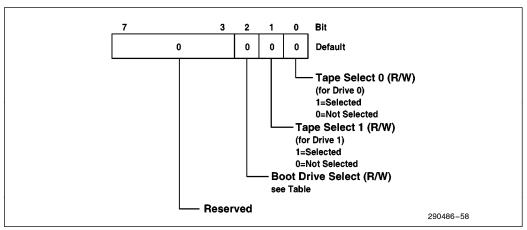

| 8.1.3 TDR—ENHANCED TAPE DRIVE REGISTER                            |

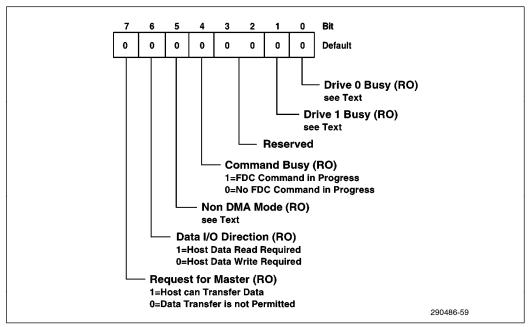

| 8.1.4 MSR—MAIN STATUS REGISTER                                    |

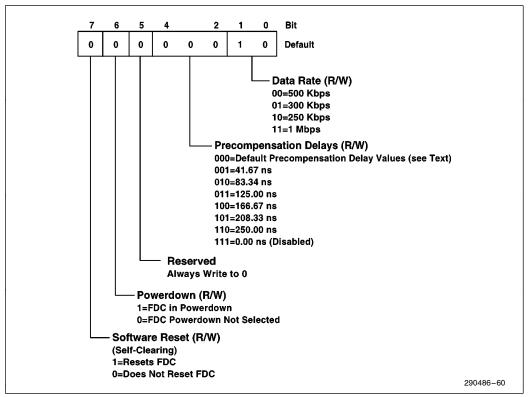

| 8.1.5 DSR—DATA RATE SELECT REGISTER                               |

| 8.1.6 FDCFIFO—FDC FIFO (DATA)                                     |

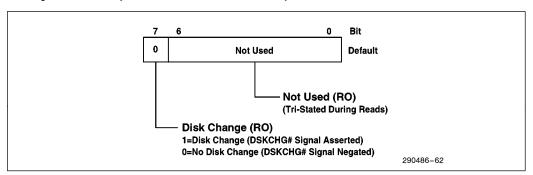

| 8.1.7 DIR—DIGITAL INPUT REGISTER                                  |

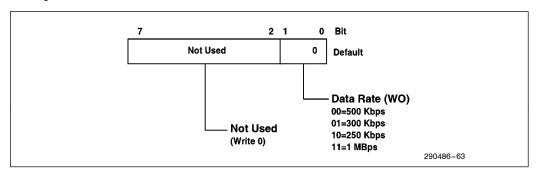

| 8.1.8 CCR—CONFIGURATION CONTROL REGISTER                          |

| 8.2 Reset                                                         |

| 8.2.1 HARD RESET AND CONFIGURATION REGISTER RESET 128             |

| 8.2.2 DOR RESET vs DSR RESET                                      |

| 8.3 DMA Transfers                                                 |

| 8.4 Controller Phases                                             |

| 8.4.1 COMMAND PHASE                                               |

| 8.4.2 EXECUTION PHASE                                             |

| CONTENTS                                                 | PAGE |

|----------------------------------------------------------|------|

| 8.4.2.1 Non-DMA Mode Transfers from the FIFO to the Host | 129  |

| 8.4.2.2 Non-DMA Mode Transfers from the Host to the FIFO | 129  |

| 8.4.2.3 DMA Mode Transfers from the FIFO to the Host     | 129  |

| 8.4.2.4 DMA Mode Transfers from the Host to the FIFO     | 129  |

| 8.4.3 DATA TRANSFER TERMINATION                          | 130  |

| 8.5 Command Set/Descriptions                             | 130  |

| 8.5.1 STATUS REGISTER ENCODING                           | 144  |

| 8.5.1.1 Status Register 0                                |      |

| 8.5.1.2 Status Register 1                                | 145  |

| 8.5.1.3 Status Register 2                                | 146  |

| 8.5.1.4 Status Register 3                                | 146  |

| 8.5.2 DATA TRANSFER COMMANDS                             | 147  |

| 8.5.2.1 Read Data                                        | 147  |

| 8.5.2.2 Read Deleted Data                                | 148  |

| 8.5.2.3 Read Track                                       | 149  |

| 8.5.2.4 Write Data                                       | 149  |

| 8.5.2.5 Verify                                           | 150  |

| 8.5.2.6 Format Track                                     | 151  |

| 8.5.2.7 Format Field                                     | 152  |

| 8.5.3 CONTROL COMMANDS                                   | 153  |

| 8.5.3.1 READ ID Command                                  |      |

| 8.5.3.2 RECALIBRATE Command                              | 153  |

| 8.5.3.3 DRIVE SPECIFICATION Command                      |      |

| 8.5.3.4 SEEK Command                                     | 154  |

| 8.5.3.5 SENSE INTERRUPT STATUS Command                   | 155  |

| 8.5.3.6 SENSE DRIVE STATUS Command                       |      |

| 8.5.3.7 SPECIFY Command                                  | 155  |

| 8.5.3.8 CONFIGURE Command                                | 156  |

| 8.5.3.9 VERSION Command                                  |      |

| 8.5.3.10 RELATIVE SEEK Command                           | 157  |

| 8.5.3.11 DUMPREG Command                                 |      |

| 8.5.3.12 PERPENDICULAR MODE Command                      | 157  |

| 8.5.3.13 POWERDOWN MODE Command                          |      |

| 8.5.3.14 PART ID Command                                 |      |

| 8.5.3.15 OPTION Command                                  |      |

| 8.5.3.16 SAVE Command                                    |      |

| 8.5.3.17 RESTORE Command                                 |      |

| 8.5.3.18 EORMAT AND WRITE Command                        | 160  |

| CONTENTS                                                                                                                                                                                                                                                                                                 | PAGE              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

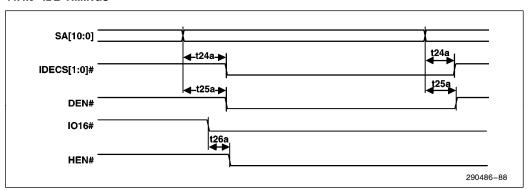

| 9.0 IDE INTERFACE  9.1 IDE Registers  9.2 IDE Interface Operation                                                                                                                                                                                                                                        | 160               |

| 10.0 POWER MANAGEMENT  10.1 Power Management Registers  10.2 Clock Power Management  10.3 FDC Power Management  10.4 Serial Port Power Management  10.5 Parallel Port Power Management                                                                                                                   |                   |

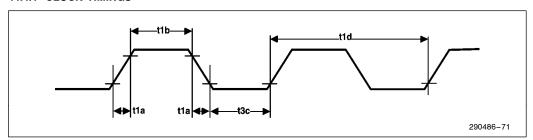

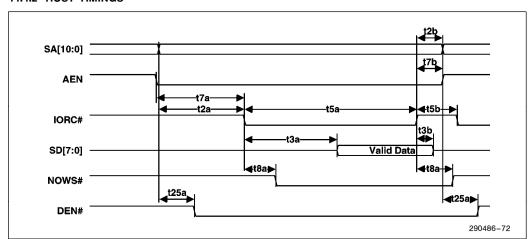

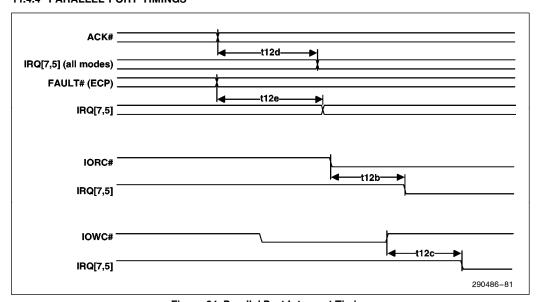

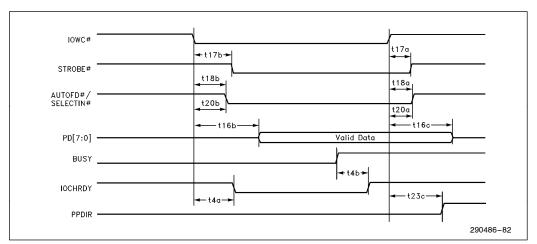

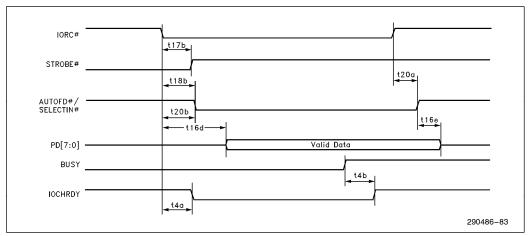

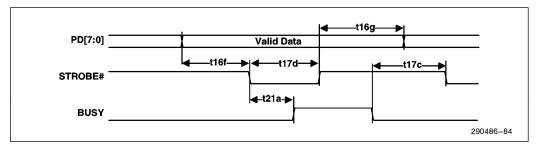

| 11.0 ELECTRICAL CHARACTERISTICS  11.1 Absolute Maximum Ratings  11.2 DC Characteristics  11.3 Oscillator  11.4 AC Characteristics  11.4.1 CLOCK TIMINGS  11.4.2 HOST TIMINGS  11.4.3 FDC TIMINGS  11.4.4 PARALLEL PORT TIMINGS  11.4.5 IDE TIMINGS  11.4.5 GAME PORT TIMINGS  11.4.7 SERIAL PORT TIMINGS |                   |

| 12.0 PINOUT AND PACKAGE INFORMATION  12.1 Pin Assignment  12.2 Package Characteristics                                                                                                                                                                                                                   | 186               |

| 13.0 DATA SEPARATOR CHARACTERISTICS FOR FLOPPY DISK MODE  13.1 Write Data Timing  13.2 Drive Control  13.3 Internal PLL                                                                                                                                                                                  |                   |

| APPENDIX A—FDC FOUR DRIVE SUPPORT  A.1 Floppy Disk Controller Interface Signals  A.2 DOR—Digital Output Register  A.3 TDR—Enhanced Tape Drive Register  A.4 MSR—Main Status Register                                                                                                                     | A-1<br>A-2<br>A-5 |

#### 1.0. OVERVIEW

The major functions of the 82091AA are shown in Figure 1. A brief description of each of these functions is presented in this section.

#### **Host Interface**

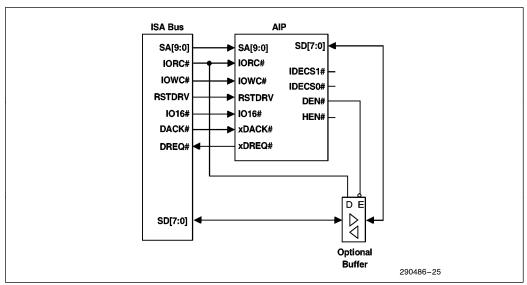

The 82091AA host interface is an 8-bit direct-drive (24 mA) ISA Bus/X-Bus interface that permits the CPU to access its registers through read/write operations in I/O space. These registers may be accessed by programmed I/O and/or DMA bus cycles. With the exception of the IDE Interface, all functions on the 82091AA require only 8-bit data accesses. The 16-bit access required for the IDE Interface is supported through the appropriate chip selects and data buffer enables from the 82091AA.

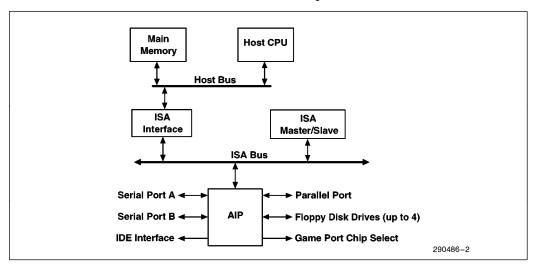

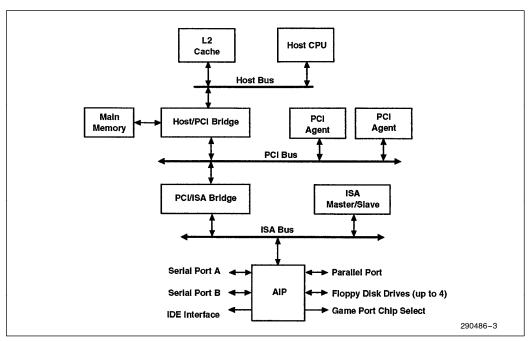

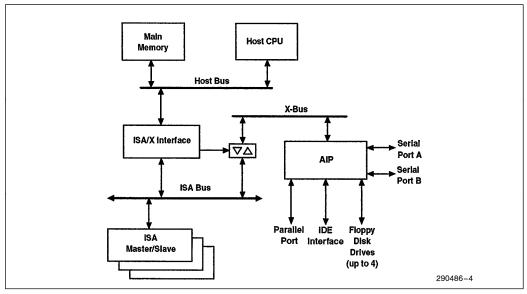

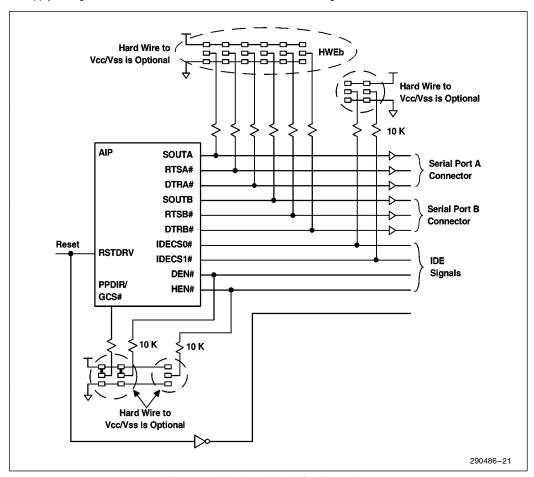

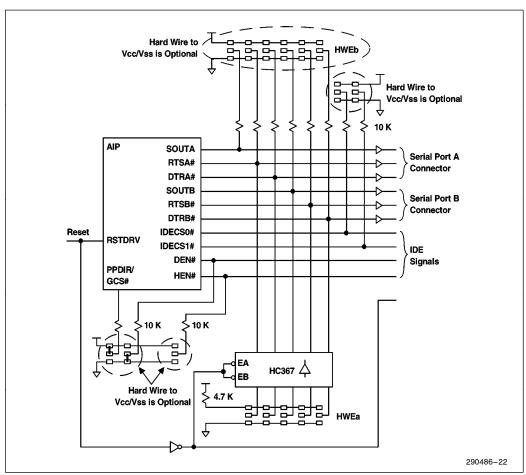

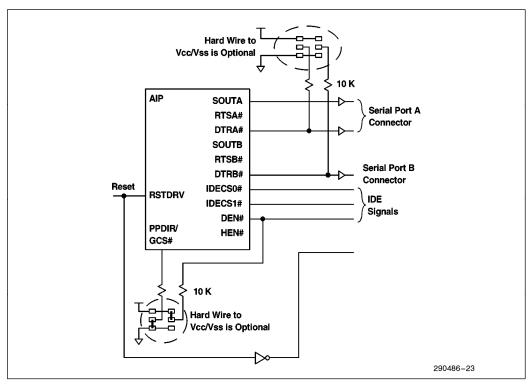

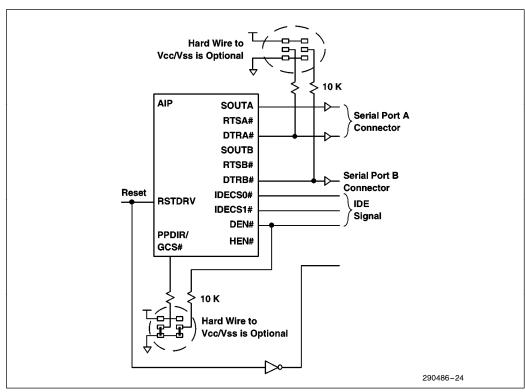

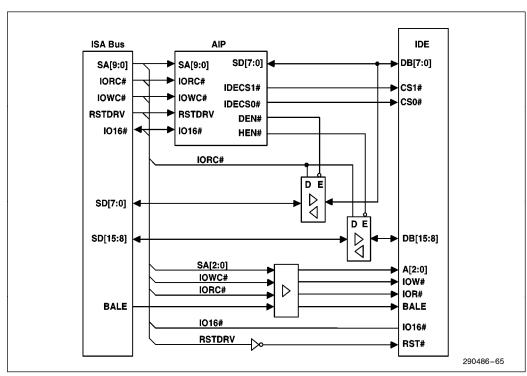

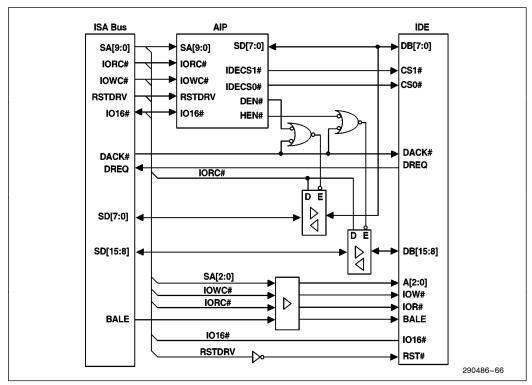

Figure 2 shows an example system implementation with the 82091AA located on an ISA Bus add-in card. This add-in card could also be used in a PCI-based system as shown in Figure 3. For motherboard implementations, the 82091AA can be located on the X-Bus as shown in Figure 4.

Figure 2. Block Diagram of the 82091AA on the ISA Bus

Figure 3. Block Diagram of the 82091AA in a PCI System

Figure 4. Block Diagram of the 82091AA on the X-Bus

#### Floppy Disk Controller

The 82091AA's enhanced floppy disk controller (FDC) incorporates several new features allowing for easy implementation in both the portable and desktop markets. It provides a low cost, small form factor solution targeted for 5.0V and 3.3V platforms. The FDC supports up to four drives.

The 82091AA's FDC implements these new features while remaining functionally compatible with 82078/82077SL/82077AA/8272A floppy disk controllers. Together, with a 24-MHz crystal, a resistor package and a device chip select, these devices allow for the most integrated solution available. The integrated analog PLL data separator has better performance than most board level discrete PLL implementations and can be operated at 1 Mbps/500 Kbps/300 Kbps/250 Kbps. A 16-byte FIFO substantially improves system performance and is ideal for multimaster systems (e.g., EISA).

#### Serial Ports

The 82091AA contains two independent serial ports that provide asynchronous communications that are equivalent to two 16550 UARTs. The serial ports have identical circuitry and provide the serial communication interface to a peripheral device or modem via Serial Port A and Serial Port B. Each serial port can be configured for one of eight address assignments. The standard PC/AT compatible logical address assignments for COM1, COM2, COM3, and COM4 are supported.

The serial ports perform serial-to-parallel conversion on data characters received from a peripheral device or modem, and parallel-to-serial conversion on data characters received from the host. The serial ports can operate in either FIFO mode or non-FIFO mode. In FIFO mode, a 16-byte transmit FIFO holds data from the host to be transmitted on the serial link and a 16-byte receive FIFO that buffers data from the serial link until read by the host.

The serial ports contain programmable baud rate generators that divide the internal reference clock by divisors of 1 to  $(2^{16}-1)$ , and produce a 16x clock for driving the transmitter and receiver logic. The internal reference clock can be programmed to support MIDI. The serial ports have complete modem-control capability and a prioritized interrupt system.

#### Parallel Port

The 82091AA provides a multi-function parallel port that transfers information between the host and peripheral device (e.g., printer). The parallel port interface contains nine control/status lines and an 8-bit data bus. The standard PC/AT compatible logical address assignments for LPT1, LPT2, and LPT3 are supported. The parallel port can be configured for one of four modes and supports the following IEEE Standard 1284 parallel interface protocol standards:

| Parallel Port        | Parallel Interface    |

|----------------------|-----------------------|

| Mode                 | Protocol              |

| ISA-Compatible Mode  | Compatibility, Nibble |

| PS/2-Compatible Mode | Byte                  |

| EPP Mode             | EPP                   |

| ECP Mode             | ECP                   |

For ISA-Compatible and PS/2-Compatible modes, software controls the handshake signals on the parallel port interface to transfer data between the host and peripheral device. Status and Control registers permit software to monitor the state of the peripheral device and generate handshake sequences.

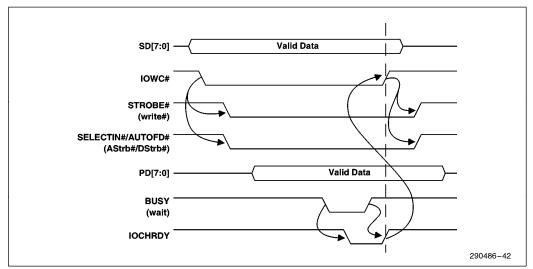

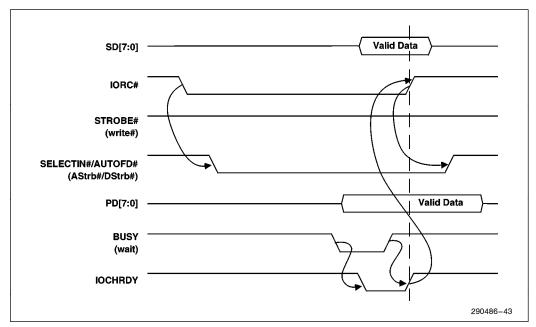

The EPP parallel port interface protocol increases throughput by specifying an automatic handshake sequence. In EPP mode, the 82091AA parallel port automatically generates this handshake sequence in hardware to transfer data between the host and peripheral device.

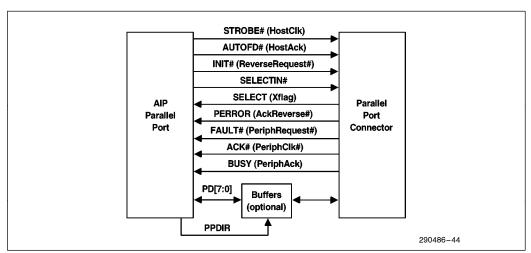

In addition to a hardware handshake on the parallel port interface, the ECP protocol specification also defines DMA and FIFO capability. To minimize processor overhead data transfer to/from a peripheral device, the 82091AA parallel port, in ECP mode, provides a 16-byte FIFO with DMA capability.

#### **IDE Interface**

The 82091AA supports the IDE (Integrated Drive Electronics) interface by providing chip selects and lower data byte control. Two chip selects are used to access registers on the IDE device. Separate lower and upper byte data control signals are provided. With these control signals, minimal external logic is needed to implement 16-bit IDE I/O and DMA interfaces.

#### **Game Port**

The 82091AA provides a game port chip select signal for use when the 82091AA is in an add-in card application. This function is assigned to I/O address location 201h. Note that when the 82091AA is located on the motherboard, this feature is not available.

#### **Power Management**

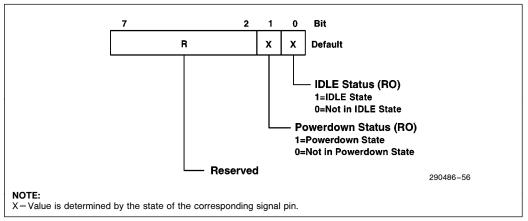

82091AA power management provides a mechanism for saving power when the device or a portion of the device is not being used. By programming the appropriate 82091AA registers, software can invoke power management to the entire 82091AA or selected modules within the 82091AA (e.g., floppy disk controller, serial port, or parallel port). There are two methods for applying power management—direct powerdown or auto powerdown. Direct powerdown turns off the clock to a particular module immediately placing that module into a powerdown state. This method removes the clock regardless of the activity or status of the module. When auto powerdown is invoked, the module enters a powerdown state (clock is turned off) after certain conditions are met and the module is in an idle state.

### 1.1. 3.3V/5V Operating Modes

The 82091AA can operate at a power supply of 3.3V, 5V or a mix of 3.3V and 5V. The mixed power supply mode provides 5V interfaces for the floppy disk controller and parallel port while all other 82091AA interfaces and internal logic (including the floppy disk controller and parallel port internal circuitry) operate at 3.3V. The mixed mode permits 5V floppy disk drives and parallel port peripherals to be used in a 3.3V system without external buffering.

#### NOTE:

3.3V operation is available only in the 82091AA.

#### 2.0. SIGNAL DESCRIPTION

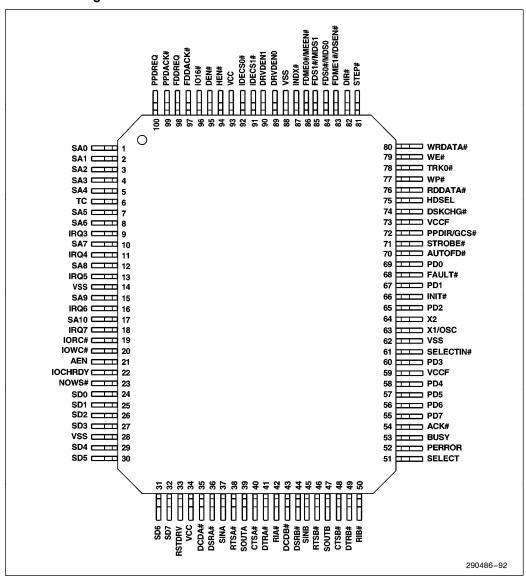

This section describes the 82091AA signals. The interface signals are shown in Figure 5 and described in the following tables. Signal descriptions are organized by functional group.

Note that the "#" symbol at the end of a signal name indicates the active, or asserted, state occurs when the signal is at a low voltage level. When "#" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working with a mixture of "active-low" and "active-high" signals. The term **assert**, or **assertion**, indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term **negate**, or **negation**, indicates that a signal is inactive.

The following notations are used to describe pin types:

- I Input Pin

- O Output Pin

- I/O Bi-Directional Pin

Figure 5. 82091AA Signals

## 2.1 Host Interface Signals

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ISA SIGNA      | LS   |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| SA[10:0]       | I    | SYSTEM ADDRESS BUS: The 82091AA decodes the standard ISA I/O address space using SA[9:0]. SA10 is used along with SA[9:0] to decode the extended register set of the ECP parallel port. SA[10:0] connects directly to the ISA system address bus.                                                                                                                                                                               |  |

| SD[7:0]        | 1/0  | SYSTEM DATA BUS: SD[7:0] is a bi-directional data bus. Data is written to and read from the 82091AA on these signal lines. SD[7:0] connect directly to the ISA system data bus.                                                                                                                                                                                                                                                 |  |

| IORC#          | I    | I/O READ COMMAND STROBE: IORC# is an I/O access read control signal. When a valid internal address is decoded by the 82091AA and IORC# is asserted, data at the decoded address location is driven onto the SD[7:0] signal lines.                                                                                                                                                                                               |  |

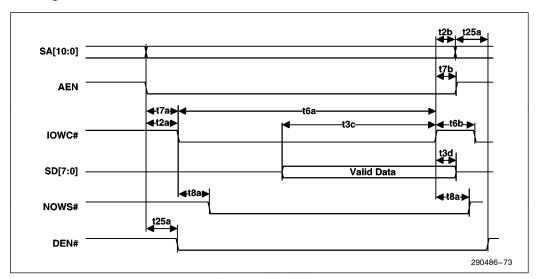

| IOWC#          | I    | I/O WRITE COMMAND STROBE: IOWC# is an I/O access write control signal. When a valid internal address is decoded by the 82091AA and IOWC# is asserted, data on the SD[7:0] signal lines is written into the decoded address location at the rising edge of IOWC#.                                                                                                                                                                |  |

| NOWS#          | 0    | NO WAIT-STATES: End data transfer signal. The 82091AA asserts NOWS# when a valid internal address is decoded by the 82091AA and the IORC# or IOWC# signal is asserted. This reduces the total bus cycle time by eliminating the wait-states associated with the default 8-bit I/O cycles. NOWS# is not asserted for IDE accesses or DMA accesses. This is an open drain output pin.                                             |  |

| IOCHRDY        | 0    | I/O CHANNEL READY: The 82091AA uses this signal for parallel port data transfers when the parallel port is in EPP mode. In this case, the 82091AA negates IOCHRDY to extend the cycle to allow for completion of transfers to/from the peripheral attached to the parallel port. When the parallel port is in EPP mode, the 82091AA negates IOCHRDY to lengthen the ISA Bus cycle if the parallel port BUSY signal is asserted. |  |

|                |      | The 82091AA also uses IOCHRDY during hardware configuration time (see Section 4.0, AIP Configuration). If IOWC#/IORC# is asserted to the 82091AA during hardware configuration time, the 82091AA negates IOCHRDY until hardware configuration time is completed. This is an open drain output pin.                                                                                                                              |  |

| AEN            | I    | ADDRESS ENABLE: AEN is used during DMA cycles to prevent the 82091AA from misinterpreting DMA cycles from valid I/O cycles. When negated, AEN indicates that the 82091AA may respond to address and I/O commands addressed to the 82091AA. When asserted, AEN informs the 82091AA that a DMA transfer is occurring. When AEN is asserted and a xDACK# signal is asserted, the 82091AA responds to the cycle as a DMA cycle.     |  |

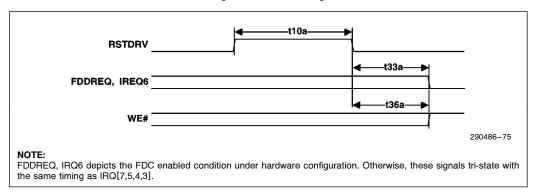

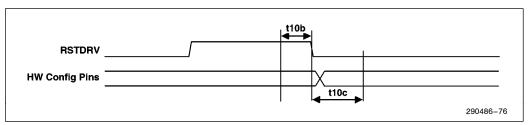

| RSTDRV         | I    | RESET DRIVE: RSTDRV forces the 82091AA to a known state. All 82091AA registers are set to their default state.                                                                                                                                                                                                                                                                                                                  |  |

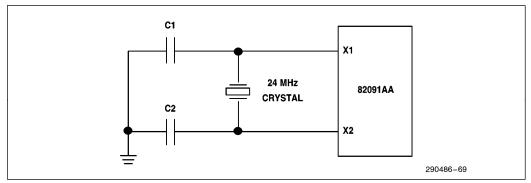

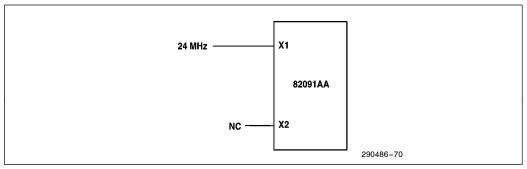

| X1/OSC         | I    | CRYSTAL1/OSCILLATOR: Main clock input signal can be a 24 MHz crystal connected across X1 and X2 or a 24 MHz TTL level clock input connected to X1.                                                                                                                                                                                                                                                                              |  |

| X2             | I    | <b>CRYSTAL2:</b> This signal pin is connected to one side of the crystal when a crystal oscillator is used to provide the main clock. If an external oscillator/clock is connected to X1, this pin is not used and left unconnected.                                                                                                                                                                                            |  |

## 2.1 Host Interface Signals (Continued)

| Signal<br>Name | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DMA SIGNA      | LS     |                                                                                                                                                                                                                                                                                                                                                                                       |  |

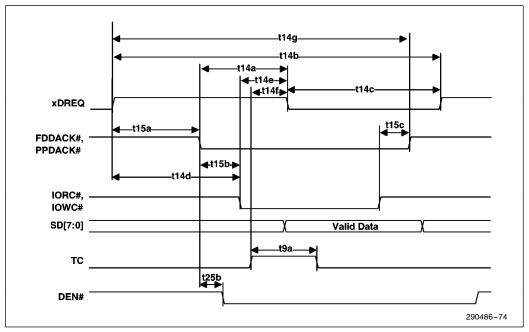

| FDDREQ         | 0      | <b>FLOPPY DISK CONTROLLER DMA REQUEST:</b> The 82091AA asserts FDDREQ to request service from a DMA controller for the FDC module. This signal is enabled/disabled by bit 3 of the Digital Output Register (DOR). When disabled, FDDREQ is tri-stated.                                                                                                                                |  |

| FDDACK#        | I      | <b>FLOPPY DISK CONTROLLER DMA ACKNOWLEDGE:</b> The DMA controller asserts this signal to acknowledge the FDC DMA request. When asserted, the IORC# and IOWC# inputs are enabled during DMA transfers. This signal is enabled/disabled by bit 3 of the DOR.                                                                                                                            |  |

| PPDREQ         | 0      | PARALLEL PORT DMA REQUEST: Parallel port DMA service request to the system DMA controller. This signal is only used when the parallel port is in ECP hardware mode and is always negated when the parallel port is not in this mode. In ECP hardware mode DMA requests are enabled/disabled by bit 3 of the ECP Extended Control Register (ECR). When disabled, PPDREQ is tri-stated. |  |

| PPDACK#        | l      | <b>PARALLEL PORT DMA ACKNOWLEDGE:</b> The DMA controller asserts this signal to acknowledge the parallel port DMA request. When asserted the IORC# and IOWC# inputs are enabled during DMA transfers. This signal is enabled/disabled by bit 3 of the ECR Register.                                                                                                                   |  |

| TC             | I      | <b>TERMINAL COUNT:</b> The system DMA controller asserts TC to indicate it has reached the last programmed data transfer. TC is accepted only when FDDACK# or PPDACK# is asserted.                                                                                                                                                                                                    |  |

| INTERRUPT      | SIGNAL | S                                                                                                                                                                                                                                                                                                                                                                                     |  |

| IRQ3, IRQ4     | 0      | INTERRUPT 3 AND 4: IRQ3 and IRQ4 are associated with the serial ports and can be programmed (via the AIPCFG2 Register) to be either active high or active low. These signals can be configured for a particular serial channel via hardware configuration (at powerup) or by software configuration.                                                                                  |  |

|                |        | Under Hardware Configuration IRQ3 is used as a serial port interrupt if the serial port is configured at address locations 2F8h–2FFh or 2E8h–2EFh. IRQ4 is used as a serial port interrupt if the serial port is configured at address locations 3F8h–3FFh or 3E8h–3EFh.                                                                                                              |  |

|                |        | Under Software configuration                                                                                                                                                                                                                                                                                                                                                          |  |

|                |        | IRQ3 and IRQ4 are independently configured (i.e., the IRQ does not automatically track the communication port address assignment).                                                                                                                                                                                                                                                    |  |

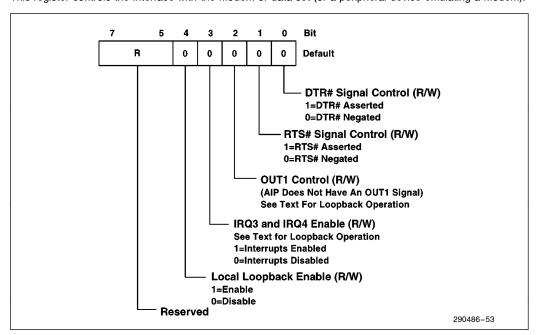

|                |        | These interrupts are enabled/disabled globally via bit 3 of the serial port Modem Control Register (MCR) and for specific conditions via the Interrupt Enable Register (IER). IRQ3 and IRQ4 are tri-stated when not enabled.                                                                                                                                                          |  |

| IRQ5, IRQ7     | 0      | INTERRUPT REQUEST 5: IRQ5 and IRQ7 are associated with the parallel port and can be programmed (via AIPCFG2 Register) to be either active high or active low. Either IRQ5 or IRQ7 is enabled/disabled via PCFG1 Register to signal a parallel port interrupt. The interrupt not selected is disabled and tri-stated.                                                                  |  |

|                |        | During hardware configuration (see Section 4.0, AIP Configuration), IRQ5 is used if the parallel port is assigned to 278h–27Fh and IRQ7 is used if the parallel port interrupt is assigned to either 3BCh–3BFh or 378h–37Fh.                                                                                                                                                          |  |

# 2.1 Host Interface Signals (Continued)

| Signal<br>Name | Туре                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|----------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| INTERR         | INTERRUPT SIGNALS (Continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| IRQ6           | 0                             | INTERRUPT REQUEST 6: IRQ6 is associated with the floppy disk controller and can be programmed (via the AIPCFG2 Register) to be either active high or active low. In non-DMA mode this signal is asserted to signal when a data transfer is ready. IRQ6 is also asserted to signal the completion of the execution phase for certain FDC commands. This signal is enabled/disabled by the DMAGATE bit in the Digital Output Register of the FDC. The signal is tri-stated when disabled. |  |  |  |

## 2.2 Floppy Disk Controller Interface

| Signal<br>Name       | Туре | Description                                                                                                                                                                                     |  |

|----------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RDDATA#              | I    | READ DATA: Serial data from the disk drive.                                                                                                                                                     |  |

| WRDATA#              | 0    | WRITE DATA: MFM serial data to the disk drive. Precompensation value is selectable through software.                                                                                            |  |

| HDSEL                | 0    | <b>HEAD SELECT:</b> Selects which side of a disk is to be accessed. When asserted (low), side 1 is selected. When negated (high), side 0 is selected.                                           |  |

| STEP#                | 0    | STEP: STEP# supplies step pulses (asserted) to the drive to move the head between the tracks during a seek operation.                                                                           |  |

| DIR#                 | 0    | DIRECTION: Controls the direction the head moves when a step signal is present. The head moves toward the center when DIR # is asserted and away from the center when negated.                  |  |

| WE#                  | 0    | <b>WRITE ENABLE:</b> WE # is a disk drive control signal. When asserted, WE # enables the head to write to the disk.                                                                            |  |

| TRK0#                | I    | TRACK0: The disk drive asserts this signal to indicate that the head is on track 0.                                                                                                             |  |

| INDX#                | I    | INDEX: The disk drive asserts this signal to indicate the beginning of the track.                                                                                                               |  |

| WP#                  | I    | <b>WRITE PROTECT:</b> The disk drive asserts this signal to indicate that the disk drive is write-protected.                                                                                    |  |

| DSKCHG               | I    | <b>DISK CHANGE:</b> The disk drive asserts this signal to indicate that the drive door has been opened. The state of this signal input is available in the Digital Input Register (DIR#).       |  |

| DRIVDEN0<br>DRIVDEN1 | 0    | <b>DRIVE DENSITY:</b> These signals are used by the disk drive to configure the drive for the appropriate media density. These signals are controlled by the FDC's Drive Specification Command. |  |

### 2.2 Floppy Disk Controller Interface (Continued)

| Signal<br>Name                | Туре | Description                                                                                                                                                                                                                                                                                                            |  |

|-------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

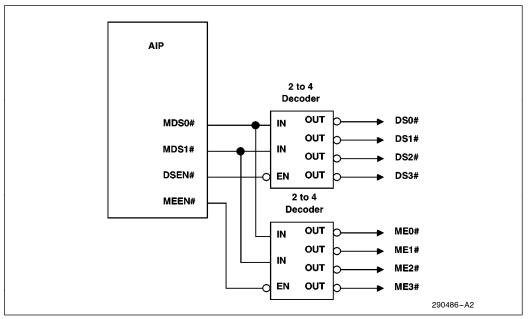

| FDME1#/<br>DSEN#(1)           | 0    | FLOPPY DRIVE MOTOR ENABLE 1, IDLE, OR DRIVE SELECT ENABLE: This signal pin has two functions <sup>(1)</sup> . FDME1# is the motor enable for drive 1. FDME1# is directly controlled via the Digital Output Register (DOR) and is a function of the mapping based on the BOOTSEL bits in the Tape Drive Register (TDR). |  |

|                               |      | The Drive Select Enable (DSEN#) function is only used in a four floppy drive system (see Appendix A, FDC Four Drive Support).                                                                                                                                                                                          |  |

| FDS1#/<br>MDS1 <sup>(1)</sup> | 0    | FLOPPY DRIVE SELECT1, POWERDOWN, OR MOTOR DRIVE SELECT 1: This signal pin has two functions(1). FDS1 # is the floppy drive select for drive 1. FDS1 # is controlled by the select bits in the DOR and is a function of the mapping based on the BOOTSEL bits in the TDR.                                               |  |

|                               |      | The Motor Drive Select 1 (MDS1) function is only used in a four floppy drive system (see Appendix A, FDC Four Drive Support).                                                                                                                                                                                          |  |

| FDME0#/<br>MEEN#(1)           | 0    | FLOPPY DRIVE MOTOR ENABLE 0 OR MOTOR ENABLE ENABLE: This signal pin has two functions <sup>(1)</sup> . FDME0# is the motor enable for drive 0. FDME0# is directly controlled via the Digital Output Register (DOR) and is a function of the mapping based on the BOOTSEL bits in the Tape Drive Register (TDR).        |  |

|                               |      | The Motor Enable Enable (MEEN#) function is only used in a four floppy drive system (see Appendix A, FDC Four Drive Support).                                                                                                                                                                                          |  |

| FDS0#/<br>MDS0(1)             | 0    | FLOPPY DRIVE SELECT 0 OR MOTOR DRIVE SELECT 0: This signal pin has two functions <sup>(1)</sup> . FDS0# is the floppy drive select for drive 0. This output is controlled by the drive select bits in the DOR and is a function of the mapping based on BOOTSEL bits in the TDR.                                       |  |

|                               |      | The Motor Drive Select 0 (MDS0) function is only used in a four floppy drive system (see Appendix A, FDC Four Drive Support).                                                                                                                                                                                          |  |

## NOTE:

1. The function selected for these pins is based on the FDDQTY bit in the FCFG1 Register as shown in the following table.

| Signal Pin   | 2 Drive System<br>(FDDQTY=0) | 4 Drive System<br>(FDDQTY = 1) |

|--------------|------------------------------|--------------------------------|

| FDME1#/DSEN# | FDME1#                       | DSEN#                          |

| FDS1#/MDS1#  | FDS1#                        | MDS1                           |

| FDME0#/MEEN# | FDME0#                       | MEEN#                          |

| FDS0#/MDS0   | FDS0#                        | MDS0                           |

When FDDQTY = 1, these signal pins are used to control an external decoder for a four floppy disk drive system as described in Appendix A, FDC Four Drive Support.

## 2.3 Serial Port Interface

Serial Port A signal names end in the letter A and Serial Port B signal names end in the letter B. Serial Port A and B signals have the same functionality.

| Signal<br>Name  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

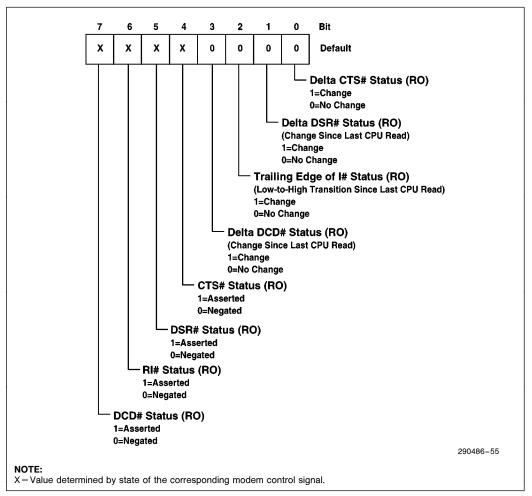

| CTSA#,<br>CTSB# | I    | CLEAR TO SEND: When asserted, this signal indicates that the modem or data set is ready to exchange data. The CTS# signal is a modem status input whose condition the CPU can determine by reading the CTS bit in Modem Status Register (MSR) for the appropriate serial port. The CTS bit is the compliment of the CTS# signal. The DCTS bit in the MSR indicates whether the CTS# input has changed state since the previous reading of the MSR. CTS# has no effect on the transmitter.                          |  |

| DCDA#,<br>DCDB# | I    | DATA CARRIER DETECT: When asserted, this signal indicates that the data carrier has been detected by the modem or data set. The DCD# signal is a modem status whose condition the CPU can determine by reading the DCD bit in the MSR for the appropriate serial port. The DCD bit is the compliment of the DCD# signal. The DDCD bit in the MSR indicates whether the DCD# input has changed state since the previous reading of the MSR. DCD# has no effect on the transmitter.                                  |  |

| DSRA#,<br>DSRB# | I    | DATA SET READY: When asserted, this signal indicates that the modem or data set is ready to establish the communications link with the serial port module. The DSR# signal is a modem status whose condition the CPU can determine by reading the DSR bit in the MSR for the appropriate serial channel. The DSR bit is the compliment of the DSR# signal. The DSR bit in the MSR indicates whether the DSR# input has changed state since the previous reading of the MSR. DSR# has no effect on the transmitter. |  |

| DTRA#,<br>DTRB# | 1/0  | <b>DATA TERMINAL READY:</b> DTRA # /DTRB # are outputs during normal system operations. When asserted, this signal indicates to the modem or data set that the serial port module is ready to establish a communications link. The DTR # signal can be asserted via the Modem Control Register (MCR). A hard reset negates this signal.                                                                                                                                                                            |  |

|                 |      | Hardware Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                 |      | These signals are only inputs during hardware configuration time (RSTDRV asserted and for a short time after RSTDRV is negated). (See Section 4.0, AIP Configuration.)                                                                                                                                                                                                                                                                                                                                             |  |

| RIA#, RIB#      | I    | RING INDICATOR: When asserted, this signal indicates that a telephone ringing signal has been received by the modem or data set. The RI# signal is a modem status input whose condition the CPU can determine by reading the RI bit in the MSR for the appropriate serial channel. The RI bit is the compliment of the RI# signal. The TERI bit in the MSR indicates whether the RI# input has changed from low to high since the previous reading of the MSR.                                                     |  |

## 2.3 Serial Port Interface (Continued)

| Signal<br>Name  | Туре | Description                                                                                                                                                                                                                                                                                                |

|-----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RTSA#,<br>RTSB# | 1/0  | REQUEST TO SEND: RTSA#/RTSB# are outputs during normal system operations. When asserted, this signal informs the modem or data set that the serial port module is ready to exchange data. The RTS# signal can be asserted via the RTS bit in the Modem Control Register. A hard reset negates this signal. |

|                 |      | Hardware Configuration                                                                                                                                                                                                                                                                                     |

|                 |      | These signals are only inputs during hardware configuration time (RSTDRV asserted and for a short time after RSTDRV is negated). (See Section 4.0, AIP Configuration.)                                                                                                                                     |

| SINA, SINB      | I    | <b>SERIAL INPUT:</b> Serial data input from the communications link. (Peripheral device, modem, or data set.)                                                                                                                                                                                              |

| SOUTA,<br>SOUTB | 1/0  | <b>SERIAL OUTPUT:</b> SOUTA/SOUTB are serial data outputs to the communications link during normal system operations. (Peripheral device, modem, or data set.) The SOUT signal is set to a marking state (logic 1) after a hard reset.                                                                     |

|                 |      | Test Mode                                                                                                                                                                                                                                                                                                  |

|                 |      | In test mode (selected via the SACFG2 or SBCFG2 Registers), the baudout from the baud rate generator is output on SOUTx.                                                                                                                                                                                   |

|                 |      | Hardware Configuration                                                                                                                                                                                                                                                                                     |

|                 |      | These signals are only inputs during hardware configuration time (RSTDRV asserted and for a short time after RSTDRV is negated). (See Section 4.0, AIP Configuration.)                                                                                                                                     |

## 2.4 IDE Interface

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                                              |  |

|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IO16#          | I    | <b>16-BIT I/O:</b> This signal is driven by I/O devices on the ISA Bus to indicate support for 16-bit I/O bus cycles. The IDE interface asserts this signal to the 82091AA to indicate support for 16-bit transfers. For IDE transfers, the 82091AA asserts HEN# when IO16# is asserted. |  |

| IDECS[1:0] #   | 1/0  | <b>IDE CHIP SELECT:</b> IDECS[1:0] # are outputs during normal system operation and are chip selects for the IDE interface. IDECS[1:0] # select the Command Block Registers of the IDE device and are decoded from SA[9:3] and AEN.                                                      |  |

|                |      | Hardware Configuration                                                                                                                                                                                                                                                                   |  |

|                |      | These signals are only inputs during hardware configuration time (RSTDRV asserted). (See Section 4.0, AIP Configuration.)                                                                                                                                                                |  |

# 2.4 IDE Interface (Continued)

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEN#           | 1/0  | <b>DATA ENABLE:</b> DEN# is an output during normal system operations and is a data enable for an external data buffer for all 82091AA and IDE accesses. The SD[7:0] signals can be connected directly to the ISA. In this case, the DEN# signal is not used. However, an external buffer can be used to isolate the SD[7:0] signals from the 240 pF loading of the ISA Bus. With an external buffer implementation, DEN# controls the external buffers for transfers to/from the ISA Bus. |

|                |      | Hardware Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                |      | This signal is only an input during hardware configuration time (RSTDRV asserted). (See Section 4.0, AIP Configuration.)                                                                                                                                                                                                                                                                                                                                                                   |

| HEN#           | I/O  | IDE UPPER DATA TRANSCEIVER ENABLE: HEN# is an output during normal system operations and is a high byte data transceiver enable signal for the IDE hard disk drive interface. HEN# is asserted for I/O accesses to the IDE data register when the drive asserts IO16#.                                                                                                                                                                                                                     |

|                |      | Hardware Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                |      | This signal is only an input during hardware configuration time (RSTDRV asserted). (See Section 4.0, AIP Configuration.)                                                                                                                                                                                                                                                                                                                                                                   |

## 2.5 Parallel Port External Buffer Control/Game Port

| Signal<br>Name | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PPDIR/GCS#     | 1/0  | PARALLEL PORT DIRECTION (PPDIR) or GAME PORT CHIP SELECT (GCS#): This signal is an output during normal operations and provides the PPDIR and GCS# functions as follows:                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |      | PPDIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |      | This signal pin functions as a parallel port direction control output when the 82091AA is configured for software motherboard mode (SWMB). For configuration details, see Section 4.0, AIP Configuration. If external buffers are used on PD[7:0], PPDIR can be used to control the buffer direction. The 82091AA drives this signal low when PD[7:0] are outputs and the 82091AA drives this signal high when PD[7:0] are inputs. Note that if a configuration mode other than SWMB is selected, this signal pin is a game port chip select and does not track the PD[7:0] signal direction. |

|                |      | GCS#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                |      | This signal pin functions as a game port chip select output when 82091AA configuration is set for Software Add-In (SWAI), Hardware Basic (HWB), or Hardware Extended (HWE) modes. When the host accesses I/O address 201h, GCS# is asserted.                                                                                                                                                                                                                                                                                                                                                  |

|                |      | Hardware Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                |      | This signal is only an input during hardware configuration time (RSTDRV asserted). (See Section 4.0, AIP Configuration.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

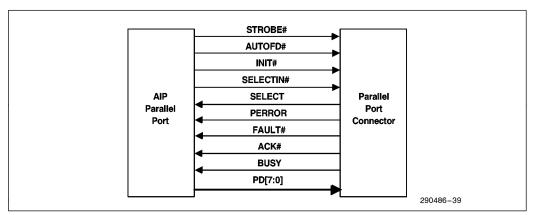

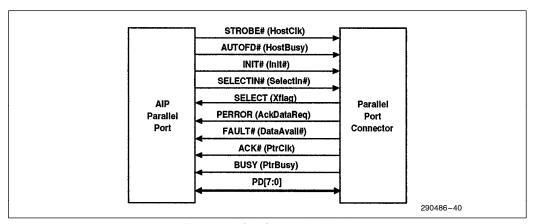

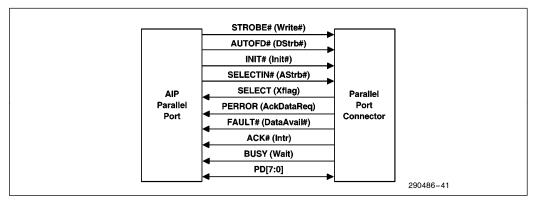

### 2.6 Parallel Port Interface

The 82091AA parallel port is a multi-function interface that can be configured for one of four hardware modes (see Section 4.0, AIP Configuration). The hardware modes are ISA-Compatible, PS/2-Compatible, EPP, and ECP modes. These parallel port modes support the compatibility, nibble, byte, EPP and ECP parallel interface protocols described in the IEEE 1284 standard. The operation and use of the interface signal pins are a function of the parallel port hardware mode selected and the protocol used.

Table 1 shows a matrix of the 82091AA parallel port signal names and corresponding signal names for each of the protocols. Sections 2.6.1–2.6.5 provide a signal description for the five interface protocols. Note that the 82091AA hardware operations are the same for Compatibility and Nibble protocols. The signals, however, are controlled and used differently via software and the peripheral device.

Table 1. Parallel Port Signal Name Cross Reference

| 82091AA<br>Signal<br>Names | Compatibility<br>Protocol Signal<br>Names | Nibble Protocol<br>Signal Names | Byte Protocol<br>Signal Names | EPP Protocol<br>Signal Names | ECP Protocol<br>Signal Names |

|----------------------------|-------------------------------------------|---------------------------------|-------------------------------|------------------------------|------------------------------|

| STROBE#                    | Strobe#                                   |                                 | HostCLK                       | Write#                       | HostClk                      |

| BUSY                       | Busy                                      | PtrBusy                         | PtrBusy                       | Wait#                        | PeriphAck                    |

| ACK#                       | Ack#                                      | PtrClk                          | PtrClk                        | Intr                         | PeriphClk#                   |

| SELECT                     | Select                                    | Xflag                           | Xflag                         | Xflag                        | Xflag                        |

| PERROR                     | PError                                    | AckDataReq                      | AckDataReq                    | AckDataReq                   | AckReverse#                  |

| FAULT#                     | Fault#                                    | DataAvail#                      | DataAvail#                    | DataAvail#                   | PeriphRequest#               |

| INIT#                      | Init#                                     | _                               | _                             | Init#                        | ReverseRequest#              |

| AUTOFD#                    | AutoFd#                                   | HostBusy                        | HostBusy                      | DStrb#                       | HostAck                      |

| PD[7:0]                    | Data[8:1]                                 | _                               | Data[8:1]                     | Data[8:1]                    | Data[8:1]                    |

| SELECTIN#                  | SelectIn#                                 | _                               | _                             | AStrb#                       | ECP Mode                     |

#### NOTE:

Not all parallel port signal pins are used for certain parallel port interface protocols. These signals are labeled "--".

## 2.6.1 COMPATIBILITY PROTOCOL SIGNAL DESCRIPTION

Except for the data bus, the 82091AA and compatibility protocol signal names are the same. For the data bus, the 82091AA signal names PD[7:0] corresponds to the compatibility protocol signal names Data[8:1].

| 82091AA<br>Signal<br>Name | Туре | Compatibility Protocol Signal Name and Description                                                                                                                                                                                                                                                         |  |

|---------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| STROBE#                   | 0    | <b>STROBE:</b> The host asserts STROBE# to latch data into the peripheral device's input latch. This signal is controlled via the PCON Register.                                                                                                                                                           |  |

| BUSY                      | I    | <b>BUSY:</b> BUSY is asserted by the peripheral to indicate that the peripheral device is not ready to receive data. The status of this signal line is reported in the PSTAT Register.                                                                                                                     |  |

| ACK#                      | I    | <b>ACKNOWLEDGE:</b> The printer asserts this signal to indicate that it has received the data and is ready for new data. The status of this signal line is reported in the PSTAT Register.                                                                                                                 |  |

| SELECT                    | I    | <b>SELECT:</b> SELECT is asserted by the peripheral device to indicate that the device is on line. The status of this signal line is reported in the PSTAT Register.                                                                                                                                       |  |

| PERROR                    | ı    | <b>PAPER ERROR:</b> The peripheral device asserts PERROR to indicate that it has encountered an error in the paper path. The exact meaning varies from peripheral device to peripheral device. The status of this signal line is reported in the PSTAT Register.                                           |  |

| FAULT#                    | I    | <b>FAULT:</b> FAULT# is asserted by the peripheral device to indicate that an error has occurred. The status of this signal line is reported in the PSTAT Register.                                                                                                                                        |  |

| INIT#                     | 0    | <b>INITIALIZE:</b> The host asserts INIT# to issue a hardware reset to the peripheral device. This signal is controlled via the PCON Register.                                                                                                                                                             |  |

| AUTOFD#                   | 0    | <b>AUTO FEED:</b> AUTOFD# is asserted by the host to put the peripheral device into auto-line feed mode. This means that when software asserts this signal, the printer is instructed to advance the paper one line for each carriage return encountered. This signal is controlled via the PCON Register. |  |

| PD[7:0]                   | 0    | DATA: Forward channel data.                                                                                                                                                                                                                                                                                |  |

| SELECTIN#                 | 0    | <b>SELECT INPUT:</b> SELECTIN# is asserted by the host to select a peripheral device. This signal is controlled via the PCON Register.                                                                                                                                                                     |  |

### 2.6.2 NIBBLE PROTOCOL SIGNAL DESCRIPTION

The Nibble protocol assigns the following signal operation to the parallel port pins. The name in bold at the beginning of the signal description column is the Nibble protocol signal name. The terms **assert** and **negate** are used in accordance with the 82091AA signal name as described at the beginning of Section 2.0. For example, AUTOFD# (HostBusy) asserted refers to AUTOFD# (HostBusy) at a low level.

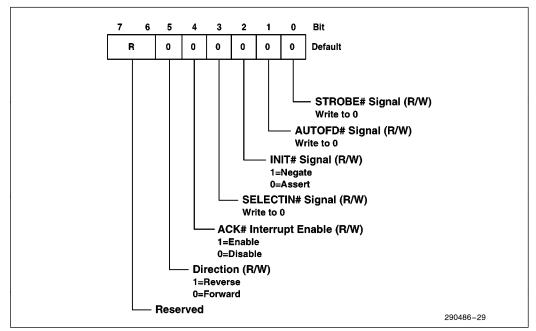

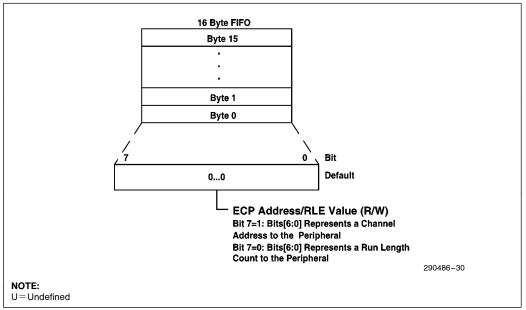

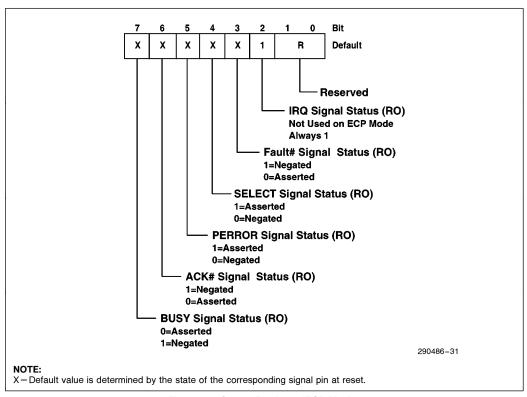

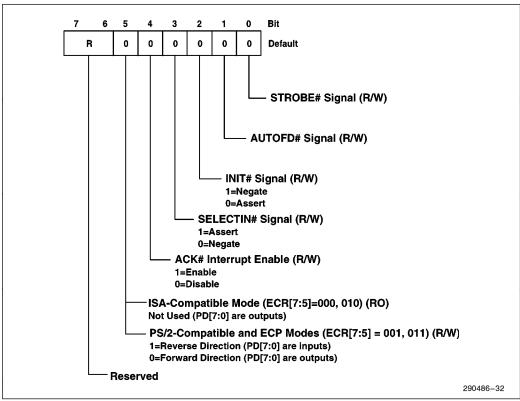

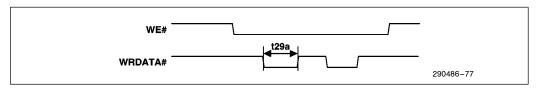

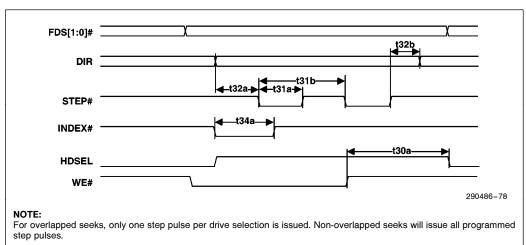

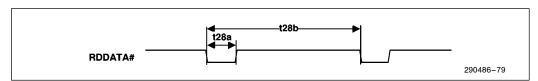

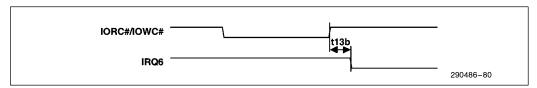

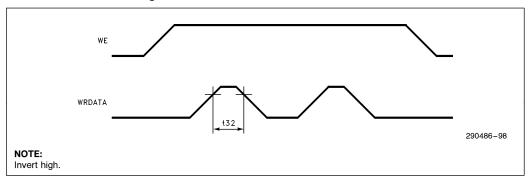

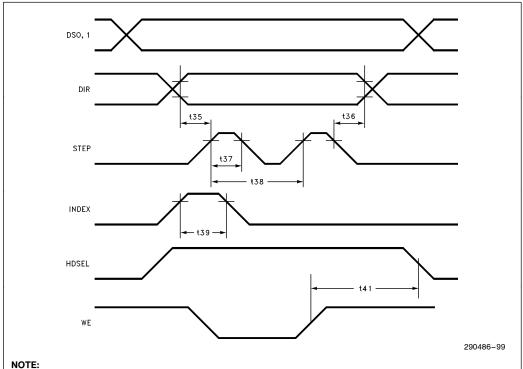

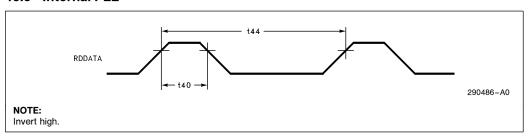

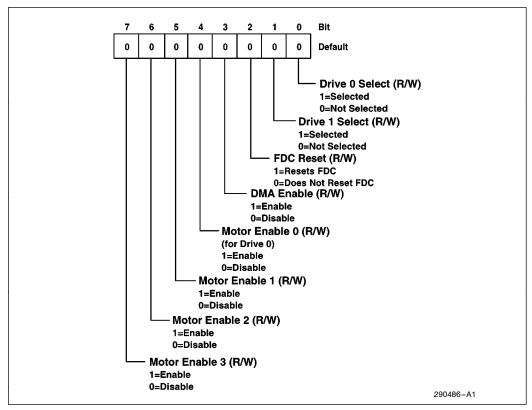

| 82091AA<br>Signal<br>Name | Туре | Nibble Protocol Signal Name and Description                                                                                                                                                                                                                                                                                                                                              |  |