January 1990 Revised December 1998

#### 74ACT899

## 9-Bit Latchable Transceiver with Parity Generator/Checker

#### **General Description**

The ACT899 is a 9-bit to 9-bit parity transceiver with transparent latches. The device can operate as a feed-through transceiver or it can generate/check parity from the 8-bit data busses in either direction. The ACT899 features independent latch enables for the A-to-B direction and the B-to-A direction, a select pin for ODD/EVEN parity, and separate error signal output pins for checking parity.

#### **Features**

- Latchable transceiver with output sink of 24 mA

- Option to select generate parity and check or "feed-through" data/parity in directions A-to-B or B-to-A

- Independent latch enable for A-to-B and B-to-A directions

- Select pin for ODD/EVEN parity

- $\blacksquare$   $\overline{\text{ERRA}}$  and  $\overline{\text{ERRB}}$  output pins for parity checking

- Ability to simultaneously generate and check parity

- May be used in system applications in place of the 280

- May be used in system applications in place of the 657 and 373 (no need to change T/R to check parity)

#### **Ordering Code:**

| Order Number   Package Number |      | Package Description                                                   |

|-------------------------------|------|-----------------------------------------------------------------------|

| 74ACT899QC                    | V28A | 28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450" Square |

Device also available in Tape and Reel. Specify by appending suffix letter "X" to the ordering code.

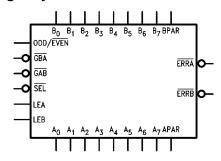

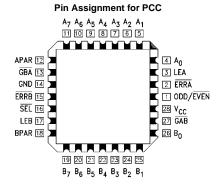

#### **Logic Symbol**

#### **Connection Diagram**

$\mathsf{FACT^{\scriptscriptstyle\mathsf{TM}}}$  is a trademark of Fairchild Semiconductor Corporation.

#### **Pin Descriptions**

| Pin Names                      | Description                                                                     |  |  |  |  |

|--------------------------------|---------------------------------------------------------------------------------|--|--|--|--|

| A <sub>0</sub> -A <sub>7</sub> | A Bus Data Inputs/Data Outputs                                                  |  |  |  |  |

| B <sub>0</sub> -B <sub>7</sub> | B Bus Data Inputs/Data Outputs                                                  |  |  |  |  |

| APAR, BPAR                     | A and B Bus Parity Inputs                                                       |  |  |  |  |

| ODD/EVEN                       | ODD/EVEN Parity Select,<br>Active LOW for EVEN Parity                           |  |  |  |  |

| GBA, GAB                       | Output Enables for A or B Bus,<br>Active LOW                                    |  |  |  |  |

| SEL                            | Select Pin for Feed-Through or Generate Mode, LOW for Generate Mode             |  |  |  |  |

| LEA, LEB                       | Latch Enables for A and B Latches,<br>HIGH for Transparent Mode                 |  |  |  |  |

| ERRA, ERRB                     | Error Signals for Checking Generated Parity with Parity In, LOW if Error Occurs |  |  |  |  |

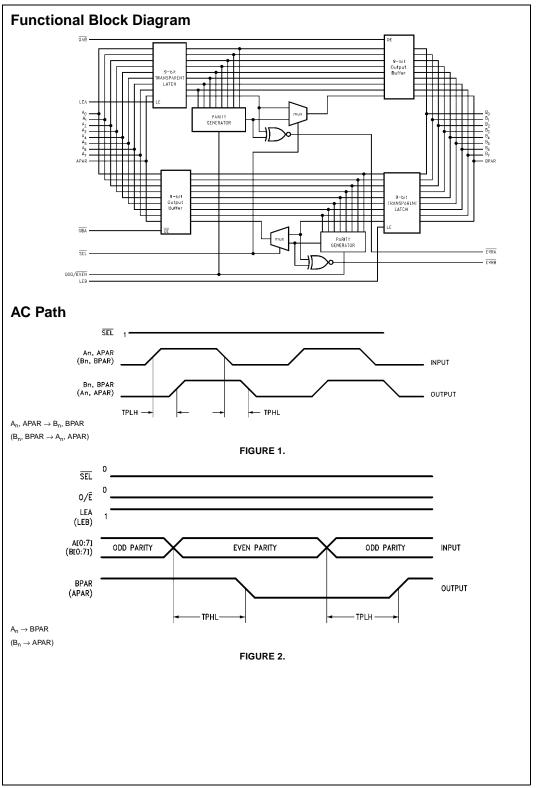

#### **Functional Description**

The ACT899 has three principal modes of operation which are outlined below. These modes apply to both the A-to-B and B-to-A directions.

- Bus A (B) communicates to Bus B (A), parity is generated and passed on to the B (A) Bus as BPAR (APAR). If LEB (LEA) is HIGH and the Mode Select (SEL) is LOW, the parity generated from B[0:7] (A[0:7]) can be checked and monitored by ERRB (ERRA).

- Bus A (B) communicates to Bus B (A) in a feed-through mode if SEL is HIGH. Parity is still generated and checked as ERRA and ERRB in the feed-through mode (can be used as an interrupt to signal a data/parity bit error to the CPU).

- Independent Latch Enables (LEA and LEB) allow other permutations of generating/checking (see Function Table).

#### **Function Table**

| Inputs |     |     | 3   |     | Operation                                                                                                                                                                                                                                                           |  |  |  |  |

|--------|-----|-----|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| GAB    | GBA | SEL | LEA | LEB |                                                                                                                                                                                                                                                                     |  |  |  |  |

| Н      | Н   | Х   | Х   | Χ   | Busses A and B are 3-STATE.                                                                                                                                                                                                                                         |  |  |  |  |

| Н      | L   | L   | L   | Н   | Generates parity from B[0:7] based on O/Ē (Note 1). Generated parity → APAR.<br>Generated parity checked against BPAR and output as ĒRRĒ.                                                                                                                           |  |  |  |  |

| Н      | L   | L   | Н   | Н   | Generates parity from B[0:7] based on O/ $\overline{E}$ . Generated parity $\to$ APAR. Generated parity checked against BPAR and output as $\overline{ERRB}$ . Generated parity also fed back hrough the A latch for generate/check as $\overline{ERRA}$ .          |  |  |  |  |

| Н      | L   | L   | Х   | L   | Generates parity from B latch data based on O/Ē. Generated parity → APAR. Generated parity checked against latched BPAR and output as ERRB.                                                                                                                         |  |  |  |  |

| Н      | L   | Н   | Х   | Н   | BPAR/B[0:7] $\rightarrow$ APAR/A0:7] Feed-through mode. Generated parity checked against BPAR and output as $\overline{\text{ERRB}}$ .                                                                                                                              |  |  |  |  |

| Н      | L   | Н   | Н   | Н   | BPAR/B[0:7] → APAR/A[0:7]                                                                                                                                                                                                                                           |  |  |  |  |

|        |     |     |     |     | Feed-through mode. Generated parity checked against BPAR and output as ERRB. Generated parity also fed back through the A latch for generate/check as ERRA.                                                                                                         |  |  |  |  |

| L      | Н   | L   | Н   | L   | Generates parity for A[0:7] based on $O/\overline{E}$ . Generated parity $\to$ BPAR. Generated parity checked against APAR and output as $\overline{\text{ERRA}}$ .                                                                                                 |  |  |  |  |

| L      | Н   | L   | Н   | Н   | Generates parity from A[0:7] based on O/ $\overline{E}$ . Generated parity $\rightarrow$ BPAR. Generated parity checked against APAR and output as $\overline{ERRA}$ . Generated parity also fed back through the B latch for generate/check as $\overline{ERRB}$ . |  |  |  |  |

| L      | Н   | L   | L   | Х   | Generates parity from A latch data based on $O/\overline{E}$ . Generated parity $\to$ BPAR. Generated parity checked against latched APAR and output as $\overline{ERRA}$ .                                                                                         |  |  |  |  |

| L      | Н   | Н   | Н   | L   | $APAR/A[0:7] \to BPAR/B[0:7]$                                                                                                                                                                                                                                       |  |  |  |  |

|        |     |     |     |     | Feed-through mode. Generated parity checked against APAR and output as ERRA.                                                                                                                                                                                        |  |  |  |  |

| L      | Н   | Н   | Н   | Н   | $APAR/A[0:7] \to BPAR/B[0:7]$                                                                                                                                                                                                                                       |  |  |  |  |

|        |     |     |     |     | Feed-through mode. Generated parity checked against APAR and output as ERRA. Generated parity also fed back through the B latch for generate/check as ERRB.                                                                                                         |  |  |  |  |

H = HIGH Voltage Level

Note 1:  $O/\overline{E} = ODD/\overline{EVEN}$

L = LOW Voltage Level

X = Immaterial

#### Absolute Maximum Ratings(Note 2)

Supply Voltage (V $_{CC}$ ) -0.5V to +7.0V

DC Input Diode Current (I<sub>IK</sub>)

$\begin{array}{c} \text{V}_{\text{I}} = -0.5 \text{V} & -20 \text{ mA} \\ \text{V}_{\text{I}} = \text{V}_{\text{CC}} + 0.5 \text{V} & +20 \text{ mA} \\ \text{DC Input Voltage (V_{\text{I}})} & -0.5 \text{V to V}_{\text{CC}} + 0.5 \text{V} \end{array}$

DC Output Diode Current (I<sub>OK</sub>)

$\begin{aligned} & \text{V}_{\text{O}} = -0.5 \text{V} & -20 \text{ mA} \\ & \text{V}_{\text{O}} = \text{V}_{\text{CC}} + 0.5 \text{V} & +20 \text{ mA} \\ & \text{DC Output Voltage (V}_{\text{O}}) & -0.5 \text{V to V}_{\text{CC}} + 0.5 \text{V} \end{aligned}$

DC Output Source

or Sink Current ( $I_O$ )  $\pm 50$  mA

DC V<sub>CC</sub> or Ground Current

per Output Pin ( $I_{CC}$  or  $I_{GND}$ )  $\pm 50$  mA Storage Temperature ( $T_{STG}$ )  $-65^{\circ}$ C to  $+150^{\circ}$ C

DC Latch-Up Source or

Sink Current ±300 mA Junction Temperature (T<sub>J</sub>) 140°C

### Recommended Operating Conditions

$V_{IN}$  from 0.8V to 2.0V  $V_{CC}$  @ 4.5V, 5.5V

Note 2: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation of FACT™ circuits outside databook specifications.

#### **DC Electrical Characteristics**

| Symbol           | Parameter                      | v <sub>cc</sub> | T <sub>A</sub> = +25°C |      | T <sub>A</sub> = -40°C to +85°C | Units | Conditions                                 |

|------------------|--------------------------------|-----------------|------------------------|------|---------------------------------|-------|--------------------------------------------|

|                  |                                | (V)             | Typ Gu                 |      | aranteed Limits                 | İ     |                                            |

| V <sub>IH</sub>  | Minimum HIGH Level             | 4.5             | 1.5                    | 2.0  | 2.0                             | V     | $V_{OUT} = 0.1V$                           |

|                  | Input Voltage                  | 5.5             | 1.5                    | 2.0  | 2.0                             |       | or V <sub>CC</sub> – 0.1V                  |

| V <sub>IL</sub>  | Maximum LOW Level              | 4.5             | 1.5                    | 0.8  | 0.8                             | V     | V <sub>OUT</sub> = 0.1V                    |

|                  | Input Voltage                  | 5.5             | 1.5                    | 0.8  | 0.8                             |       | or V <sub>CC</sub> – 0.1V                  |

| V <sub>OH</sub>  | Minimum HIGH Level             | 4.5             | 4.49                   | 4.4  | 4.4                             | V     | $I_{OUT} = -50 \mu A$                      |

|                  | Output Voltage                 | 5.5             | 5.49                   | 5.4  | 5.4                             |       |                                            |

|                  |                                |                 |                        |      |                                 |       | $V_{IN} = V_{IL}$ or $V_{IH}$              |

|                  |                                | 4.5             |                        | 3.86 | 3.76                            | V     | $I_{OH} = -24 \text{ mA}$                  |

|                  |                                | 5.5             |                        | 4.86 | 4.76                            |       | $I_{OH} = -24 \text{ mA} \text{ (Note 3)}$ |

| V <sub>OL</sub>  | Maximum LOW Level              | 4.5             | 0.001                  | 0.1  | 0.1                             | V     | $I_{OUT} = 50 \mu A$                       |

|                  | Output Voltage                 | 5.5             | 0.001                  | 0.1  | 0.1                             |       |                                            |

|                  |                                |                 |                        |      |                                 |       | $V_{IN} = V_{IL}$ or $V_{IH}$              |

|                  |                                | 4.5             |                        | 0.36 | 0.44                            | V     | $I_{OL} = 24 \text{ mA}$                   |

|                  |                                | 5.5             |                        | 0.36 | 0.44                            |       | I <sub>OL</sub> = 24 mA (Note 3)           |

| I <sub>IN</sub>  | Maximum Input                  | 5.5             |                        | ±0.1 | ±1.0                            | μΑ    | $V_I = V_{CC}$ , GND                       |

|                  | Leakage Current                |                 |                        |      |                                 |       |                                            |

| I <sub>OZ</sub>  | Maximum 3-STATE                | 5.5             |                        | ±0.5 | ±5.0                            | μΑ    | $V_I = V_{IL}, V_{IH}$                     |

|                  | Leakage Current                |                 |                        |      |                                 |       | $V_O = V_{CC}$ , GND                       |

| I <sub>CCT</sub> | Maximum I <sub>CC</sub> /Input | 5.5             | 0.6                    |      | 1.5                             | mA    | $V_{I} = V_{CC} - 2.1V$                    |

| I <sub>OLD</sub> | Minimum Dynamic                | 5.5             |                        |      | 75                              | mA    | V <sub>OLD</sub> = 1.65V Max               |

| I <sub>OHD</sub> | Output Current (Note 4)        | 5.5             |                        |      | -75                             | mA    | V <sub>OHD</sub> = 3.85V Min               |

| I <sub>CC</sub>  | Maximum Quiescent              | 5.5             |                        | 8.0  | 80.0                            | μΑ    | $V_{IN} = V_{CC}$                          |

|                  | Supply Current                 |                 |                        |      |                                 |       | or GND                                     |

Note 3: Maximum of 9 outputs loaded; thresholds on input associated with output under test.

Note 4: Maximum test duration 2.0 ms, one output loaded at a time.

#### **AC Electrical Characteristics**

|                  |                                                                    | V <sub>CC</sub> | $T_A = +25^{\circ}C$ $C_L = 50 \text{ pF}$ |     |      | T <sub>A</sub> = -40° | C to +85°C | Units |           |

|------------------|--------------------------------------------------------------------|-----------------|--------------------------------------------|-----|------|-----------------------|------------|-------|-----------|

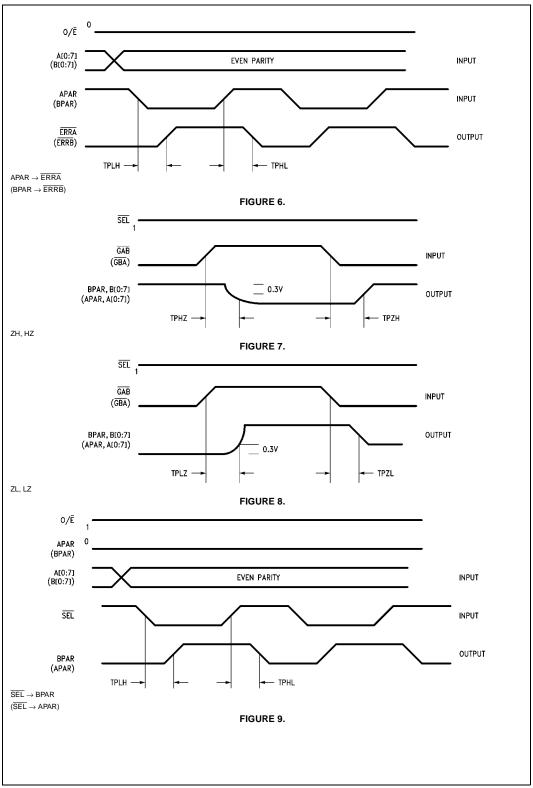

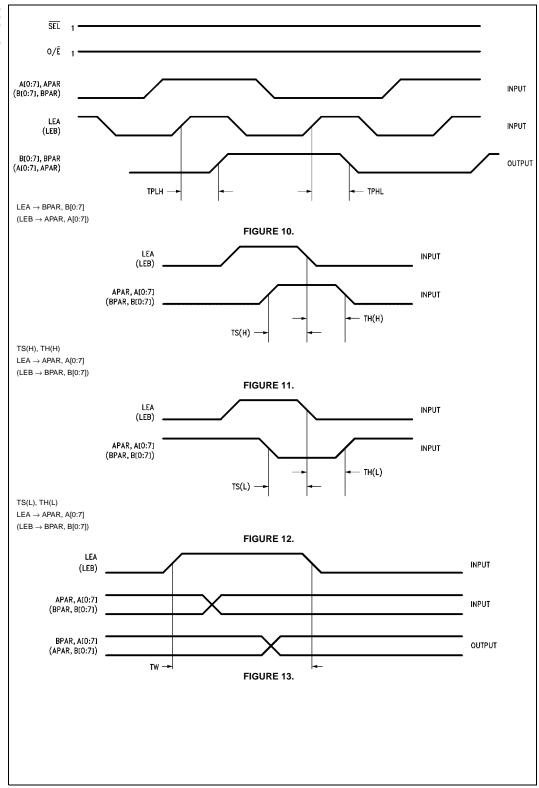

| Symbol           | Parameter                                                          | (V)             |                                            |     |      | C <sub>L</sub> =      | 50 pF      |       | Fig. No.  |

|                  |                                                                    | (Note 5)        | Min                                        | Тур | Max  | Min                   | Max        |       |           |

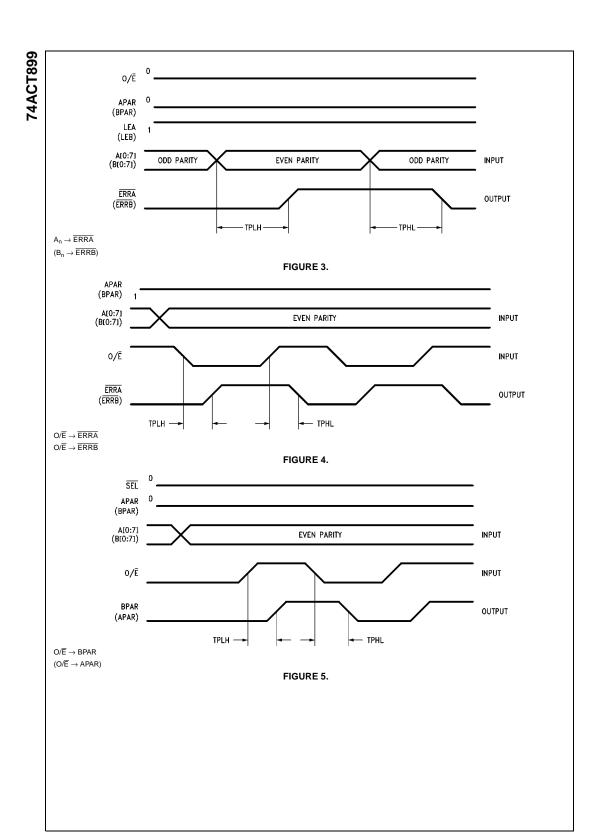

| t <sub>PLH</sub> | Propagation Delay                                                  | 5.0             | 2.5                                        | 7.5 | 11.5 | 2.5                   | 12.0       | ns    | Figure 1  |

| t <sub>PHL</sub> | A <sub>n</sub> , B <sub>n</sub> to B <sub>n</sub> , A <sub>n</sub> |                 |                                            |     |      |                       |            |       |           |

| t <sub>PLH</sub> | Propagation Delay                                                  | 5.0             | 1.5                                        | 6.0 | 8.5  | 1.5                   | 9.0        | ns    | Figure 1  |

| t <sub>PHL</sub> | APAR, BPAR to BPAR, APAR                                           |                 |                                            |     |      |                       |            |       |           |

| t <sub>PLH</sub> | Propagation Delay                                                  | 5.0             | 2.5                                        | 8.5 | 12.0 | 2.5                   | 12.5       | ns    | Figure 2  |

| t <sub>PHL</sub> | A <sub>n</sub> , B <sub>n</sub> to BPAR, APAR                      |                 |                                            |     |      |                       |            |       |           |

| t <sub>PLH</sub> | Propagation Delay                                                  | 5.0             | 2.0                                        | 8.0 | 11.5 | 2.0                   | 12.0       | ns    | Figure 3  |

| t <sub>PHL</sub> | $A_n$ , $B_n$ to $\overline{ERRA}$ , $\overline{ERRB}$             |                 |                                            |     |      |                       |            |       |           |

| t <sub>PLH</sub> | Propagation Delay                                                  | 5.0             | 2.0                                        | 8.0 | 11.5 | 2.0                   | 12.0       | ns    | Figure 4  |

| t <sub>PHL</sub> | ODD/EVEN to ERRA, ERRB                                             |                 |                                            |     |      |                       |            |       |           |

| t <sub>PLH</sub> | Propagation Delay                                                  | 5.0             | 2.5                                        | 8.0 | 11.5 | 2.5                   | 12.0       | ns    | Figure 5  |

| t <sub>PHL</sub> | ODD/EVEN to APAR, BPAR                                             |                 |                                            |     |      |                       |            |       |           |

| t <sub>PLH</sub> | Propagation Delay                                                  | 5.0             | 1.5                                        | 7.5 | 10.5 | 1.5                   | 11.5       | ns    | Figure 6  |

| t <sub>PHL</sub> | APAR, BPAR to ERRA, ERRB                                           |                 |                                            |     |      |                       |            |       |           |

| t <sub>PLH</sub> | Propagation Delay                                                  | 5.0             | 1.5                                        | 6.5 | 9.0  | 1.5                   | 9.5        | ns    | Figure 9  |

| t <sub>PHL</sub> | SEL to APAR, BPAR                                                  |                 |                                            |     |      |                       |            |       |           |

| t <sub>PLH</sub> | Propagation Delay                                                  | 5.0             | 2.5                                        | 7.0 | 10.5 | 2.5                   | 11.0       | ns    | Figure 10 |

| t <sub>PHL</sub> | LEB to A <sub>n</sub> , B <sub>n</sub>                             |                 |                                            |     |      |                       |            |       | Figure 11 |

| t <sub>PLH</sub> | Propagation Delay                                                  | 5.0             | 2.0                                        | 8.0 | 11.5 | 2.0                   | 12.0       | ns    | Figure 10 |

| t <sub>PHL</sub> | LEA to APAR, BPAR                                                  |                 |                                            |     |      |                       |            |       | Figure 11 |

| t <sub>PLH</sub> | Propagation Delay                                                  | 5.0             | 2.5                                        | 8.0 | 11.5 | 2.5                   | 12.0       | ns    | Figure 12 |

| $t_{PHL}$        | LEA, LEB to ERRA, ERRB                                             |                 |                                            |     |      |                       |            |       |           |

| t <sub>PZH</sub> | Output Enable Time                                                 | 5.0             | 2.5                                        | 7.0 | 10.5 | 2.5                   | 11.0       | ns    | Figure 7  |

| $t_{PZL}$        | $\overline{GBA}$ or $\overline{GAB}$ to $A_n$ , $B_n$              |                 |                                            |     |      |                       |            |       | Figure 8  |

| t <sub>PZH</sub> | Output Enable Time                                                 | 5.0             | 1.5                                        | 6.0 | 9.0  | 1.5                   | 9.5        | ns    | Figure 7  |

| $t_{PZL}$        | GBA or GAB to BPAR or APAR                                         |                 |                                            |     |      |                       |            |       | Figure 8  |

| t <sub>PHZ</sub> | Output Disable Time                                                | 5.0             | 1.5                                        | 6.5 | 9.5  | 1.5                   | 9.5        | ns    | Figure 7  |

| t <sub>PHL</sub> | GBA or GAB to A <sub>n</sub> , B <sub>n</sub>                      |                 |                                            |     |      |                       |            |       | Figure 8  |

| t <sub>PHZ</sub> | Output Disable Time                                                | 5.0             | 1.5                                        | 6.5 | 9.5  | 1.5                   | 9.5        | ns    | Figure 7  |

| t <sub>PLZ</sub> | GBA or GAB to BPAR, APAR                                           |                 |                                            |     |      |                       |            |       | Figure 8  |

**Note 5:** Voltage Range 5.0 is 5.0V ± 0.5V.

#### **AC Operating Requirements**

| Symbol         | Parameter                                         | v <sub>cc</sub> | $T_A = +25$ °C<br>$C_L = 50 \text{ pF}$ | $T_A = -40$ °C to $+85$ °C<br>$C_L = 50$ pF | Units | Fig. No.  |

|----------------|---------------------------------------------------|-----------------|-----------------------------------------|---------------------------------------------|-------|-----------|

|                |                                                   | (Note 6)        | Guarantee                               | d Minimum                                   |       |           |

| ts             | Setup Time, HIGH or LOW                           | 5.0             | 3.0                                     | 3.0                                         | ns    | Figure 11 |

|                | A <sub>n</sub> , B <sub>n</sub> , PAR to LEA, LEB |                 |                                         |                                             |       | Figure 12 |

| t <sub>H</sub> | Hold Time, HIGH or LOW                            | 5.0             | 1.5                                     | 1.5                                         | ns    | Figure 11 |

|                | A <sub>n</sub> , B <sub>n</sub> , PAR to LEA, LEB |                 |                                         |                                             |       | Figure 12 |

| t <sub>W</sub> | Pulse Width for LEB, LEA                          | 5.0             | 4.0                                     | 4.0                                         | ns    | Figure 13 |

**Note 6:** Voltage Range  $5.0 = 5.0V \pm 0.5V$ .

#### Capacitance

| Symbol          | Symbol Parameter              |     | Units | Conditions             |

|-----------------|-------------------------------|-----|-------|------------------------|

| C <sub>IN</sub> | Input Capacitance             | 4.5 | pF    | V <sub>CC</sub> = 5.0V |

| C <sub>PD</sub> | Power Dissipation Capacitance | 210 | pF    | V <sub>CC</sub> = 5.0V |

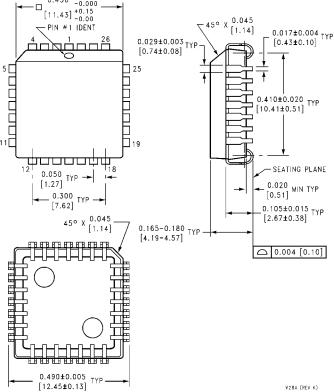

# Physical Dimensions inches (millimeters) unless otherwise noted 0.450 +0.006 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -0.000 -

28-Lead Plastic Lead Chip Carrier (PLCC), JEDEC MO-047, 0.450" Square Package Number V28A

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com