Toshiba

TC74AC109F 데이터시트 - Toshiba

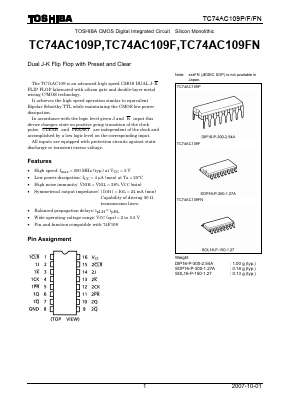

Dual J-K Flip Flop with Preset and Clear

The TC74AC109 is an advanced high speed CMOS DUAL J- K FLIP FLOP fabricated with silicon gate and double-layer metal wiring C2MOS technology.

It achieves the high speed operation similar to equivalent Bipolar Schottky TTL while maintaining the CMOS low power dissipation.

In accordance with the logic level given J and K input this device changes state on positive going transition of the clock pulse. CLEAR and PRESET are independent of the clock and accomplished by a low logic level on the corresponding input.

All inputs are equipped with protection circuits against static discharge or transient excess voltage.

FEATUREs

• High speed: fmax = 200 MHz (typ.) at VCC = 5 V

• Low power dissipation: ICC = 4 μA (max) at Ta = 25°C

• High noise immunity: VNIH = VNIL = 28% VCC (min)

• Symmetrical output impedance: |IOH| = IOL = 24 mA (min)

Capability of driving 50 Ω

transmission lines.

• Balanced propagation delays: tpLH ∼ − tpHL

• Wide operating voltage range: VCC (opr) = 2 to 5.5 V

• Pin and function compatible with 74F109