Micrel

SY89425JC 데이터시트 - Micrel

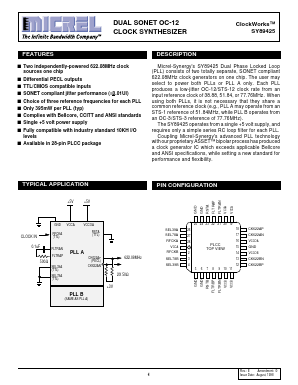

DESCRIPTION

Micrel-Synergys SY89425 Dual Phase Locked Loop (PLL) consists of two totally separate, SONET compliant 622.08MHz clock generators on one chip. The user may select to power both PLLs or PLL A only. Each PLL produces a low-jitter OC-12/STS-12 clock rate from an input reference clock of 38.88, 51.84, or 77.76MHz. When using both PLLs, it is not necessary that they share a common reference clock (e.g., PLL A may operate from an STS-1 reference of 51.84MHz, while PLL B operates from an OC-3/STS-3 reference of 77.76MHz).

FEATURES

■ Two independently-powered 622.08MHz clock sources one chip

■ Differential PECL outputs

■ TTL/CMOS compatible inputs

■ SONET compliant jitter performance (≤0.01UI)

■ Choice of three reference frequencies for each PLL

■ Only 395mW per PLL (typ)

■ Complies with Bellcore, CCITT and ANSI standards

■ Single +5 volt power supply

■ Fully compatible with industry standard 10KH I/O levels

■ Available in 28-pin PLCC package