Silicon Storage Technology

SST36VF1602-90-4C-EK 데이터시트 - Silicon Storage Technology

PRODUCT DESCRIPTION

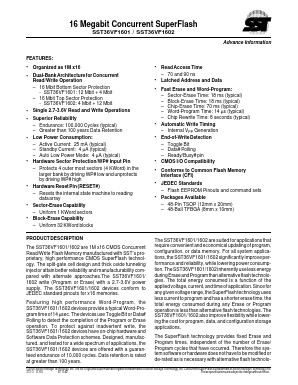

The SST36VF1601/1602 are 1M x16 CMOS Concurrent Read/Write Flash Memory manufactured with SST’s proprietary, high performance CMOS SuperFlash technology. The split-gate cell design and thick oxide tunneling injector attain better reliability and manufacturability compared with alternate approaches.The SST36VF1601/ 1602 write (Program or Erase) with a 2.7-3.6V power supply. The SST36VF1601/1602 devices conform to JEDEC standard pinouts for x16 memories.

FEATURES:

• Organized as 1M x16

• Dual-Bank Architecture for Concurrent

Read/Write Operation

– 16 Mbit Bottom Sector Protection

- SST36VF1601: 12 Mbit + 4 Mbit

– 16 Mbit Top Sector Protection

- SST36VF1602: 4 Mbit + 12 Mbit

• Single 2.7-3.6V Read and Write Operations

• Superior Reliability

– Endurance: 100,000 Cycles (typical)

– Greater than 100 years Data Retention

• Low Power Consumption:

– Active Current: 25 mA (typical)

– Standby Current: 4 µA (typical)

– Auto Low Power Mode: 4 µA (typical)

• Hardware Sector Protection/WP# Input Pin

– Protects 4 outer most sectors (4 KWord) in the

larger bank by driving WP# low and unprotects

by driving WP# high

• Hardware Reset Pin (RESET#)

– Resets the internal state machine to reading

data array

• Sector-Erase Capability

– Uniform 1 KWord sectors

• Block-Erase Capability

– Uniform 32 KWord blocks

• Read Access Time

– 70 and 90 ns

• Latched Address and Data

• Fast Erase and Word-Program:

– Sector-Erase Time: 18 ms (typical)

– Block-Erase Time: 18 ms (typical)

– Chip-Erase Time: 70 ms (typical)

– Word-Program Time: 14 µs (typical)

– Chip Rewrite Time: 8 seconds (typical)

• Automatic Write Timing

– Internal VPP Generation

• End-of-Write Detection

– Toggle Bit

– Data# Polling

– Ready/Busy# pin

• CMOS I/O Compatibility

• Conforms to Common Flash Memory

Interface (CFI)

• JEDEC Standards

– Flash EEPROM Pinouts and command sets

• Packages Available

– 48-Pin TSOP (12mm x 20mm)

– 48-Ball TFBGA (8mm x 10mm)