Solomon Systech

SSD1905 데이터시트 - Solomon Systech

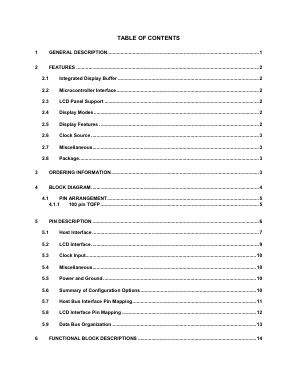

GENERAL DESCRIPTION

The SSD1905 is a graphics controller with built-in 80Kbyte SRAM display buffer, supporting color and mono LCD. The SSD1905 can support a wide range of active and passive panels, and interface with various CPUs. The advanced design, together with integration of memory and timing circuits make a low cost, low power, single chip solution to meet the handheld devices or appliances market needs, such as Pocket/Palm-size PCs and mobile communication devices.

FEATURES

Integrated Display Buffer

• Embedded 80K byte SRAM display buffer.

Microcontroller Interface

• Directly interfaces to :

Generic #1 bus interface with WAIT# signal

Generic #2 bus interface with WAIT# signal

Motorola MC68K

Motorola MC68EZ328/MC68VZ328/MC68SZ328 DragonBall

Motorola DragonBall MX1 MC9328MX1

Intel StrongARM/ XScale

Hitachi SH-3

Hitachi SH-4

• 8-bit processor support with “glue logic”.

• “Fixed” and low-latency CPU access times.

• Registers are memory-mapped with dedicated M/R# input to select between memory and register address space.

• The contiguous 80K byte display buffer is directly accessible through the 17-bit address bus.

LCD Panel Support

• 4/8-bit monochrome STN interface.

• 4/8-bit color STN interface.

• 9/12/18-bit Active Matrix TFT interface.

• Direct support for 18-bit Sharp HR-TFT interface (160x160, 320x240).

Display Modes

• 1/2/4/8/16 bit-per-pixel (bpp) color depths.

• Up to 64 gray shades using Frame Rate Control (FRC) and dithering on monochrome passive LCD panels.

• Up to 256k colors on passive STN panels.

• Up to 256k colors on active matrix LCD panels.

• Resolution examples :

320x240 at a color depth of 8 bpp

160x160 at a color depth of 16 bpp

160x240 at a color depth of 16 bpp

Display Features

• Display Rotate Mode : 90°, 180°, 270° counter-clockwise hardware rotation of display image.

• Virtual display support : displays image larger than the panel size through the use of panning and scrolling.

• Floating Window Mode : displays a variable size window overlaid on background image.

• 2 Hardware Cursors (for 4/8/16 bpp) : simultaneously displays two cursors overlaid on background image.

• Double Buffering/Multi-pages: provides smooth animation and instantaneous screen updates.

Clock Source

• Two clock inputs: CLKI and AUXCLK. It is possible to use one clock input only.

• Bus clock (BCLK) is derived from CLKI, can be internally divided by 2, 3, or 4.

• Memory clock (MCLK) is derived from BCLK. It can be internally divided by 2, 3, or 4.

• Pixel clock (PCLK) can be derived from CLKI, AUXCLK, BCLK, or MCLK. It can be internally divided by 2, 3, 4, or 8.

Miscellaneous

• Hardware/Software Color Invert

• Software Power Saving mode

• General Purpose Input / Output pins available

• Single Supply Operation : 3.0V – 3.6V

Package

• 100-pin TQFP package