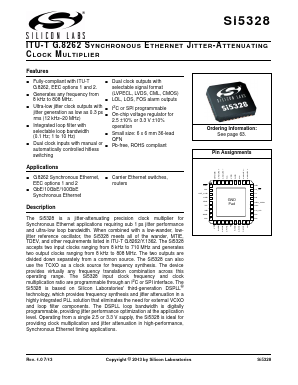

Silicon Laboratories

SI5328B-C-GM 데이터시트 - Silicon Laboratories

Description

The Si5328 is a jitter-attenuating precision clock multiplier for Synchronous Ethernet applications requiring sub 1 ps jitter performance and ultra-low loop bandwidth. Whencombined with a low-wander, low jitter reference oscillator, the Si5328 meets all of the wander, MTIE, TDEV, and other requirements listed in ITU-T G.8262/Y.1362. The Si5328 accepts two input clocks ranging from 8 kHz to 710 MHz and generates two output clocks ranging from 8 kHz to 808 MHz. The two outputs are divided down separately from a common source.

FEATUREs

Fully-compliant with ITU-T G.8262, EEC options 1 and 2.

Generates any frequency from 8kHz to 808MHz.

Ultra-low jitter clock outputs with jitter generation as low as 0.3 ps rms (12 kHz–20 MHz)

Integrated loopfilter with selectable loop bandwidth (0.1 Hz; 1 to 10 Hz)

Dual clock inputs with manual or automatically controlled hitless switching

Dual clock outputs with selectable signal format(LVPECL, LVDS, CML, CMOS)

LOL, LOS, FOS alarm outputs

I2C or SPI programmable

On-chip voltage regulator for 2.5 ±10% or 3.3 V ±10% operation

Small size: 6 x 6 mm 36-lead QFN

Pb-free, ROHS compliant

APPLICATIONs

G.8262 Synchronous Ethernet, EEC options 1 and 2

GbE/10GbE/100GbE Synchronous Ethernet

Carrier Ethernet switches, routers