PhaseLink Corporation

PLL103-03 데이터시트 - PhaseLink Corporation

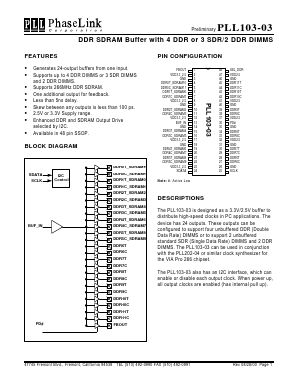

DESCRIPTIONS

The PLL103-03 is designed as a 3.3V/2.5V buffer to distribute high-speed clocks in PC applications. The device has 24 outputs. These outputs can be configured to support four unbuffered DDR (Double Data Rate) DIMMS or to support 2 unbuffered standard SDR (Single Data Rate) DIMMS and 2 DDR DIMMS. The PLL103-03 can be used in conjunction with the PLL202-04 or similar clock synthesizer for the VIA Pro 266 chipset.

FEATURES

• Generates 24-output buffers from one input.

• Supports up to 4 DDR DIMMS or 3 SDR DIMMS and 2 DDR DIMMS.

• Supports 266MHz DDR SDRAM.

• One additional output for feedback.

• Less than 5ns delay.

• Skew between any outputs is less than 100 ps.

• 2.5V or 3.3V Supply range.

• Enhanced DDR and SDRAM Output Drive selected by I2C.

• Available in 48 pin SSOP.