Motorola => Freescale

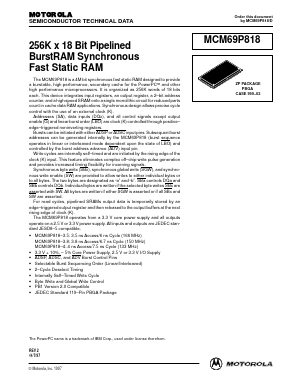

MCM69P818ZP3.5 데이터시트 - Motorola => Freescale

The MCM69P818 is a 4M bit synchronous fast static RAM designed to provide a burstable, high performance, secondary cache for the PowerPC™ and other high performance microprocessors. It is organized as 256K words of 18 bits each. This device integrates input registers, an output register, a 2–bit address counter, and a high speed SRAM onto a single monolithic circuit for reduced parts count in cache data RAM applications. Synchronous design allows precise cycle control with the use of an external clock (K).

• MCM69P818–3.5: 3.5 ns Access/6 ns Cycle (166 MHz)

MCM69P818–3.8: 3.8 ns Access/6.7 ns Cycle (150 MHz)

MCM69P818–4: 4 ns Access/7.5 ns Cycle (133 MHz)

• 3.3 V + 10%, – 5% Core Power Supply, 2.5 V or 3.3 V I/O Supply

• ADSP, ADSC, and ADV Burst Control Pins

• Selectable Burst Sequencing Order (Linear/Interleaved)

• 2–Cycle Deselect Timing

• Internally Self–Timed Write Cycle

• Byte Write and Global Write Control

• PB1 Version 2.0 Compatible

• JEDEC Standard 119–Pin PBGA Package