Motorola => Freescale

MC14531BCL 데이터시트 - Motorola => Freescale

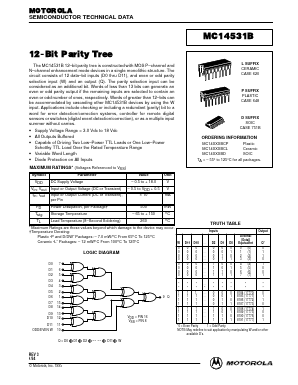

The MC14531B 12–bit parity tree is constructed with MOS P–channel and N–channel enhancement mode devices in a single monolithic structure. The circuit consists of 12 data–bit inputs (D0 thru D11), and even or odd parity selection input (W) and an output (Q). The parity selection input can be considered as an additional bit. Words of less than 13 bits can generate an even or odd parity output if the remaining inputs are selected to contain an even or odd number of ones, respectively. Words of greater than 12–bits can be accommodated by cascading other MC14531B devices by using the W input. Applications include checking or including a redundant (parity) bit to a word for error detection/correction systems, controller for remote digital sensors or switches (digital event detection/correction), or as a multiple input summer without carries.

• Supply Voltage Range = 3.0 Vdc to 18 Vdc

• All Outputs Buffered

• Capable of Driving Two Low–Power TTL Loads or One Low–Power Schottky TTL Load Over the Rated Temperature Range

• Variable Word Length

• Diode Protection on All Inputs