STMicroelectronics

M54HC112 데이터시트 - STMicroelectronics

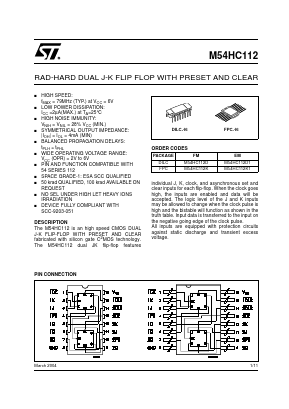

DESCRIPTION

The M54HC112 is an high speed CMOS DUAL J-K FLIP-FLOP WITH PRESET AND CLEAR fabricated with silicon gate C2MOS technology.

The M54HC112 dual JK flip-flop features individual J, K, clock, and asynchronous set and clear inputs for each flip-flop. When the clock goes high, the inputs are enabled and data will be accepted. The logic level of the J and K inputs may be allowed to change when the clock pulse is high and the bistable will function as shown in the truth table. Input data is transferred to the input on the negative going edge of the clock pulse.

■ HIGH SPEED: fMAX = 79MHz (TYP.) at VCC = 6V

■ LOW POWER DISSIPATION: ICC =2µA(MAX.) at TA=25°C

■ HIGH NOISE IMMUNITY: VNIH = VNIL = 28% VCC (MIN.)

■ SYMMETRICAL OUTPUT IMPEDANCE: |IOH| = IOL = 4mA (MIN)

■ BALANCED PROPAGATION DELAYS: tPLH ≅ tPHL

■ WIDE OPERATING VOLTAGE RANGE: VCC (OPR) = 2V to 6V

■ PIN AND FUNCTION COMPATIBLE WITH 54 SERIES 112

■ SPACE GRADE-1: ESA SCC QUALIFIED

■ 50 krad QUALIFIED, 100 krad AVAILABLE ON REQUEST

■ NO SEL UNDER HIGH LET HEAVY IONS IRRADIATION

■ DEVICE FULLY COMPLIANT WITH SCC-9203-051