LOGIC Devices

L10C11 데이터시트 - LOGIC Devices

DESCRIPTION

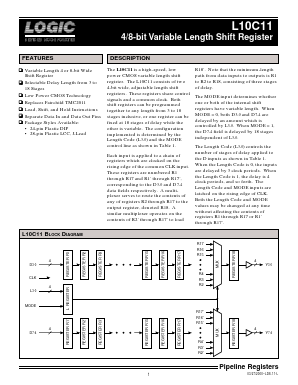

The L10C11 is a high-speed, low power CMOS variable length shift register. The L10C11 consists of two 4-bit wide, adjustable length shift registers. These registers share control signals and a common clock. Both shift registers can be programmed together to any length from 3 to 18 stages inclusive, or one register can be fixed at 18 stages of delay while the other is variable. The configuration implemented is determined by the Length Code (L3-0) and the MODE control line as shown in Table 1.

FEATURES

❑ Variable Length 4 or 8-bit Wide Shift Register

❑ Selectable Delay Length from 3 to 18 Stages

❑ Low Power CMOS Technology

❑ Replaces Fairchild TMC2011

❑ Load, Shift, and Hold Instructions

❑ Separate Data In and Data Out Pins

❑ Package Styles Available:

• 24-pin Plastic DIP

• 28-pin Plastic LCC, J-Lead