Integrated Silicon Solution

IS61LPD51218A-250B3(2005) 데이터시트 - Integrated Silicon Solution

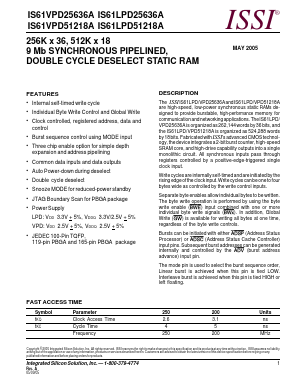

DESCRIPTION

The ISSIIS61LPD/VPD25636A and IS61LPD/VPD51218A are high-speed, low-power synchronous static RAMs designed to provide burstable, high-performance memory for communication and networking applications. The IS61LPD/ VPD25636A is organized as 262,144 words by 36 bits, and the IS61LPD/VPD51218A is organized as 524,288 words by 18 bits. Fabricated withISSIs advanced CMOS technology, the device integrates a 2-bit burst counter, high-speed SRAM core, and high-drive capability outputs into a single monolithic circuit. All synchronous inputs pass through registers controlled by a positive-edge-triggered single clock input.

FEATURES

• Internal self-timed write cycle

• Individual Byte Write Control and Global Write

• Clock controlled, registered address, data and control

• Burst sequence control using MODE input

• Three chip enable option for simple depth expansion and address pipelining

• Common data inputs and data outputs

• Auto Power-down during deselect

• Double cycle deselect

• Snooze MODE for reduced-power standby

• JTAG Boundary Scan for PBGA package

• Power Supply

LPD: VDD 3.3V + 5%, VDDQ 3.3V/2.5V + 5%

VPD: VDD 2.5V + 5%, VDDQ 2.5V + 5%

• JEDEC 100-Pin TQFP, 119-pin PBGA and 165-pin PBGA package