Integral Corp.

IN74LV74N 데이터시트 - Integral Corp.

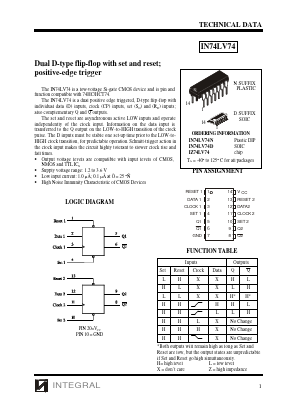

Dual D-type flip-flop with set and reset; positive-edge trigger

The IN74LV74 is a low-voltage Si-gate CMOS device and is pin and function compatible with 74HC/HCT74.

The IN74LV74 is a dual positive edge triggered, D-type flip-flop with individual data (D) inputs, clock (CP) inputs, set (SD) and (RD) inputs; also complementary Q and Q outputs.

The set and reset are asynchronous active LOW inputs and operate independently of the clock input. Information on the data input is transferred to the Q output on the LOW-to-HIGH transition of the clock pulse. The D inputs must be stable one set-up time prior to the LOW-toH-IGH clock transition, for predictable operation. Schmitt-trigger action in the clock input makes the circuit highly tolerant to slower clock rise and fall times.

• Output voltage levels are compatible with input levels of CMOS,

NMOS and TTL ICS

• Supply voltage range: 1.2 to 3.6 V

• Low input current: 1.0 mÀ; 0.1 mÀ at Ò = 25 °Ñ

• High Noise Immunity Characteristic of CMOS Devices