Integrated Circuit Systems

ICS8547 데이터시트 - Integrated Circuit Systems

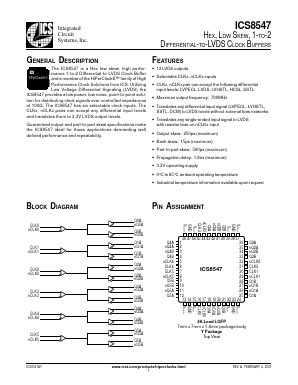

GENERAL DESCRIPTION

The ICS8547 is a Hex low skew, high performance 1-to-2 Differential-to-LVDS Clock Buffer and a member of the HiPerClockS™ family of High Performance Clock Solutions from ICS. Utilizing Low Voltage Differential Signaling (LVDS) the ICS8547 provides a low power, low noise, point-to-point solution for distributing clock signals over controlled impedances of 100Ω. The ICS8547 has six selectable clock inputs. The CLKx, nCLKx pairs can accept any differential input levels and translates them to 3.3V LVDS output levels.

FEATURES

• 12 LVDS outputs

• Selectable CLKx, nCLKx inputs

• CLKx, nCLKx pair can accept the following differential input levels: LVPECL, LVDS, LVHSTL, HCSL, SSTL

• Maximum output frequency: 700MHz

• Translates any differential input signal (LVPECL, LVHSTL, SSTL, DCM) to LVDS levels without external bias networks

• Translates any single-ended input signal to LVDS with resistor bias on nCLKx input

• Output skew: 250ps (maximum)

• Bank skew: 15ps (maximum)

• Part-to-part skew: 500ps (maximum)

• Propagation delay: 1.8ns (maximum)

• 3.3V operating supply

• 0°C to 85°C ambient operating temperature

• Industrial temperature information available upon request