Integrated Circuit Systems

ICS670-02 데이터시트 - Integrated Circuit Systems

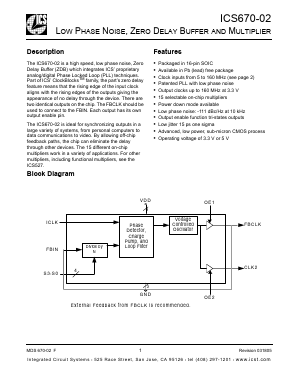

Description

The ICS670-02 is a high speed, low phase noise, Zero Delay Buffer (ZDB) which integrates ICS’ proprietary analog/digital Phase Locked Loop (PLL) techniques. Part of ICS’ ClockBlocksTM family, the part’s zero delay feature means that the rising edge of the input clock aligns with the rising edges of the outputs giving the appearance of no delay through the device. There are two identical outputs on the chip. The FBCLK should be used to connect to the FBIN. Each output has its own output enable pin.

FEATUREs

• Packaged in 16-pin SOIC

• Available in Pb (lead) free package

• Clock inputs from 5 to 160 MHz (see page 2)

• Patented PLL with low phase noise

• Output clocks up to 160 MHz at 3.3 V

• 15 selectable on-chip multipliers

• Power down mode available

• Low phase noise: -111 dBc/Hz at 10 kHz

• Output enable function tri-states outputs

• Low jitter 15 ps one sigma

• Advanced, low power, sub-micron CMOS process

• Operating voltage of 3.3 V or 5 V