Cypress Semiconductor

CY7C4255V(2001) 데이터시트 - Cypress Semiconductor

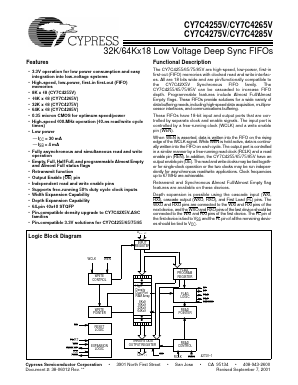

Functional Description

The CY7C4255/65/75/85V are high-speed, low-power, first-in first-out (FIFO) memories with clocked read and write interfaces. All are 18 bits wide and are pin/functionally compatible to the CY7C42X5V Synchronous FIFO family. The CY7C4255/65/75/85V can be cascaded to increase FIFO depth. Programmable features include Almost Full/Almost Empty flags. These FIFOs provide solutions for a wide variety of data buffering needs, including high-speed data acquisition, multiprocessor interfaces, and communications buffering.

FEATUREs

• 3.3V operation for low power consumption and easy integration into low-voltage systems

• High-speed, low-power, first-in first-out (FIFO) memories

• 8K x 18 (CY7C4255V)

• 16K x 18 (CY7C4265V)

• 32K x 18 (CY7C4275V)

• 64K x 18 (CY7C4285V)

• 0.35 micron CMOS for optimum speed/power

• High-speed 100-MHz operation (10-ns read/write cycle times)

• Low power

— ICC = 30 mA

— ISB = 4 mA

• Fully asynchronous and simultaneous read and write operation

• Empty, Full, Half Full, and programmable Almost Empty and Almost Full status flags

• Retransmit function

• Output Enable (OE) pin

• Independent read and write enable pins

• Supports free-running 50% duty cycle clock inputs

• Width Expansion Capability

• Depth Expansion Capability

• 64-pin 10x10 STQFP

• Pin-compatible density upgrade to CY7C42X5V-ASC families

• Pin-compatible 3.3V solutions for CY7C4255/65/75/85