Cypress Semiconductor

CY23S08SI-1H 데이터시트 - Cypress Semiconductor

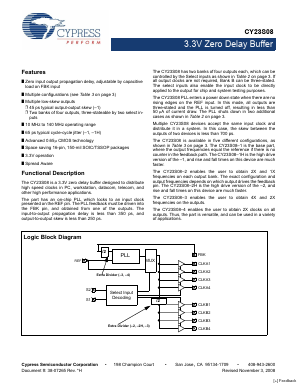

Functional Description

The CY23S08 is a 3.3V zero delay buffer designed to distribute high speed clocks in PC, workstation, datacom, telecom, and other high performance applications.

The part has an on-chip PLL which locks to an input clock presented on the REF pin. The PLL feedback must be driven into the FBK pin, and obtained from one of the outputs. The input-to-output propagation delay is less than 350 ps, and output-to-output skew is less than 250 ps.

FEATUREs

■ Zero input output propagation delay, adjustable by capacitive load on FBK input

■ Multiple configurations (see Table 3 on page 3)

■ Multiple low-skew outputs

❐ 45 ps typical output-output skew (–1)

❐ Two banks of four outputs, three-stateable by two select inputs

■ 10 MHz to 140 MHz operating range

■ 65 ps typical cycle-cycle jitter (–1, –1H)

■ Advanced 0.65μ CMOS technology

■ Space saving 16-pin, 150-mil SOIC/TSSOP packages

■ 3.3V operation

■ Spread Aware