Analog Devices

ADSP-2171 데이터시트 - Analog Devices

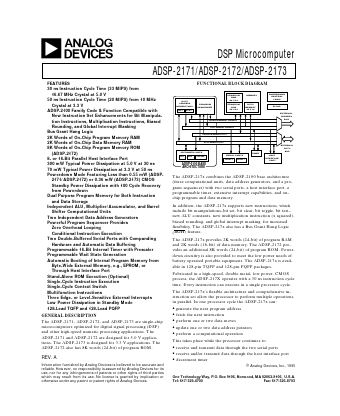

GENERAL DESCRIPTION

The ADSP-2171, ADSP-2172, and ADSP-2173 are single-chip microcomputers optimized for digital signal processing (DSP) and other high-speed numeric processing applications. The ADSP-2171 and ADSP-2172 are designed for 5.0 V applications. The ADSP-2173 is designed for 3.3 V applications. The ADSP-2172 also has 8K words (24-bit) of program ROM.

FEATURES

30 ns Instruction Cycle Time (33 MIPS) from 16.67 MHz Crystal at 5.0 V

50 ns Instruction Cycle Time (20 MIPS) from 10 MHz Crystal at 3.3 V

ADSP-2100 Family Code & Function Compatible with New Instruction Set Enhancements for Bit Manipulation Instructions, Multiplication Instructions, Biased Rounding, and Global Interrupt Masking

Bus Grant Hang Logic

2K Words of On-Chip Program Memory RAM

2K Words of On-Chip Data Memory RAM

8K Words of On-Chip Program Memory ROM (ADSP-2172)

8- or 16-Bit Parallel Host Interface Port

300 mW Typical Power Dissipation at 5.0 V at 30 ns

70 mW Typical Power Dissipation at 3.3 V at 50 ns

Powerdown Mode Featuring Less than 0.55 mW (ADSP- 2171/ADSP-2172) or 0.36 mW (ADSP-2173) CMOS Standby Power Dissipation with 100 Cycle Recovery from Powerdown

Dual Purpose Program Memory for Both Instruction and Data Storage

Independent ALU, Multiplier/Accumulator, and Barrel Shifter Computational Units

Two Independent Data Address Generators

Powerful Program Sequencer Provides Zero Overhead Looping Conditional Instruction Execution

Two Double-Buffered Serial Ports with Companding Hardware and Automatic Data Buffering

Programmable 16-Bit Interval Timer with Prescaler

Programmable Wait State Generation

Automatic Booting of Internal Program Memory from Byte-Wide External Memory, e.g., EPROM, or Through Host Interface Port

Stand-Alone ROM Execution (Optional)

Single-Cycle Instruction Execution

Single-Cycle Context Switch

Multifunction Instructions

Three Edge- or Level-Sensitive External Interrupts

Low Power Dissipation in Standby Mode

128-Lead TQFP and 128-Lead PQFP