Analog Devices

ADSP-21261(Rev0) 데이터시트 - Analog Devices

GENERAL DESCRIPTION

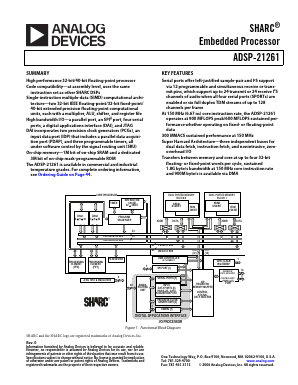

The ADSP-21261 SHARC DSP is a member of the SIMD SHARC family of DSPs featuring Analog Devices Super Harvard Architecture. The ADSP-21261 is source code compatible with the ADSP-2126x, ADSP-21160, and ADSP-21161 DSPs, as well as with first generation ADSP-2106x SHARC processors in SISD (single-instruction, single-data) mode. Like other SHARC DSPs, the ADSP-21261 is a 32-bit/40-bit floating-point processor optimized for high performance signal processing applications with its dual-ported on-chip SRAM, mask-programmable ROM, multiple internal buses to eliminate I/O bottlenecks, and an innovative digital applications interface.

SUMMARY

High performance 32-bit/40-bit floating-point processor

Code compatibility—at assembly level, uses the same

instruction set as other SHARC DSPs

Single-instruction multiple-data (SIMD) computational

architecture—two 32-bit IEEE floating-point/32-bit fixed-point/

40-bit extended precision floating-point computational

units, each with a multiplier, ALU, shifter, and register file

High bandwidth I/O—a parallel port, an SPI® port, four serial

ports, a digital applications interface (DAI), and JTAG

DAI incorporates two precision clock generators (PCGs), an

input data port (IDP) that includes a parallel data

acquisition port (PDAP), and three programmable timers, all

under software control by the signal routing unit (SRU)

On-chip memory—1M bit of on-chip SRAM and a dedicated

3M bit of on-chip mask-programmable ROM

The ADSP-21261 is available in commercial and industrial

temperature grades. For complete ordering information,

see Ordering Guide on Page 44.