Analog Devices

ADSP-21161NCCA-100(RevA) 데이터시트 - Analog Devices

GENERAL DESCRIPTION

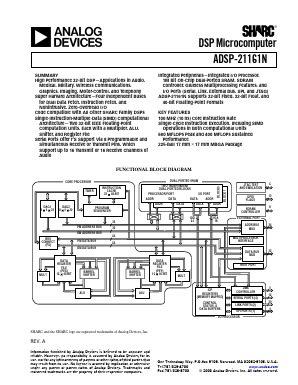

The ADSP-21161N SHARC DSP is the first low cost derivative of the ADSP-21160 featuring Analog Devices Super Harvard Architecture. Easing portability, the ADSP-21161N is source code compatible with the ADSP-21160 and with first generation ADSP-2106x SHARCs in SISD (Single Instruction, Single Data) mode. Like other SHARC DSPs, the ADSP-21161N is a 32-bit processor that is optimized for high performance DSP applications. The ADSP-21161N includes a 100 MHz core, a dual-ported on-chip SRAM, an integrated I/O processor with multiprocessing support,and multiple internal buses to eliminate I/O bottlenecks.

SUMMARY

High Performance 32-Bit DSP—Applications in Audio,

Medical, Military, Wireless Communications,

Graphics, Imaging, Motor-Control, and Telephony

Super Harvard Architecture—Four Independent Buses

for Dual Data Fetch, Instruction Fetch, and

Nonintrusive, Zero-Overhead I/O

Code Compatible with All Other SHARC Family DSPs

Single-Instruction-Multiple-Data (SIMD) Computational

Architecture—Two 32-Bit IEEE Floating-Point

Computation Units, Each with a Multiplier, ALU,

Shifter, and Register File

Serial Ports Offer I2S Support Via 8 Programmable and

Simultaneous Receive or Transmit Pins, which

Support up to 16 Transmit or 16 Receive Channels of

Audio

Integrated Peripherals—Integrated I/O Processor,

1M Bit On-Chip Dual-Ported SRAM, SDRAM

Controller, Glueless Multiprocessing Features, and

I/O Ports (Serial, Link, External Bus, SPI, and JTAG)

ADSP-21161N Supports 32-Bit Fixed, 32-Bit Float, and

40-Bit Floating-Point Formats