Analog Devices

ADSP-21160M(Rev0) 데이터시트 - Analog Devices

GENERAL DESCRIPTION

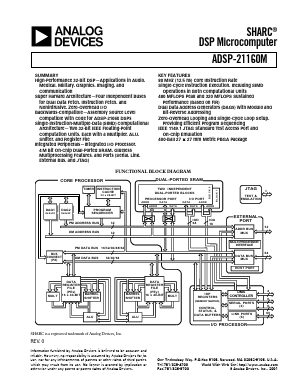

The ADSP-21160M SHARC DSP is the first processor in a new family featuring Analog Devices’ Super Harvard Architecture. Easing portability, the ADSP-21160M is application source code compatible with first generation ADSP-2106x SHARC DSPs in SISD (Single Instruction, Single Data) mode. To take advantage of the processor’s SIMD (Single Instruction, Multiple Data) capability, some code changes are needed. Like other SHARCs, the ADSP-21160M is a 32-bit processor that is optimized for high performance DSP applications. The ADSP-21160M includes an 80 MHz core, a dual-ported on-chip SRAM, an integrated I/O processor with multiprocessing support, and multiple internal buses to eliminate I/O bottlenecks.

SUMMARY

High-Performance 32-Bit DSP—Applications in Audio,

Medical, Military, Graphics, Imaging, and

Communication

Super Harvard Architecture—Four Independent Buses

for Dual Data Fetch, Instruction Fetch, and

Nonintrusive, Zero-Overhead I/O

Backwards-Compatible—Assembly Source Level

Compatible with Code for ADSP-2106x DSPs

Single-Instruction-Multiple-Data (SIMD) Computational

Architecture—Two 32-Bit IEEE Floating-Point

Computation Units, Each with a Multiplier, ALU,

Shifter, and Register File

Integrated Peripherals—Integrated I/O Processor,

4 M Bit On-Chip Dual-Ported SRAM, Glueless

Multiprocessing Features, and Ports (Serial, Link,

External Bus, and JTAG)