Analog Devices

ADSP-21065L 데이터시트 - Analog Devices

GENERAL DESCRIPTION

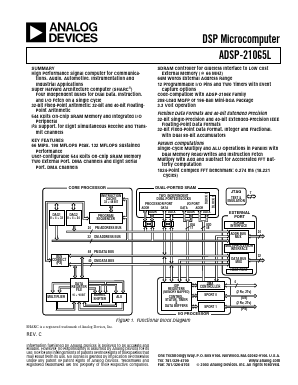

The ADSP-21065L is a powerful member of the SHARC family of 32-bit processors optimized for cost sensitive applications. The SHARC—Super Harvard Architecture—offers the highest levels of performance and memory integration of any 32-bit DSP in the industry—they are also the only DSP in the industry that offer both fixed and floating-point capabilities, without compromising precision or performance.

SUMMARY

High Performance Signal Computer for Communications,

Audio, Automotive, Instrumentation and

Industrial Applications

Super Harvard Architecture Computer (SHARC®)

Four Independent Buses for Dual Data, Instruction,

and I/O Fetch on a Single Cycle

32-Bit Fixed-Point Arithmetic; 32-Bit and 40-Bit

Floating-Point Arithmetic

544 Kbits On-Chip SRAM Memory and Integrated I/O

Peripheral

I2S Support, for Eight Simultaneous Receive and Transmit Channels

KEY FEATURES

66 MIPS, 198 MFLOPS Peak, 132 MFLOPS Sustained

Performance

User-Configurable 544 Kbits On-Chip SRAM Memory

Two External Port, DMA Channels and Eight Serial

Port, DMA Channels

SDRAM Controller for Glueless Interface to Low Cost

External Memory (@ 66 MHz)

64M Words External Address Range

12 Programmable I/O Pins and Two Timers with Event

Capture Options

Code-Compatible with ADSP-2106x Family

208-Lead MQFP or 196-Ball Mini-BGA Package

3.3 Volt Operation (Continue ...)