Intel

82093AA 데이터시트 - Intel

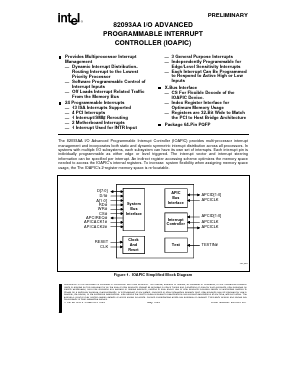

The 82093AA I/O Advanced Programmable Interrupt Controller (IOAPIC) provides multi-processor interrupt management and incorporates both static and dynamic symmetric interrupt distribution across all processors. In systems with multiple I/O subsystems, each subsystem can have its own set of interrupts. Each interrupt pin is individually programmable as either edge or level triggered. The interrupt vector and interrupt steering information can be specified per interrupt. An indirect register accessing scheme optimizes the memory space needed to access the IOAPIC’s internal registers. To increase system flexibility when assigning memory space usage, the The IOAPIC’s 2-register memory space is re-locatable.

■ Provides Multiprocessor Interrupt Management

- Dynamic Interrupt DistributionRouting Interrupt to the Lowest Priority Processor

- Software Programmable Control of Interrupt Inputs

- Off Loads Interrupt Related Traffic From the Memory Bus

■ 24 Programmable Interrupts

- 13 ISA Interrupts Supported

- 4 PCI Interrupts

- 1 Interrupt/SMI# Rerouting

- 2 Motherboard Interrupts

- 1 Interrupt Used for INTR Input

- 3 General Purpose Interrupts

- Independently Programmable for Edge/Level Sensitivity Interrupts

- Each Interrupt Can Be Programmed to Respond to Active High or Low Inputs

■ X-Bus Interface

- CS For Flexible Decode of the IOAPIC Device.

- Index Register Interface for Optimum Memory Usage

- Registers are 32-Bit Wide to Match the PCI to Host Bridge Architecture

■ Package 64-Pin PQFP