AD7175-8 데이터 시트보기 (PDF) - Analog Devices

부품명

상세내역

제조사

AD7175-8

Analog Devices

AD7175-8 Datasheet PDF : 64 Pages

| |||

Data Sheet

AD7175-8

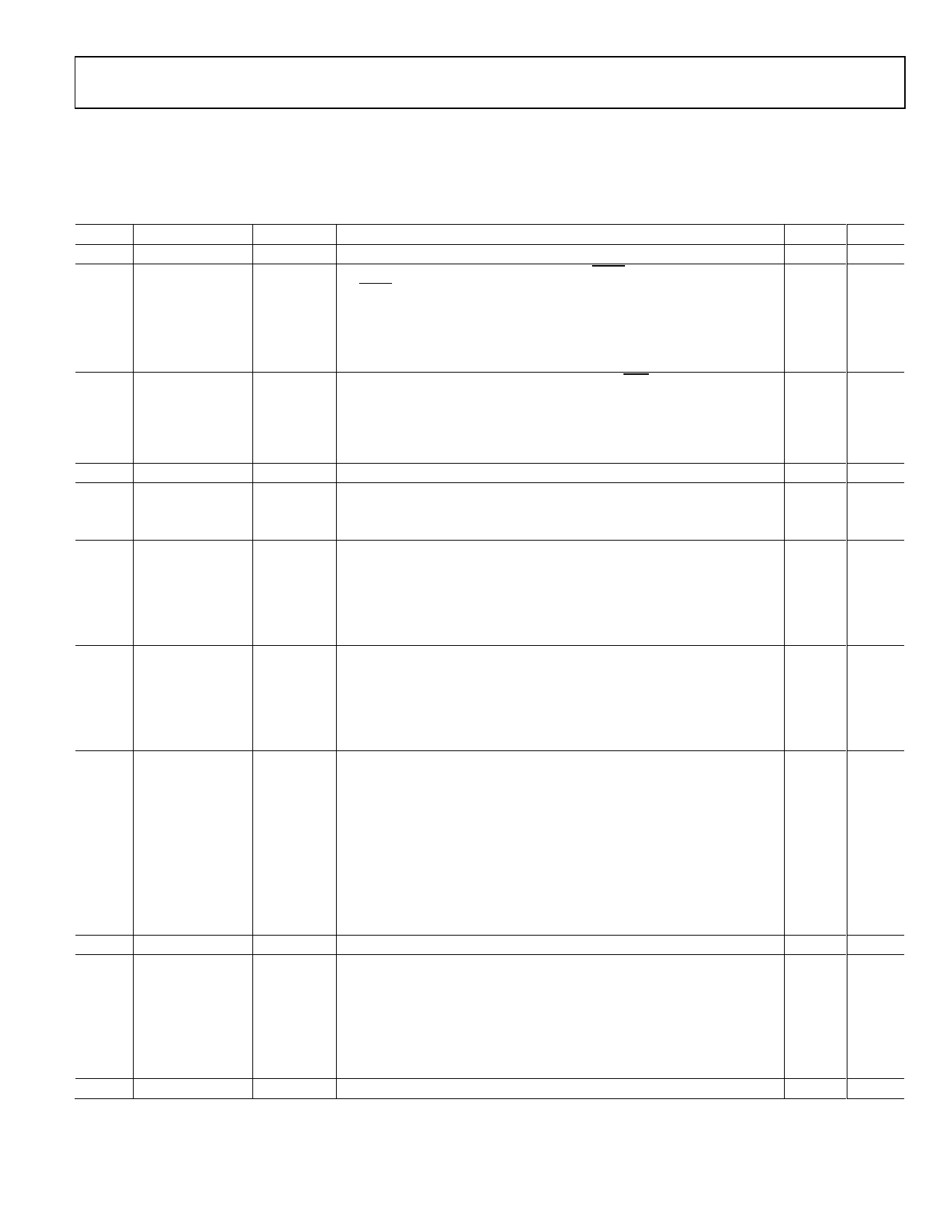

INTERFACE MODE REGISTER

Address: 0x02, Reset: 0x0000, Name: IFMODE

The interface mode register configures various serial interface options.

Table 28. Bit Descriptions for IFMODE

Bits Bit Name

Settings

[15:13] RESERVED

12

ALT_SYNC

0

1

11

IOSTRENGTH

0

1

[10:9] RESERVED

8

DOUT_RESET

0

1

7

CONTREAD

0

1

6

DATA_STAT

0

1

5

REG_CHECK

0

1

4

RESERVED

[3:2] CRC_EN

00

01

10

1

RESERVED

Description

These bits are reserved; set these bits to 0.

This bit enables a different behavior of the SYNC pin to allow the use

of SYNC as a control for conversions when cycling channels (see the

description of the SYNC_EN bit in the GPIO Configuration Register section

for details).

Disabled

Enabled

This bit controls the drive strength of the DOUT/RDY pin. Set this bit when

reading from the serial interface at high speed with a low IOVDD supply

and moderate capacitance.

Disabled (default)

Enabled

These bits are reserved; set these bits to 0.

See the DOUT_RESET section for more information.

Disabled

Enabled

This bit enables the continuous read mode of the ADC data register. The

ADC must be configured in continuous conversion mode to use

continuous read mode. For more details, see the Operating Modes

section.

Disabled

Enabled

This bit enables the status register to be appended to the data register

when read so that channel and status information are transmitted with

the data. This is the only way to be sure that the channel bits read from

the status register correspond to the data in the data register.

Disabled

Enabled

This bit enables a register integrity checker, which can be used to monitor

any change in the value of the user registers. To use this feature, configure

all other registers as desired with this bit cleared. Then write to this register to

set the REG_CHECK bit to 1. If the contents of any of the registers change,

the REG_ERROR bit is set in the status register. To clear the error, set the

REG_CHECK bit to 0. Neither the interface mode register nor the ADC data

or status registers are included in the registers that are checked. If a

register must have a new value written, this bit must first be cleared;

otherwise, an error is flagged when the new register contents are written.

Disabled

Enabled

This bit is reserved; set this bit to 0.

These bits enable CRC protection of register reads/writes. CRC increases

the number of bytes in a serial interface transfer by one. See the CRC

Calculation section for more details.

Disabled

XOR checksum enabled for register read transactions; register writes still

use CRC with these bits set

CRC checksum enabled for read and write transactions

This bit is reserved; set this bit to 0.

Reset

0x0

0x0

0x0

0x0

0x0

0x0

0x0

0x0

0x0

0x00

0x0

Access

R

RW

RW

R

RW

RW

RW

RW

R

RW

R

Rev. 0 | Page 53 of 64