74HC126PW 데이터 시트보기 (PDF) - NXP Semiconductors.

부품명

상세내역

제조사

74HC126PW Datasheet PDF : 15 Pages

| |||

Nexperia

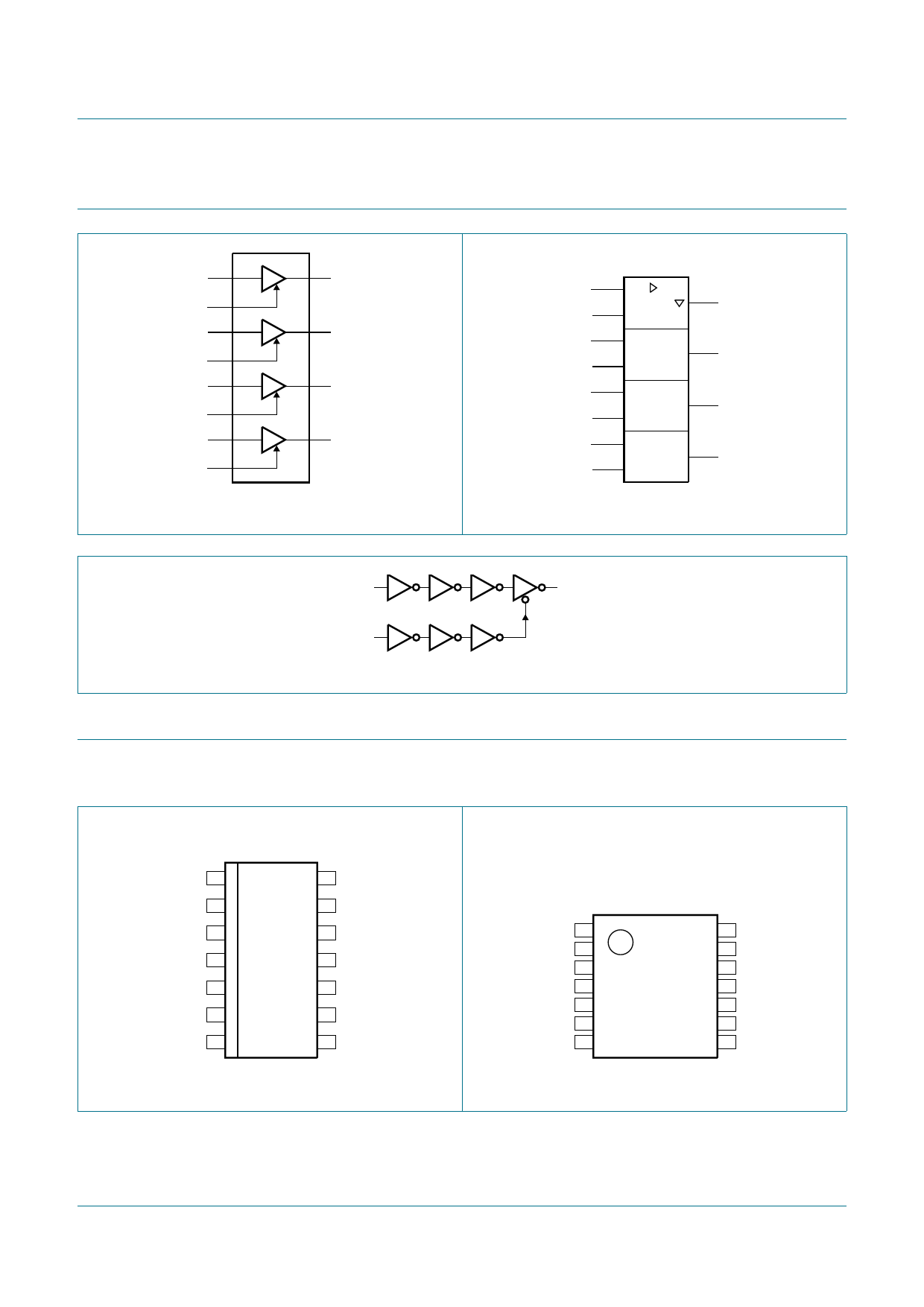

4. Functional diagram

$

<

2(

$

2(

$

<

<

2(

$

2(

<

PQD

Fig 1. Logic symbol

Q$

Q2(

Fig 3. Logic diagram (one buffer/line driver)

5. Pinning information

5.1 Pinning

+&

+&7

2(

$

<

2(

$

<

*1'

9&&

2(

$

<

2(

$

<

DDD

Fig 4. Pin configuration for SOT108-1

74HC126; 74HCT126

Quad buffer/line driver; 3-state

(1

PQD

Fig 2. IEC logic symbol

Q<

PQD

+&

+&7

2(

$

<

2(

$

<

*1'

9&&

2(

$

<

2(

$

<

DDD

Fig 5. Pin configuration for SOT337-1 and SOT402-1

74HC_HCT126

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 4 — 1 December 2015

© Nexperia B.V. 2017. All rights reserved

2 of 15