W971GG8SB 데이터 시트보기 (PDF) - Winbond

부품명

상세내역

제조사

W971GG8SB Datasheet PDF : 87 Pages

| |||

W971GG8SB

1. GENERAL DESCRIPTION

The W971GG8SB is a 1G bits DDR2 SDRAM, organized as 16,777,216 words 8 banks 8 bits. This

device achieves high speed transfer rates up to 1066Mb/sec/pin (DDR2-1066) for various applications.

W971GG8SB is sorted into the following grade parts: -18, -25, 25I and -3. The -18 grade parts is

compliant to the DDR2-1066 (6-6-6) specification. The -25 and 25I grade parts are compliant to the

DDR2-800 (5-5-5) or DDR2-800 (6-6-6) specification (the 25I industrial grade which is guaranteed to

support -40°C ≤ TCASE ≤ 95°C). The -3 grade parts is compliant to the DDR2-667 (5-5-5) specification.

All of the control and address inputs are synchronized with a pair of externally supplied differential

clocks. Inputs are latched at the cross point of differential clocks (CLK rising and CLK falling). All

I/Os are synchronized with a single ended DQS or differential DQS- DQS pair in a source

synchronous fashion.

2. FEATURES

Power Supply: VDD, VDDQ = 1.8 V ± 0.1 V

Double Data Rate architecture: two data transfers per clock cycle

CAS Latency: 3, 4, 5, 6 and 7

Burst Length: 4 and 8

Bi-directional, differential data strobes (DQS and DQS ) are transmitted / received with data

Edge-aligned with Read data and center-aligned with Write data

DLL aligns DQ and DQS transitions with clock

Differential clock inputs (CLK and CLK )

Data masks (DM) for write data

Commands entered on each positive CLK edge, data and data mask are referenced to both edges

of DQS

Posted CAS programmable additive latency supported to make command and data bus efficiency

Read Latency = Additive Latency plus CAS Latency (RL = AL + CL)

Off-Chip-Driver impedance adjustment (OCD) and On-Die-Termination (ODT) for better signal

quality

Auto-precharge operation for read and write bursts

Auto Refresh and Self Refresh modes

Precharged Power Down and Active Power Down

Write Data Mask

Write Latency = Read Latency - 1 (WL = RL - 1)

Interface: SSTL_18

Packaged in WBGA 60 Ball (8x12.5 mm2), using Lead free materials with RoHS compliant

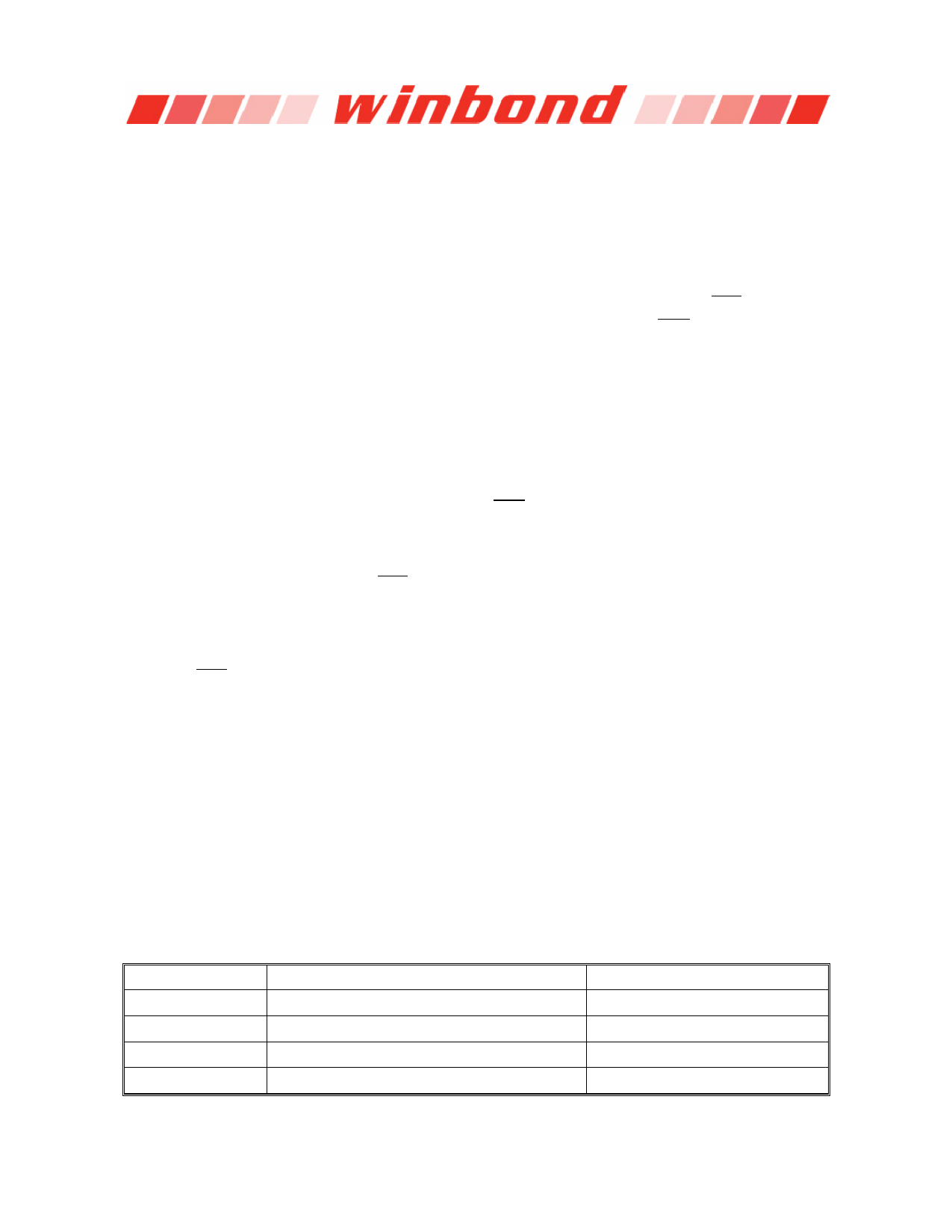

3. ORDER INFORMATION

PART NUMBER

W971GG8SB-18

SPEED GRADE

DDR2-1066 (6-6-6)

W971GG8SB-25 DDR2-800 (5-5-5) or DDR2-800 (6-6-6)

W971GG8SB25I DDR2-800 (5-5-5) or DDR2-800 (6-6-6)

W971GG8SB-3 DDR2-667 (5-5-5)

OPERATING TEMPERATURE

0°C ≤ TCASE ≤ 85°C

0°C ≤ TCASE ≤ 85°C

-40°C ≤ TCASE ≤ 95°C

0°C ≤ TCASE ≤ 85°C

Publication Release Date: Jan. 09, 2015

Revision: A01

-4-