ML6431 데이터 시트보기 (PDF) - Micro Linear Corporation

부품명

상세내역

제조사

ML6431

Micro Linear Corporation

ML6431 Datasheet PDF : 33 Pages

| |||

ML6430/ML6431

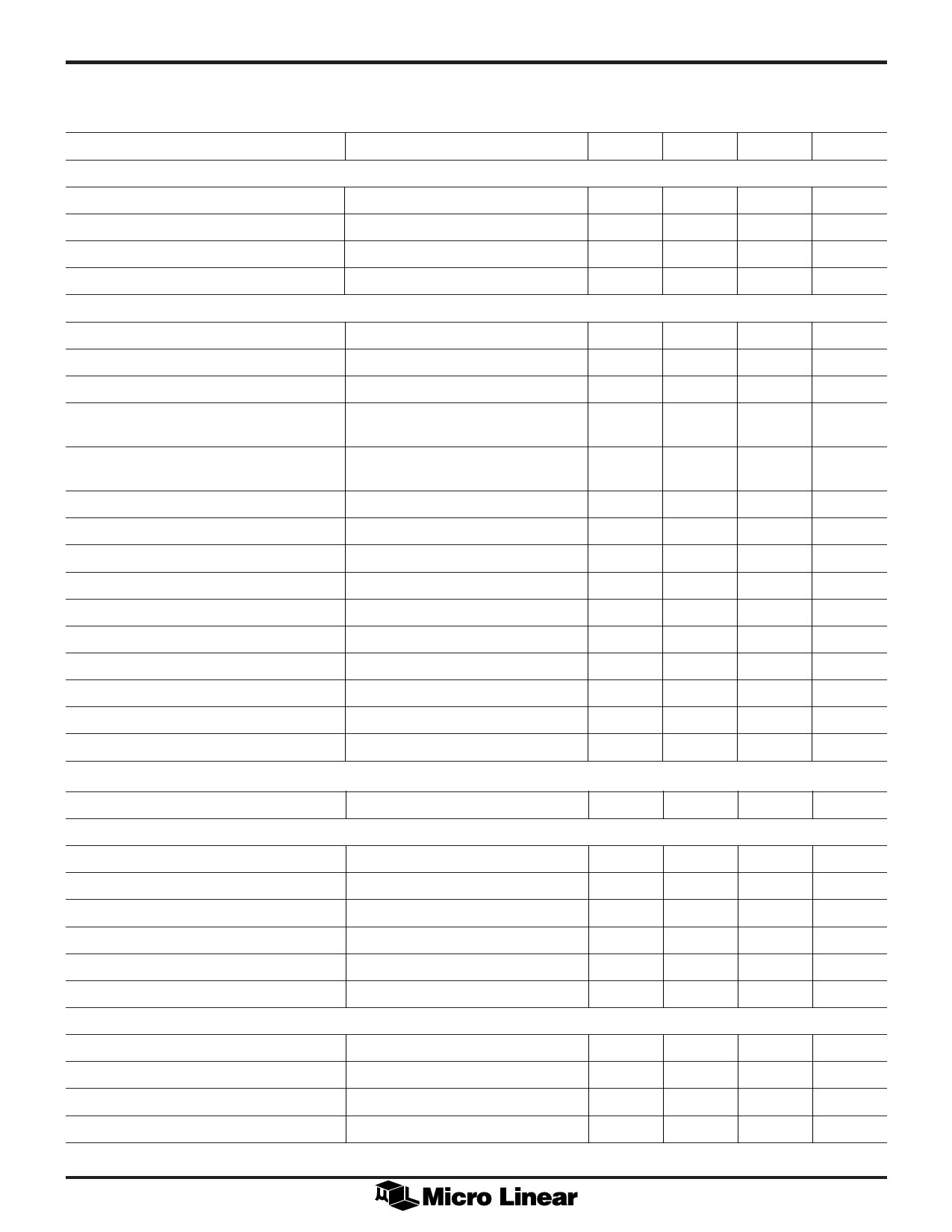

GENLOCK PERFORMANCE SPECIFICATIONS

Unless otherwise noted, VIN = 1 VPP NTSC test signal for composite inputs, or 100% color bars for component (Note 1).

See Figure 1 for parameter measurement definition

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

SYNC SEPARATION

Min Sync Amplitude

135

mV

Max Video Amplitude

3

V

Clamp timing error

NTC7 AC bounce signal (Note 2)

10

ns

Clamp Recovery TIme

NTC7 DC bounce signal (Note 3)

16

µs

CLOCK RECOVERY

Short Term Output Jitter Rejection

Input jitter = 50ns RMS

–15

dB

RMS Residual Output Clock Jitter

Input jitter <1ns RMS

600

ps

Peak to Peak (6s), Line to Line Jitter

Input Jitter < 1ns

2.0

2.2

ns

Head Switch Recovery Time to 1ns Error

5µs step H change on or before

line 1

4

lines

Step Frequency Recovery Time to 1ns Error

1% step H frequency change on or

before line 1

12

15

ms

Missing Sync Sensitivity

(Note 4)

1.0

ns

Sync Glitch Sensitivity

(Note 5)

1.0

ns

4X Clock Duty Cycle

2X Clock Duty Cycle

1X Clock Duty Cycle

Clock Skew — 1X to 2X

Pulse Output Rise Time

Pulse Output Fall Time

Pulse Output Setup Time

Pulse Output Hold Time

CLOAD = 50pF, fCLK4X < 60MHz

40

CLOAD = 50pF, fCLK2X < 30MHz

48

CLOAD = 50pF, fCLK1X < 15MHz

48

CLOAD = 50pF, fCLK1X < 15MHz

CLOAD = 50pF

2

CLOAD = 50pF

2

CLOAD = 50pF

20

CLOAD = 50pF

20

60

%

52

%

52

%

6

ns

10

ns

10

ns

ns

ns

SERIAL BUS

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

INPUT

Low Level Input Voltage

0

0.8

V

High Level Input Voltage

Low Level Input Current

High Level Input Current

Input Impedance fCLK = 100kHz

Input Capacitance (CIN)

SYSTEM TIMING

VIN = 0V

VIN = VCC D

VCC – 0.8

1

2

VCC

V

1.0

mA

1.0

mA

MW

pF

SCLK Frequency (fCLOCK)

Input Hysteresis (VHYS)

Spike Suppression (tSPIKE)

Power Setup Time to Valid Data Inputs

Max length for zero response

VCC Settled to Within 1%

100

kHz

0.2

V

50

ns

10

ms

6