HI-1567PSI 데이터 시트보기 (PDF) - Holt Integrated Circuits

부품명

상세내역

제조사

HI-1567PSI Datasheet PDF : 10 Pages

| |||

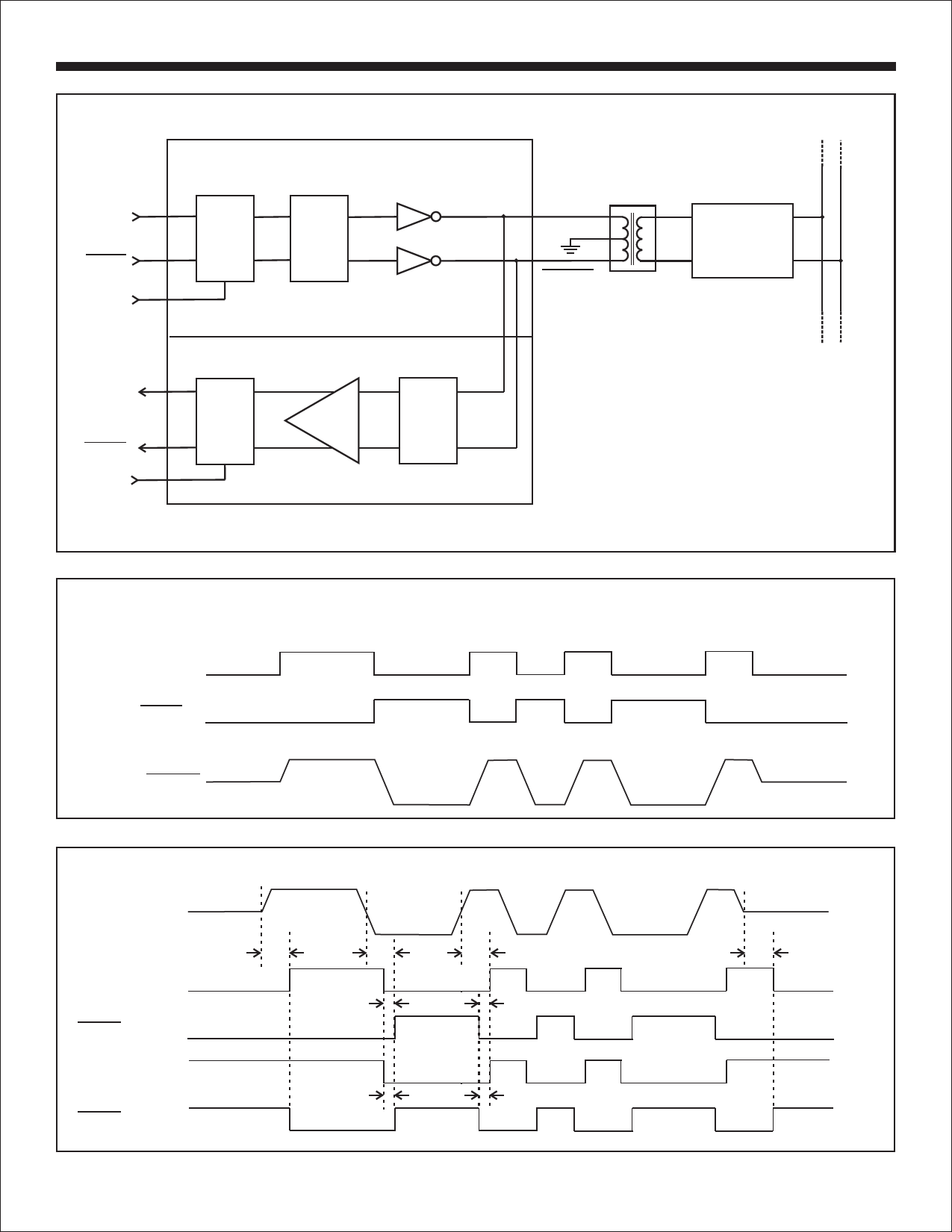

HI-1567, HI-1568

TXA/B

TXA/B

TXINHA/B

RXA/B

RXA/B

RXENA/B

Each Bus

TRANSMITTER

Transmit

Logic

Slope

Control

Data Bus

Isolation

Transformer

BUSA/B

Coupler

Network

Direct or

Transformer

BUSA/B

RECEIVER

Receive

Logic

Comparator

Input

Filter

Figure 1. Block Diagram

TRANSMIT WAVEFORM - EXAMPLE PATTERN

TXA/B

TXA/B

BUSA/B - BUSA/B

RECEIVE WAVEFORMS - EXAMPLE PATTERN

Vin

(Line to Line)

tDR

tDR

tDR

tDR

RXA/B (HI-1567)

RXA/B (HI-1567)

tRG

tRG

RXA/B (HI-1568)

RXA/B (HI-1568)

tRG

tRG

HOLT INTEGRATED CIRCUITS

3