CY7C68053 데이터 시트보기 (PDF) - Cypress Semiconductor

부품명

상세내역

제조사

CY7C68053 Datasheet PDF : 42 Pages

| |||

CY7C68053

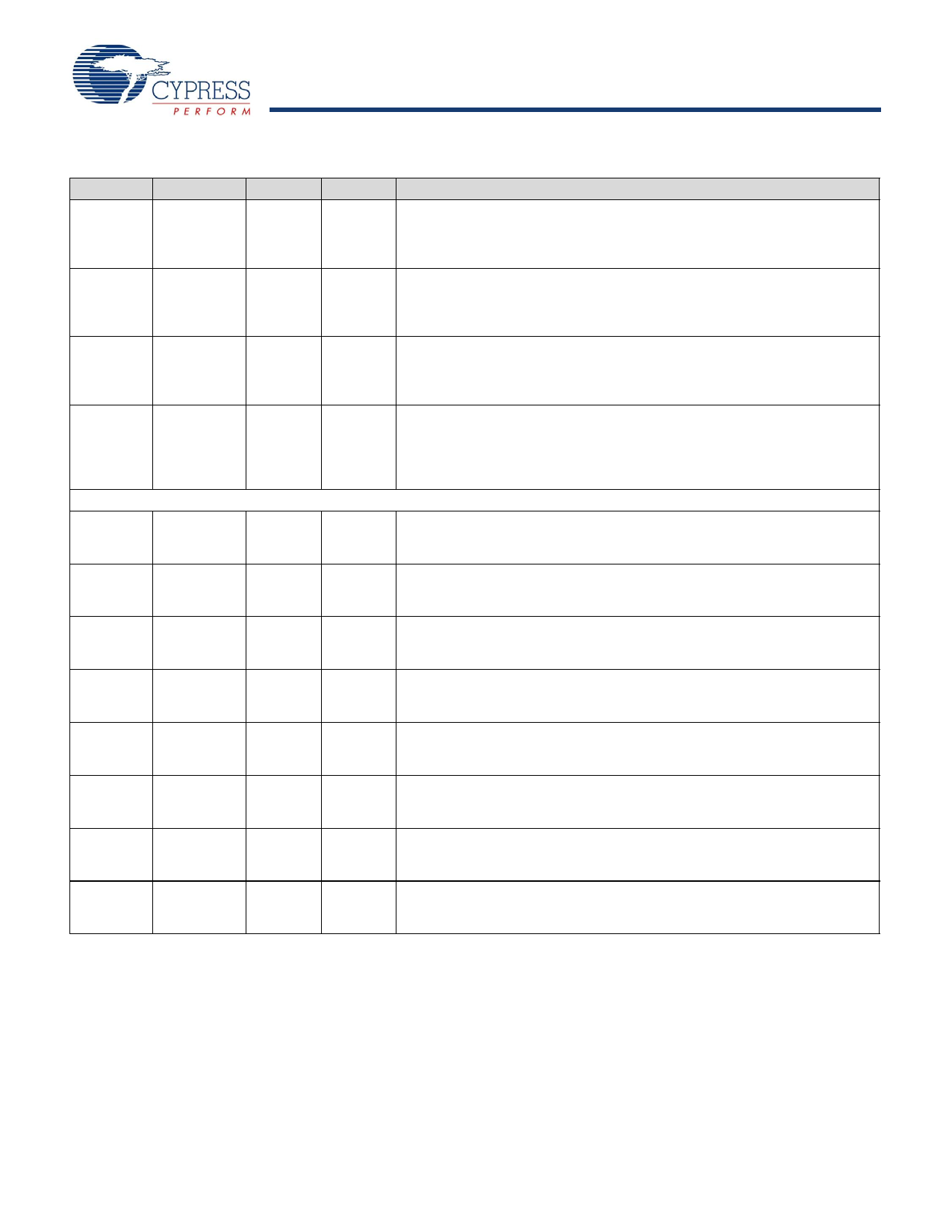

Table 7. FX2LP18 Pin Descriptions (continued)[9]

56 VFBGA Name

6F

PA4 or

FIFOADR0

8C PA5 or

FIFOADR1

7C PA6 or

PKTEND

6C PA7 or

FLAGD or

SLCS#

Port B

3H

4F

4H

4G

5H

5G

5F

6H

PB0 or

FD[0]

PB1 or

FD[1]

PB2 or

FD[2]

PB3 or

FD[3]

PB4 or

FD[4]

PB5 or

FD[5]

PB6 or

FD[6]

PB7 or

FD[7]

Type

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

I/O/Z

Default

I

(PA4)

I

(PA5)

I

(PA6)

I

(PA7)

Description

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PA4 is a bidirectional I/O port pin.

FIFOADR0 is an input-only address select for the slave FIFOs connected to

FD[7:0] or FD[15:0].

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PA5 is a bidirectional I/O port pin.

FIFOADR1 is an input-only address select for the slave FIFOs connected to

FD[7:0] or FD[15:0].

Multiplexed pin whose function is selected by the IFCONFIG[1:0] bits.

PA6 is a bidirectional I/O port pin.

PKTEND is an input that commits the FIFO packet data to the endpoint and

whose polarity is programmable using FIFOPINPOLAR.5.

Multiplexed pin whose function is selected by the IFCONFIG[1:0] and

PORTACFG.7 bits.

PA7 is a bidirectional I/O port pin.

FLAGD is a programmable slave FIFO output status flag signal.

SLCS# gates all other slave FIFO enable/strobes

I

(PB0)

I

(PB1)

I

(PB2)

I

(PB3)

I

(PB4)

I

(PB5)

I

(PB6)

I

(PB7)

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PB0 is a bidirectional I/O port pin.

FD[0] is the bidirectional FIFO/GPIF data bus.

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PB1 is a bidirectional I/O port pin.

FD[1] is the bidirectional FIFO/GPIF data bus.

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PB2 is a bidirectional I/O port pin.

FD[2] is the bidirectional FIFO/GPIF data bus.

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PB3 is a bidirectional I/O port pin.

FD[3] is the bidirectional FIFO/GPIF data bus.

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PB4 is a bidirectional I/O port pin.

FD[4] is the bidirectional FIFO/GPIF data bus.

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PB5 is a bidirectional I/O port pin.

FD[5] is the bidirectional FIFO/GPIF data bus.

Multiplexed pin whose function is selected by IFCONFIG[1:0].

PB6 is a bidirectional I/O port pin.

FD[6] is the bidirectional FIFO/GPIF data bus.

Multiplexed pin whose function is selected IFCONFIG[1:0].

PB7 is a bidirectional I/O port pin.

FD[7] is the bidirectional FIFO/GPIF data bus.

Document # 001-06120 Rev *J

Page 14 of 42

[+] Feedback