74107 데이터 시트보기 (PDF) - STMicroelectronics

부품명

상세내역

제조사

74107 Datasheet PDF : 11 Pages

| |||

M54HC107

M74HC107

DUAL J-K FLIP FLOP WITH CLEAR

. HIGH SPEED

fMAX = 75 MHz (TYP.) AT VCC = 5 V

. LOW POWER DISSIPATION

ICC = 2 µA (MAX.) AT TA = 25 °C

. HIGH NOISE IMMUNITY

VNIH = VNIL = 28 % VCC (MIN.)

. OUTPUT DRIVE CAPABILITY

10 LSTTL LOADS

. SYMMETRICAL OUTPUT IMPEDANCE

IOH = IOL = 4 mA (MIN.)

. BALANCED PROPAGATION DELAYS

tPLH = tPHL

. WIDE OPERATING VOLTAGE RANGE

VCC (OPR) = 2 V TO 6 V

. PIN AND FUNCTION COMPATIBLE WITH

54/74LS107

B1R

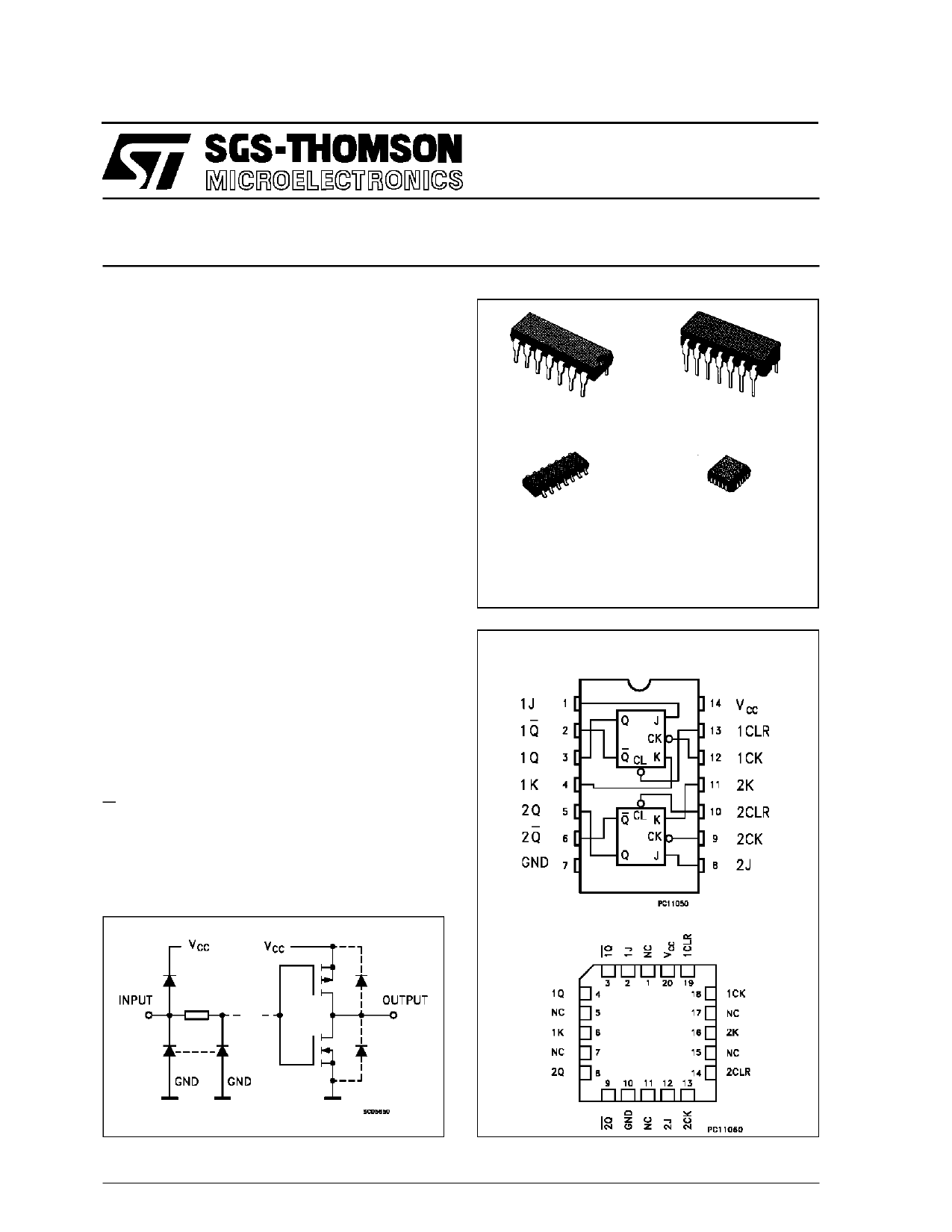

(Plastic Package)

F1R

(Ceramic Package)

M 1R

(Micro Package)

C1R

(Chip Carrier)

ORDER CODES :

M 54HC 10 7F 1R

M 74H C1 07 M1 R

M 74HC 10 7B 1R

M 74H C1 07 C1 R

DESCRIPTION

The M54/74HC107 is a high speed CMOS DUAL J-

K FLIP FLOP fabricated in silicon gate C2MOS tech-

nology. It has the same high speed performance of

LSTTL combined with true CMOS low power con-

sumption. These flip-flop are edge sensitive to the

clock input and change state on the negative going

transition of the clock pulse. Each one has inde-

pendent J, K, CLOCK, and CLEAR input and Q and

Q outputs. CLEAR is independent of the clock and

accomplished by a logic low on the input. All inputs

are equipped with protection circuits against static

discharge and transient excess voltage.

INPUT AND OUTPUT EQUIVALENT CIRCUIT

PIN CONNECTIONS (top view)

October 1992

NC =

No Internal

Connection

1/11