STFLSTUDIO2/KIT 데이터 시트보기 (PDF) - STMicroelectronics

부품명

상세내역

제조사

STFLSTUDIO2/KIT Datasheet PDF : 28 Pages

| |||

W.A.R.P.2.0

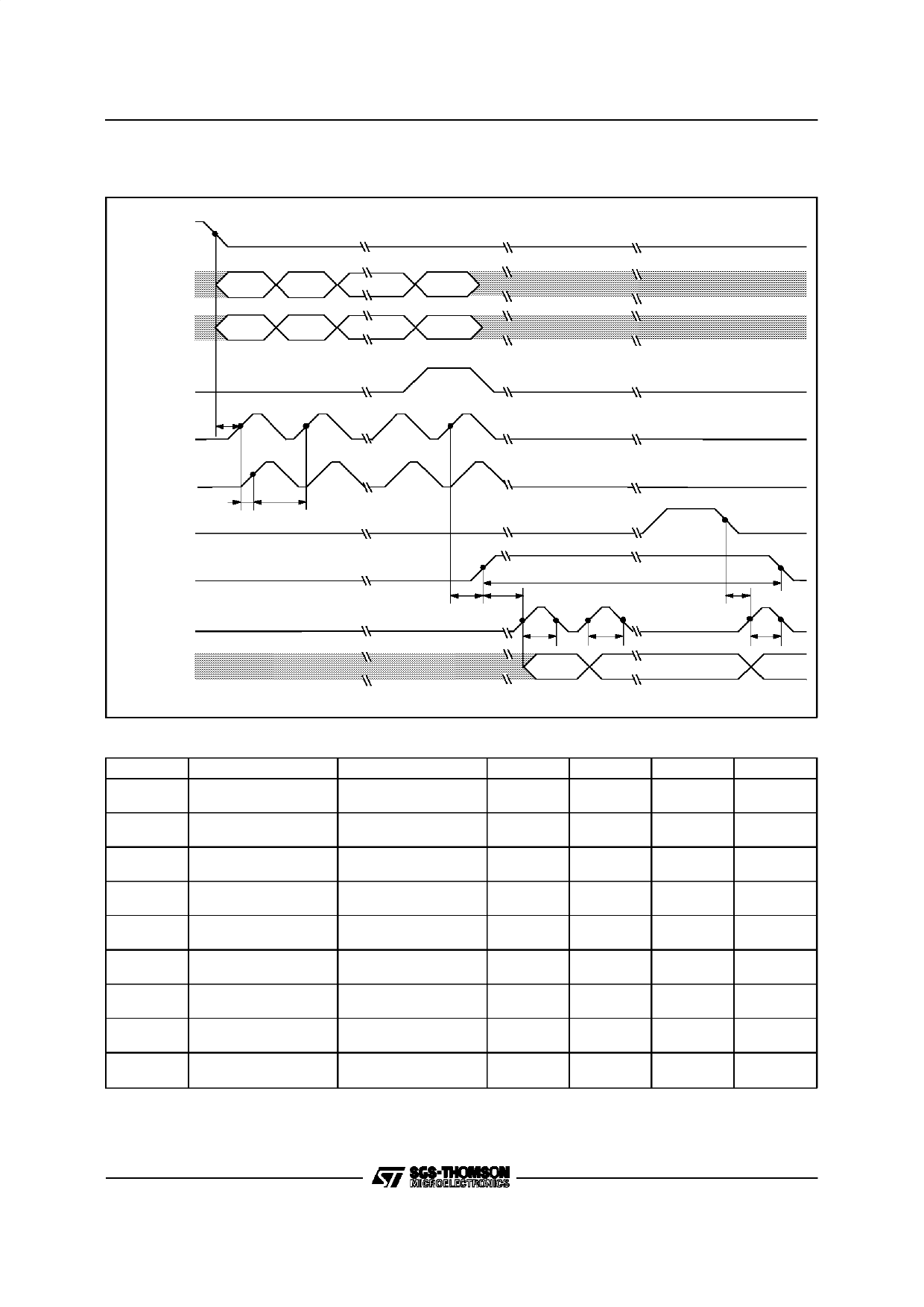

ON-LINE SLAVE PHASE TIMING

OFL

I0-I7

INP 0

INP 1

INP N-1 INP N

SIS0-SIS2 ADDR 0 ADDR 1 ADDR N-1 ADDR N

LASTIN

RD

READY

WAIT

BUSY

DS

O0-O7

T

1

TT

2

3

T

T

4

5

T

8

T

6

T

8

OUT 0 OUT 1

T

7

T

9

OUT N-1 OUT N

Table 12. On-Line Slave Timing Parameters

Symbol

T1

T2

T3

T4

T5(1)

T6

T7

T8

T9

Mode

On-Line

Slave

On-Line

Slave

On-Line

Slave

On-Line

Slave

On-Line

Slave

On-Line

Slave

On-Line

Slave

On-Line

Slave

On-Line

Slave

Parameter

Min

Typ

Max

OFL Low

to first RD High

3

RD High

to READY High

2

READY High

to next RD High

5

Last RD High

to BUSY High

10

BUSY High

to first Output Ready

64

Elaboration

Time

see fig.6

Wait Low

to next Output Valid

32

DS Pulse Width

5

LAST DS Pulse Width

1

Unit

Clock

Pulses

Clock

Pulses

Clock

Pulses

Clock

Pulses

Clock

Pulses

Clock

Pulses

Clock

Pulses

Clock

Pulses

Clock

Pulses

Note 1. T7 depends on the number of rules related to the current output variable. Each output variable needs at least

two rules and each rule requires 32 clock pulses.

20/28