MT4C4M4BX 데이터 시트보기 (PDF) - Micron Technology

부품명

상세내역

제조사

MT4C4M4BX Datasheet PDF : 20 Pages

| |||

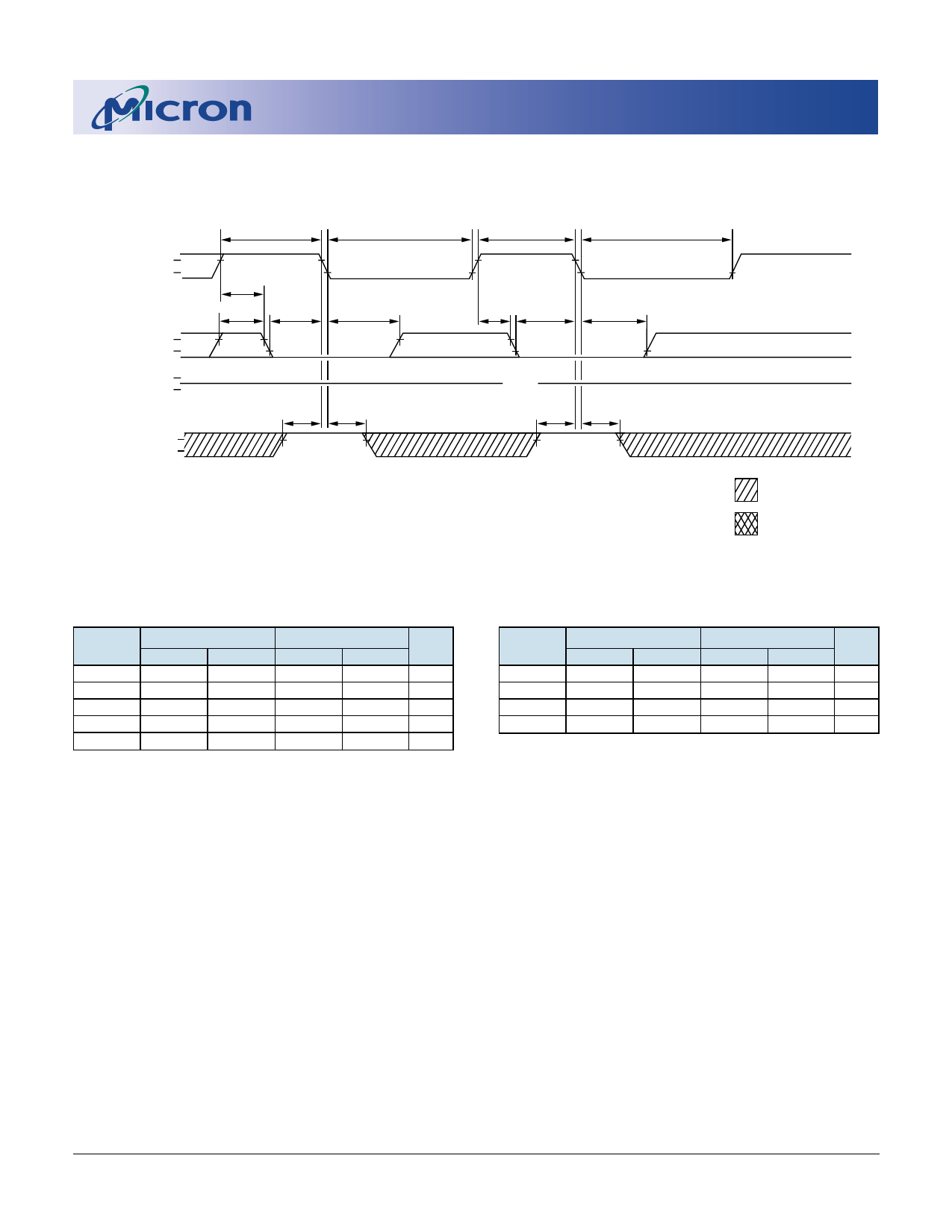

RAS# VVIIHL

CAS# VVIIHL

Q

WE#

V IH

V IL

SELF REFRESH CYCLE

(Addresses and OE# = DON’T CARE)

tRP

tRAS

tRP

tRAS

tRPC

tCP

tCSR

tCHR

tRPC

tCSR

tCHR

tWRP tWRH

OPEN

tWRP tWRH

4 MEG x 4

FPM DRAM

DON’T CARE

UNDEFINED

TIMING PARAMETERS

SYMBOL

tCHD

tCP

tCSR

tRASS

tRP

-5

MIN

MAX

15

8

5

100

30

-6

MIN

MAX

15

10

5

100

40

UNITS

ns

ns

ns

µs

ns

SYMBOL

tRPC

tRPS

tWRH

tWRP

-5

MIN

5

90

8

8

MAX

-6

MIN

MAX

5

105

10

10

UNITS

ns

ns

ns

ns

NOTE: 1. Once tRASS (MIN) is met and RAS# remains LOW, the DRAM will enter self refresh mode.

2. Once tRPS is satisfied, a complete burst of all rows should be executed if RAS#-only or burst CBR refresh is used.

4 Meg x 4 FPM DRAM

D49_5V.p65 – Rev. 5/00

18

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2000, Micron Technology, Inc.