MC14017B 데이터 시트보기 (PDF) - Motorola => Freescale

부품명

상세내역

제조사

MC14017B Datasheet PDF : 7 Pages

| |||

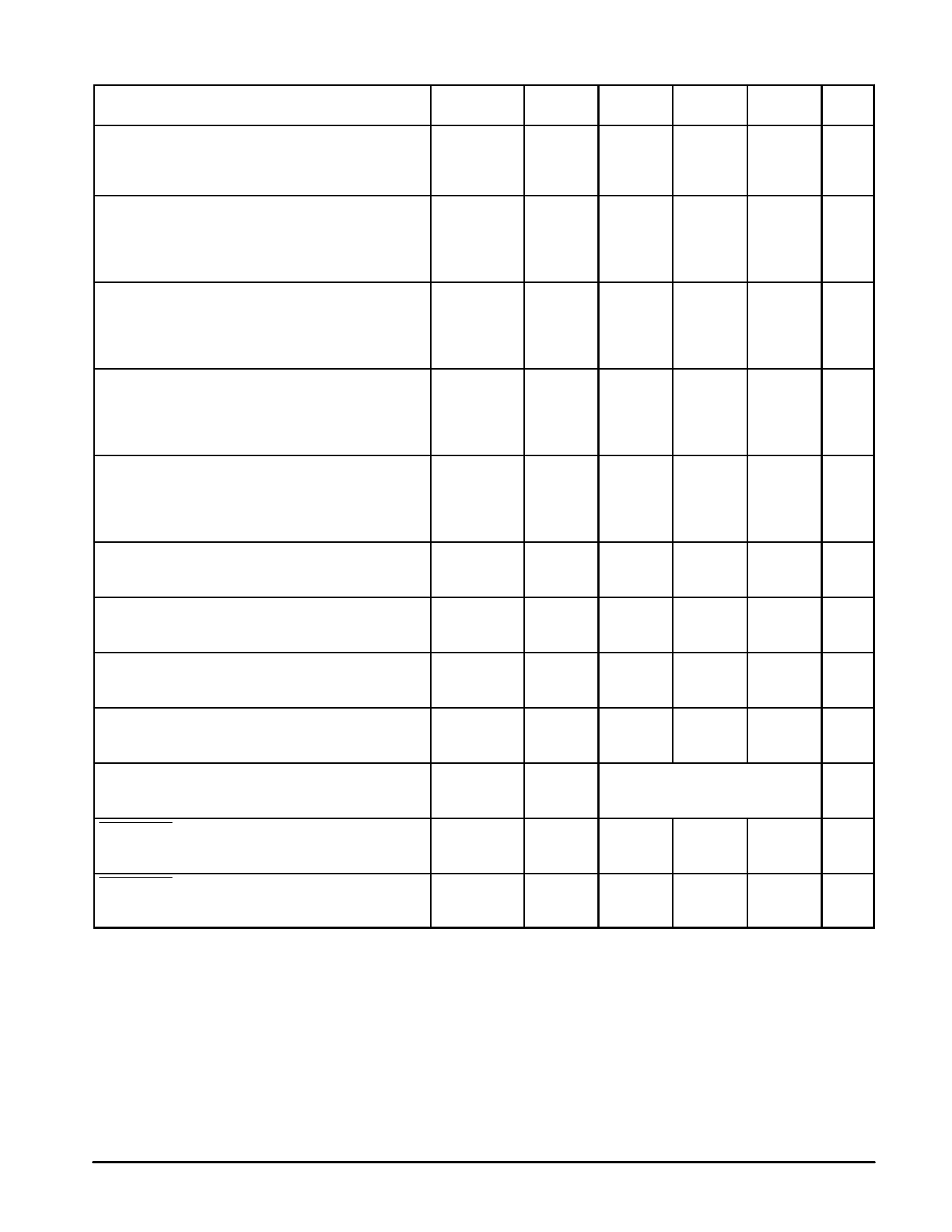

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ SWITCHING CHARACTERISTICS* (CL = 50 pF, TA = 25_C)

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Characteristic

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Output Rise and Fall Time

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tTLH, tTHL = (1.5 ns/pF) CL + 25 ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tTLH, tTHL = (0.75 ns/pF) CL + 12.5 ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tTLH, tTHL = (0.55 ns/pF) CL + 9.5 ns

Propagation Delay Time

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Reset to Decode Output

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tPLH, tPHL = (1.7 ns/pF) CL + 415 ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tPLH, tPHL = (0.66 ns/PF) CL + 197 ns

tPLH, tPHL = (0.5 ns/pF) CL + 150 ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Propagation Delay Time

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Clock to Cout

tPLH, tPHL = (1.7 ns/pF) CL + 315 ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tPLH, tPHL = (0.66 ns/pF) CL + 142 ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tPLH, tPHL = (0.5 ns/pF) CL + 100 ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Propagation Delay Time

Clock to Decode Output

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tPLH, tPHL = (1.7 ns/pF) CL + 415 ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tPLH, tPHL = (0.66 ns/pF) CL + 197 ns

tPLH, tPHL = (0.5 ns/pF) CL + 150 ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Turn–Off Delay Time

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Reset to Cout

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tPLH = (1.7 ns/pF) CL + 315 ns

tPLH = (0.66 ns/pF) CL + 142 ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ tPLH = (0.5 ns/pF) CL + 100 ns

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Clock Pulse Width

Symbol

tTLH,

tTHL

tPLH,

tPHL

tPLH,

tPHL

tPLH,

tPHL

tPLH

tw(H)

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Clock Frequency

fcl

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Reset Pulse Width

tw(H)

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Reset Removal Time

trem

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Clock Input Rise and Fall Time

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Clock Enable Setup Time

tTLH,

tTHL

tsu

ÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎÎ Clock Enable Removal Time

trem

VDD

Vdc

5.0

10

15

5.0

10

15

5.0

10

15

5.0

10

15

5.0

10

15

5.0

10

15

5.0

10

15

5.0

10

15

5.0

10

15

5.0

10

15

5.0

10

15

5.0

10

15

Min

Typ #

Max

Unit

ns

—

100

200

—

50

100

—

40

80

ns

—

500

1000

—

230

460

—

175

350

ns

—

400

800

—

175

350

—

125

250

ns

—

500

1000

—

230

460

—

175

350

ns

—

400

800

—

175

350

—

125

250

250

125

100

50

75

35

—

ns

—

—

—

5.0

2.0

MHz

—

12

5.0

—

16

6.7

500

250

250

125

190

95

—

ns

—

—

750

375

275

135

210

105

—

ns

—

—

—

No Limit

350

175

150

75

115

52

420

260

200

100

140

70

—

ns

—

—

—

ns

—

—

* The formulas given are for the typical characteristics only at 25_C.

#Data labelled “Typ” is not to be used for design purposes but is intended as an indication of the IC’s potential performance.

MC14017B

76

MOTOROLA CMOS LOGIC DATA