MAX539BC 데이터 시트보기 (PDF) - Maxim Integrated

부품명

상세내역

제조사

MAX539BC Datasheet PDF : 16 Pages

| |||

+5V, Low-Power, Voltage-Output,

Serial 12-Bit DACs

SIGNAL

IN

REFIN

CS CLR DIN DOUT REFOUT VDD VSS

2.048V

INVERTED

R-2R DAC

MAX531

VOUT

2R

RFB

2R BIPOFF

POSITIVE OFFSET

4

3

NEGATIVE OFFSET

2

1

0

1 23 4 5 6 7 8

DAC CODE (LSB)

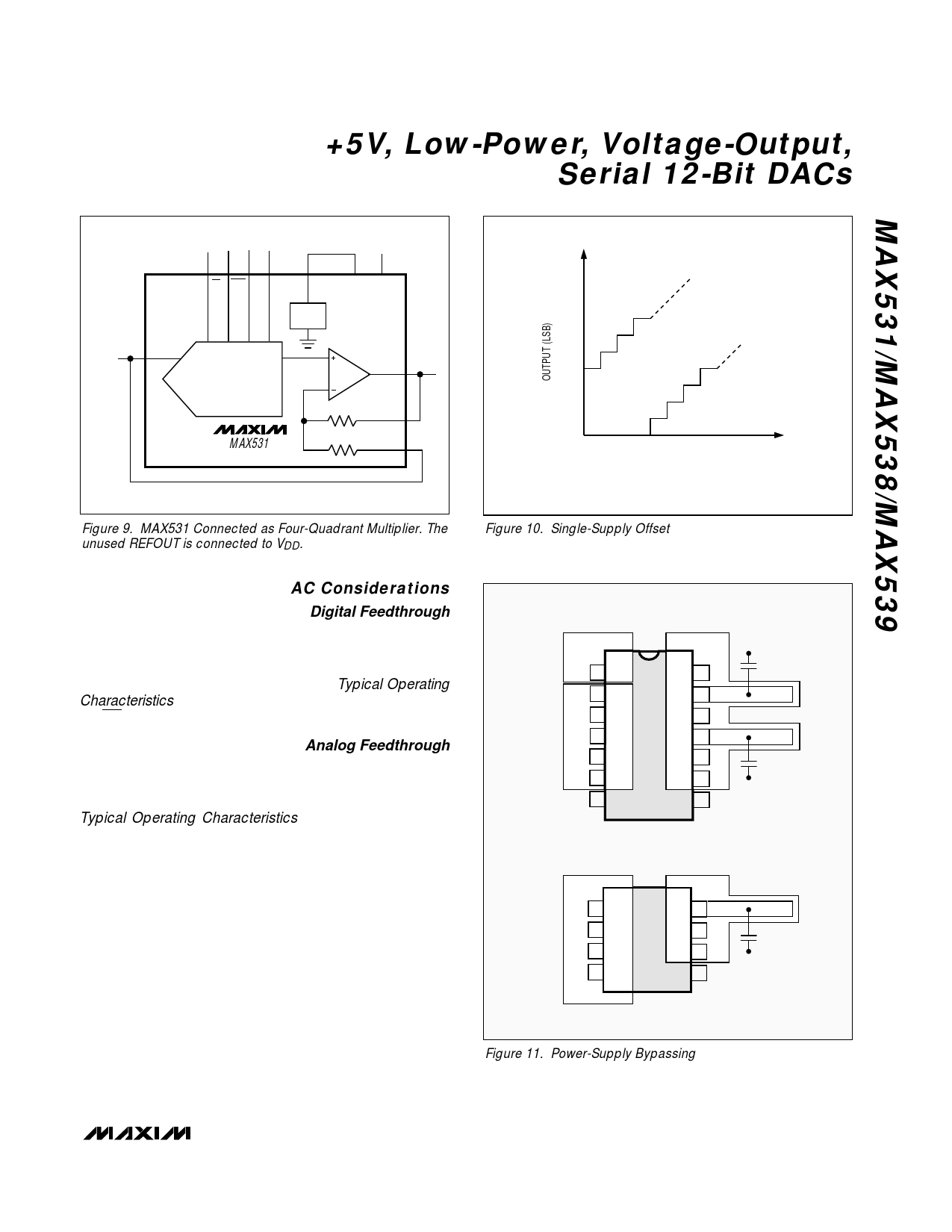

Figure 9. MAX531 Connected as Four-Quadrant Multiplier. The

unused REFOUT is connected to VDD.

Figure 10. Single-Supply Offset

AC Considerations

Digital Feedthrough

High-speed serial data at any of the digital input or output

pins may couple through the DAC package and cause

internal stray capacitance to appear at the DAC output as

noise, even though CS is held high (see Typical Operating

Characteristics). This digital feedthrough is tested by hold-

ing CS high, transmitting 555 hex from DIN to DOUT.

Analog Feedthrough

Because of internal stray capacitance, higher frequency

analog input signals may couple to the output as shown in

the Analog Feedthrough vs. Frequency graph in the

Typical Operating Characteristics. It is tested by holding

CS high, setting the DAC code to all 0s, and sweeping

REFIN.

ANALOG GROUND PLANE

1

14

2

13

3

12

4

11

5

10

6

9

7

8

(a) MAX531 BYPASSING

0.1µF

0.1µF

1

8

2

7

3

6

4

5

0.1µF

(b) MAX538/MAX539 BYPASSING

Figure 11. Power-Supply Bypassing

______________________________________________________________________________________ 13