IDT8535-01 데이터 시트보기 (PDF) - Integrated Device Technology

부품명

상세내역

제조사

IDT8535-01 Datasheet PDF : 11 Pages

| |||

IDT8535-01

LOW SKEW, 1-TO-4 LVCMOS-TO-3.3V LVPECL

CALCULATIONS AND EQUATIONS

VDD

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

Q1

VOUT

RL

50

VDD - 2V

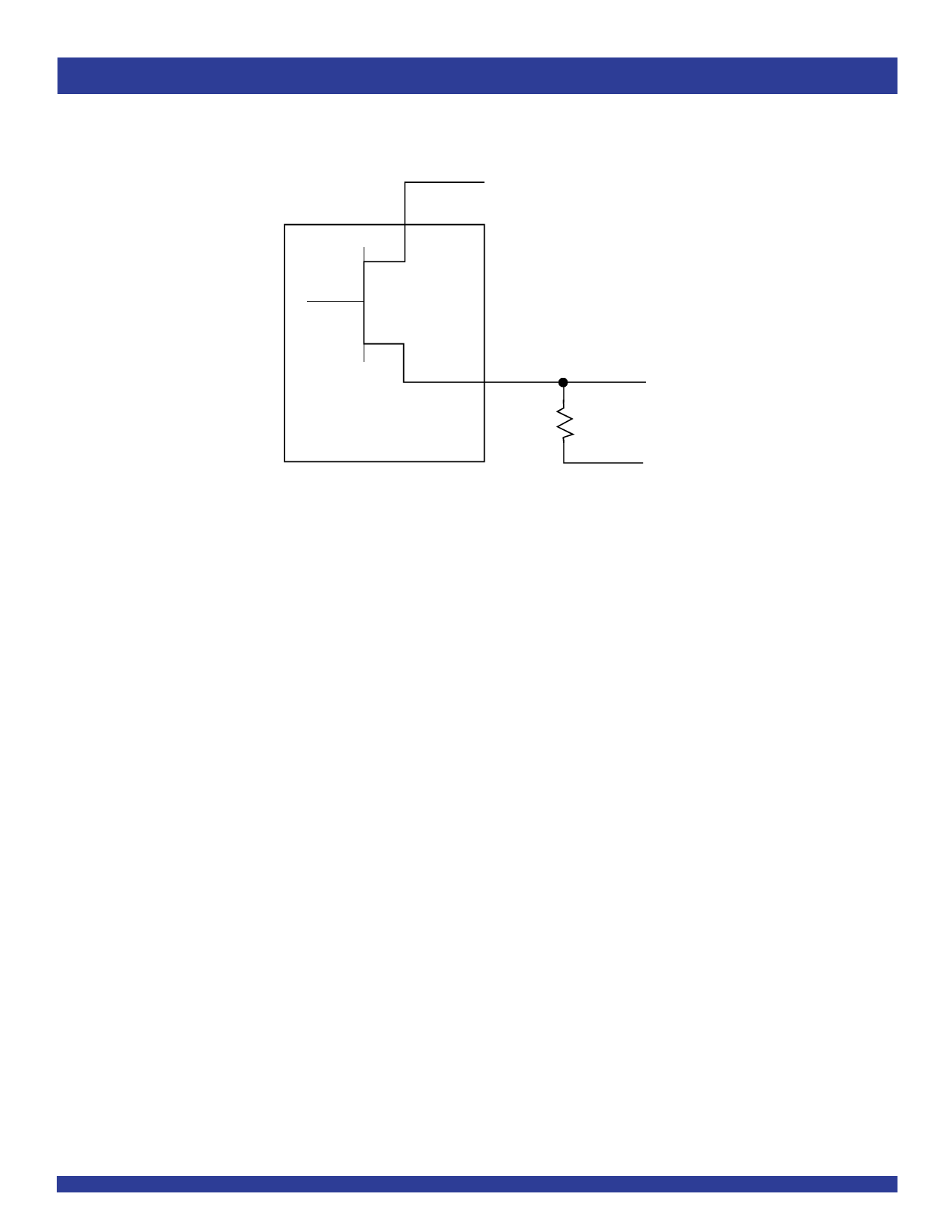

LVPECL Output Driver Circuit and Termination

To calculate worst case power dissipation into the load, use the following equations, which assume a 50Ω load and a termination voltage of VDD – 2V.

For Logic HIGH: VOUT = VOH_MAX = VDD_MAX – 1V.

(VDD_MAX – VOH_MAX) = 1V

For Logic LOW: VOUT = VOL_MAX = VDD_MAX – 1.7V.

(VDD_MAX – VOL_MAX) = 1.7V

Pd_H is power dissipation when the output drives HIGH.

Pd_L is power dissipation when the output drives LOW.

Pd_H = {[ VOH_MAX – (VDD_MAX – 2V)] / RL} * (VDD_MAX – VOH_MAX) = {[ 2V – (VDD_MAX – VOH_MAX)] / RL} * (VDD_MAX – VOH_MAX) = [( 2V – 1V) / 50Ω] *

1V = 20mW.

Pd_L = {[ VOL_MAX – (VDD_MAX – 2V)] / RL} * (VDD_MAX – VOL_MAX) = {[ 2V – (VDD_MAX – VOL_MAX)] / RL} * (VDD_MAX – VOL_MAX) = [( 2V – 1.7V) / 50Ω] *

1.7V = 10.2mW.

Total Power Dissipation per output pair = Pd_H + Pd_L = 30.2mW

10