IDT72205LB15JG(2017) 데이터 시트보기 (PDF) - Integrated Device Technology

부품명

상세내역

제조사

IDT72205LB15JG

(Rev.:2017)

(Rev.:2017)

Integrated Device Technology

IDT72205LB15JG Datasheet PDF : 16 Pages

| |||

IDT72205LB/72215LB/72225LB/72235LB/72245LB CMOS SyncFIFOTM

256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

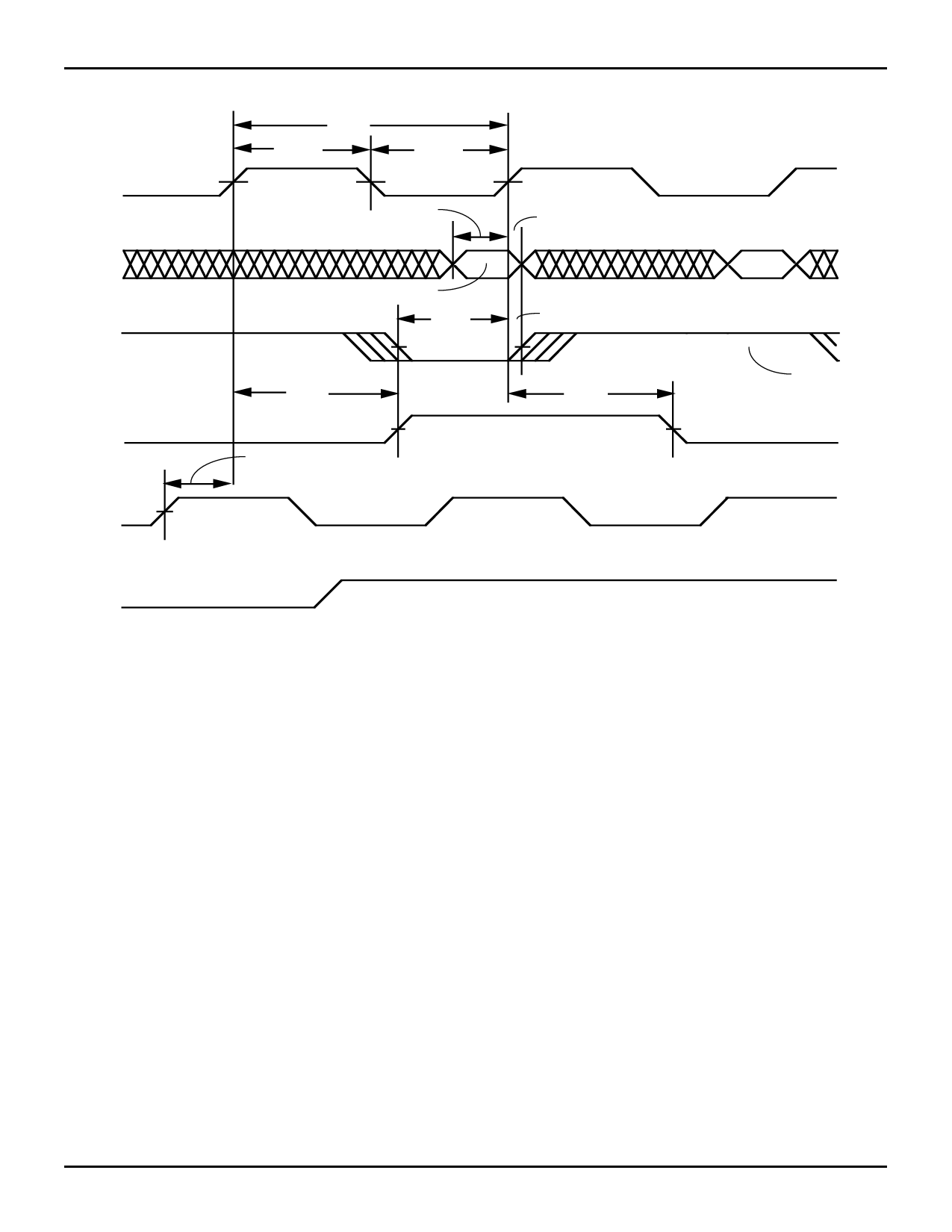

WCLK

t DS

D0 - D17

D0 (first valid write)

D1

D2

t ENS

RCLK

tSKEW2

tFRL(1)

t REF

tENS

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

D3

D4

Q0 - Q17

t OLZ

tA

t OE

tA

D0

D1

NOTES:

2766 drw 09

1. When tSKEW2 minimum specification, tFRL (maximum) = tCLK + tSKEW2. When tSKEW2 < minimum specification, tFRL (maximum) = either 2*tCLK + tSKEW2 or tCLK + tSKEW2.

The Latency Timing applies only at the Empty Boundary (EF = LOW).

2. The first word is available the cycle after EF goes HIGH, always.

Figure 7. First Data Word Latency after Reset with Simultaneous Read and Write

WCLK

D0 - D17

NO WRITE

t SKEW1(1)

t DS

t WFF

DATA WRITE

t WFF

NO WRITE

tSKEW1(1)

t WFF

t DS

DATA

WRITE

RCLK

t ENS

t ENH

t ENS

t ENH

LOW

tA

tA

Q0 - Q17 DATA IN OUTPUT REGISTER

DATA READ

NEXT DATA READ

2766 drw 10

NOTE:

1. tSKEW1 is the minimum time between a rising RCLK edge and a rising WCLK edge to guarantee that FF will go HIGH during the current clock cycle. If the time between the rising

edge of RCLK and the rising edge of WCLK is less than tSKEW1, then FF may not change state until the next WCLK edge.

Figure 8. Full Flag Timing

10

MARCH 2013