ICS810001-21 데이터 시트보기 (PDF) - Integrated Circuit Systems

부품명

상세내역

제조사

ICS810001-21 Datasheet PDF : 21 Pages

| |||

Integrated

Circuit

Systems, Inc.

PRELIMINARY

ICS810001-21

FEMTOCLOCKS™ DUAL VCXO VIDEO PLL

GENERAL DESCRIPTION

The ICS810001-21 is a member of the

ICS

HiperClockS™ family of high performance clock

HiPerClockS™ solutions from ICS. The ICS810001-21 is a PLL

based synchronous clock generator that is

optimized for digital video clock jitter attenuation

and frequency translation. The device contains two internal

frequency multiplication stages that are cascaded in series.

The first stage is a VCXO PLL that is optimized to provide

reference clock jitter attenuation, and to support the complex

PLL multiplication ratios needed for video rate conversion.

The second stage is a FemtoClock frequency multiplier that

provides the low jitter, high frequency video output clock.

Preset multiplication ratios are selected from internal lookup

tables using device input selection pins. The multiplication ra-

tios are optimized to support most common video rates used in

professional video system applications. The VCXO requires

the use of an external, inexpensive pullable crystal. Two crys-

tal connections are provided (pin selectable) so that both 60

and 59.94 base frame rates can be supported. The VCXO re-

quires external passive loop filter components which are used

to set the PLL loop bandwidth and damping characteristics.

FEATURES

• Accepts various HD and SD references including hsync,

transport and pixel clock rates

• Outputs HD and SD pixel rates

• One LVCMOS/LVTTL PLL clock output

• Two selectable LVCMOS/LVTTL input clocks

• LVCMOS input select lines

• VCXO PLL bandwidth can be optimized for jitter attenuation

and reference tracking

• FemtoClock frequency multiplier provides low jitter, high

frequency output

• FemtoClock range: 560MHz - 700MHz

• RMS phase jitter @148.3516484MHz, using a

26.973027MHz crystal (12kHz - 20MHz): 0.81ps (typical)

• 3.3V supply voltage

• 0°C to 70°C ambient operating temperature

OUTPUT RATES SUPPORTED:

Frequency (MHz)

27MHz

26.973027MHz

74.25MHz

74.17582418MHz

148.5MHz

148.3516484MHz

36MHz

Application

MPEG Transport, ITU-R601, CCIR 656

27MHz x 1000/1001

SMPTE 292M/60

SMPTE 292M/59.94

SMPTE 292M/60, 1080P

SMPTE 292M/59.94, 1080P

SMPTE 259M Level “D”

EXAMPLE FREQUENCY CONVERSIONS:

All nine combinations from / to:

27MHz

74.175MHz

74.25MHz

NTSC or PAL hsync to 27MHz

NTSC or PAL hsync to 4xFsc

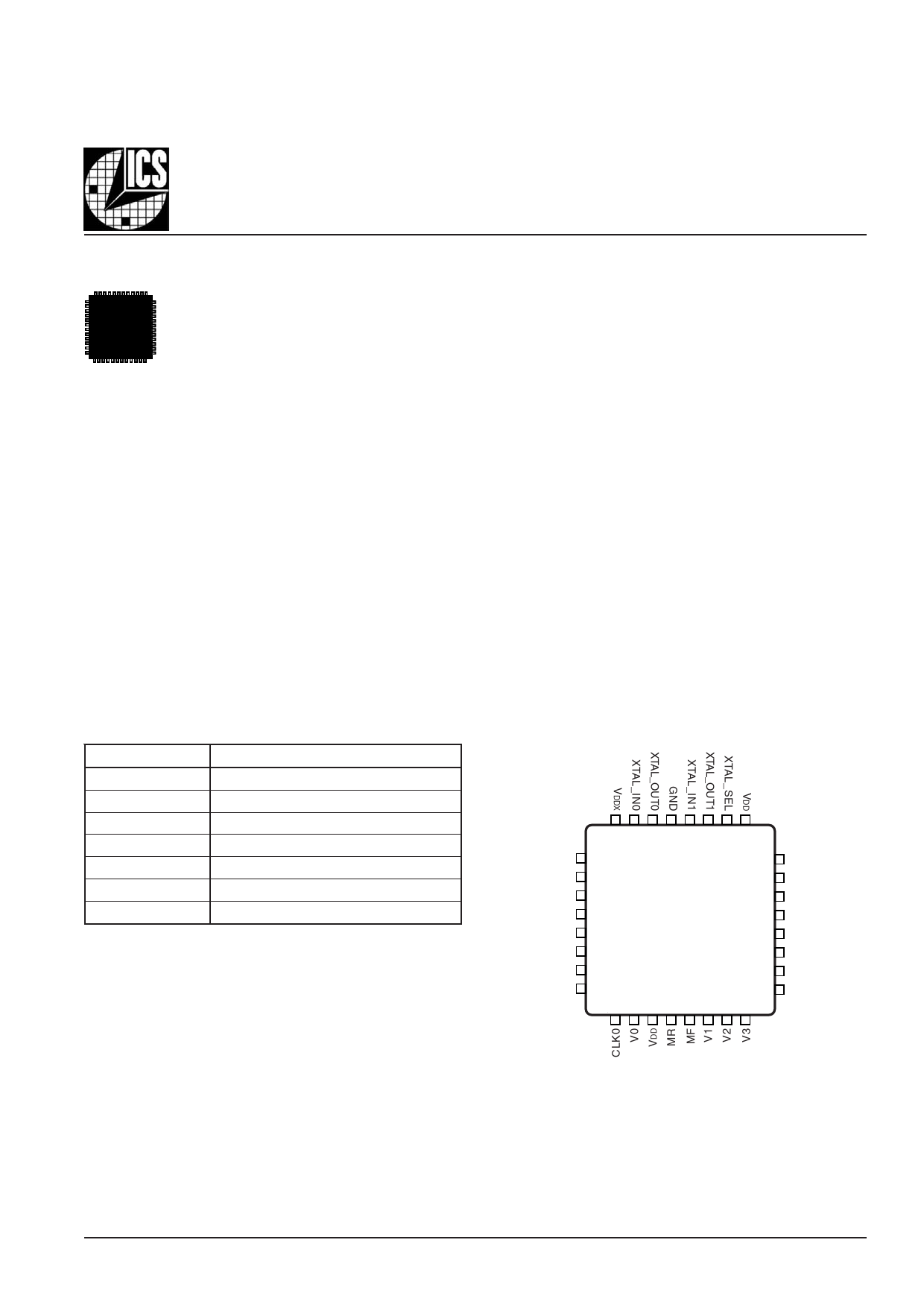

PIN ASSIGNMENT

LF1

LF0

ISET

VDD

nBP0

GND

CLK_SEL

CLK1

32 31 30 29 28 27 26 25

1

24

2

23

3

22

4 ICS810001-21 21

5

20

6

19

7

18

8

17

9 10 11 12 13 14 15 16

N0

N1

nBP1

OE

GND

Q

VDDO

VDDA

32-Lead VFQFN

5mm x 5mm x 0.95 package body

K Package

Top View

The Preliminary Information presented herein represents a product in prototyping or pre-production. The noted characteristics are based on initial

product characterization. Integrated Circuit Systems, Incorporated (ICS) reserves the right to change any circuitry or specifications without notice.

810001BK-21

www.icst.com/products/hiperclocks.html

REV. A AUGUST 12, 2005

1