ICS83940D 데이터 시트보기 (PDF) - Integrated Circuit Systems

부품명

상세내역

제조사

ICS83940D Datasheet PDF : 15 Pages

| |||

Integrated

Circuit

Systems, Inc.

ICS83940D

LOW SKEW, 1-TO-18

LVPECL-TO-LVCMOS / LVTTL FANOUT BUFFER

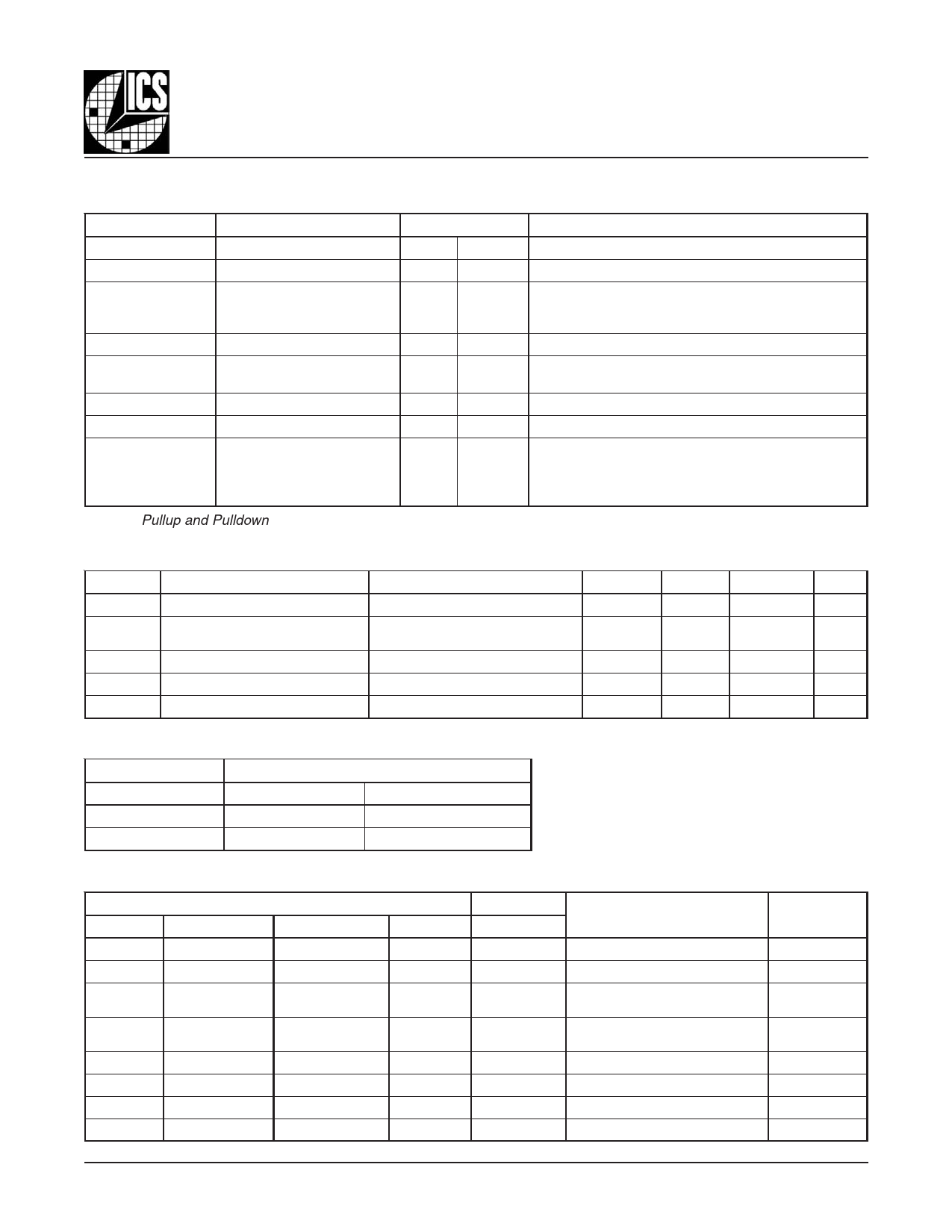

TABLE 1. PIN DESCRIPTIONS

Number

Name

Type

Description

1, 2, 12, 17, 25

GND

Power

Power supply ground.

3

LVCMOS_CLK

Input Pulldown Clock input. LVCMOS / LVTTL interface levels.

Clock select input. Selects LVCMOS / LVTTL clock

4

CLK_SEL

Input Pulldown input when HIGH. Selects PCLK, nPCLK inputs

when LOW. LVCMOS / LVTTL interface levels.

5

PCLK

Input Pulldown Non-inverting differential LVPECL clock input.

6

7, 21

8, 16, 29

9, 10, 11, 13, 14,

15, 18, 19, 20, 22,

23, 24, 26, 27, 28,

30, 31, 32

nPCLK

VDD

VDDO

Q17, Q16, Q15, Q14, Q13,

Q12, Q11, Q10, Q9, Q8,

Q7, Q6, Q5, Q4, Q3,

Q2, Q1, Q0

Input

Power

Power

Output

Pullup/ Inverting differential LVPECL clock input.

Pulldown VDD/2 default when left floating.

Core supply pins.

Output supply pins.

Clock outputs. LVCMOS / LVTTL interface levels.

NOTE: Pullup and Pulldown refers to internal input resistors. See Table 2, Pin Characteristics, for typical values.

TABLE 2. PIN CHARACTERISTICS

Symbol

CIN

CPD

RPULLup

RPULLDOWN

ROUT

Parameter

Input Capacitance

Power Dissipation Capacitance

(per output)

Input Pullup Resistor

Input Pulldown Resistor

Output Impedance

Test Conditions

TABLE 3A. CLOCK SELECT FUNCTION TABLE

Control Input

CLK_SEL

0

1

PCLK, nPCLK

Selected

De-selected

Clock

LVCMOS_CLK

De-selected

Selected

Minimum

18

Typical

4

6

51

51

Maximum

28

Units

pF

pF

KΩ

KΩ

Ω

TABLE 3B. CLOCK INPUT FUNCTION TABLE

Inputs

CLK_SEL LVCMOS_CLK

PCLK

nPCLK

Outputs

Q0:Q17

Input to Output Mode

Polarity

0

—

0

1

LOW

Differential to Single Ended Non Inverting

0

—

1

0

HIGH

Differential to Single Ended Non Inverting

0

—

0

—

0

Biased;

NOTE 1

LOW

Single Ended to Single Ended Non Inverting

1

Biased;

NOTE 1

HIGH

Single Ended to Single Ended Non Inverting

0

—

Biased; NOTE 1

0

HIGH

Single Ended to Single Ended Inverting

0

—

Biased; NOTE 1

1

LOW

Single Ended to Single Ended Inverting

1

0

—

—

LOW

Single Ended to Single Ended Non Inverting

1

1

—

—

HIGH

Single Ended to Single Ended Non Inverting

NOTE 1: Please refer to the Application Information section, "Wiring the Differential Input to Accept Single Ended Levels".

83940DY

www.icst.com/products/hiperclocks.html

REV. B JUNE 15, 2004

2