BD6761FS-E2 데이터 시트보기 (PDF) - ROHM Semiconductor

부품명

상세내역

제조사

BD6761FS-E2 Datasheet PDF : 23 Pages

| |||

BD6761FS,BD6762FV

Technical Note

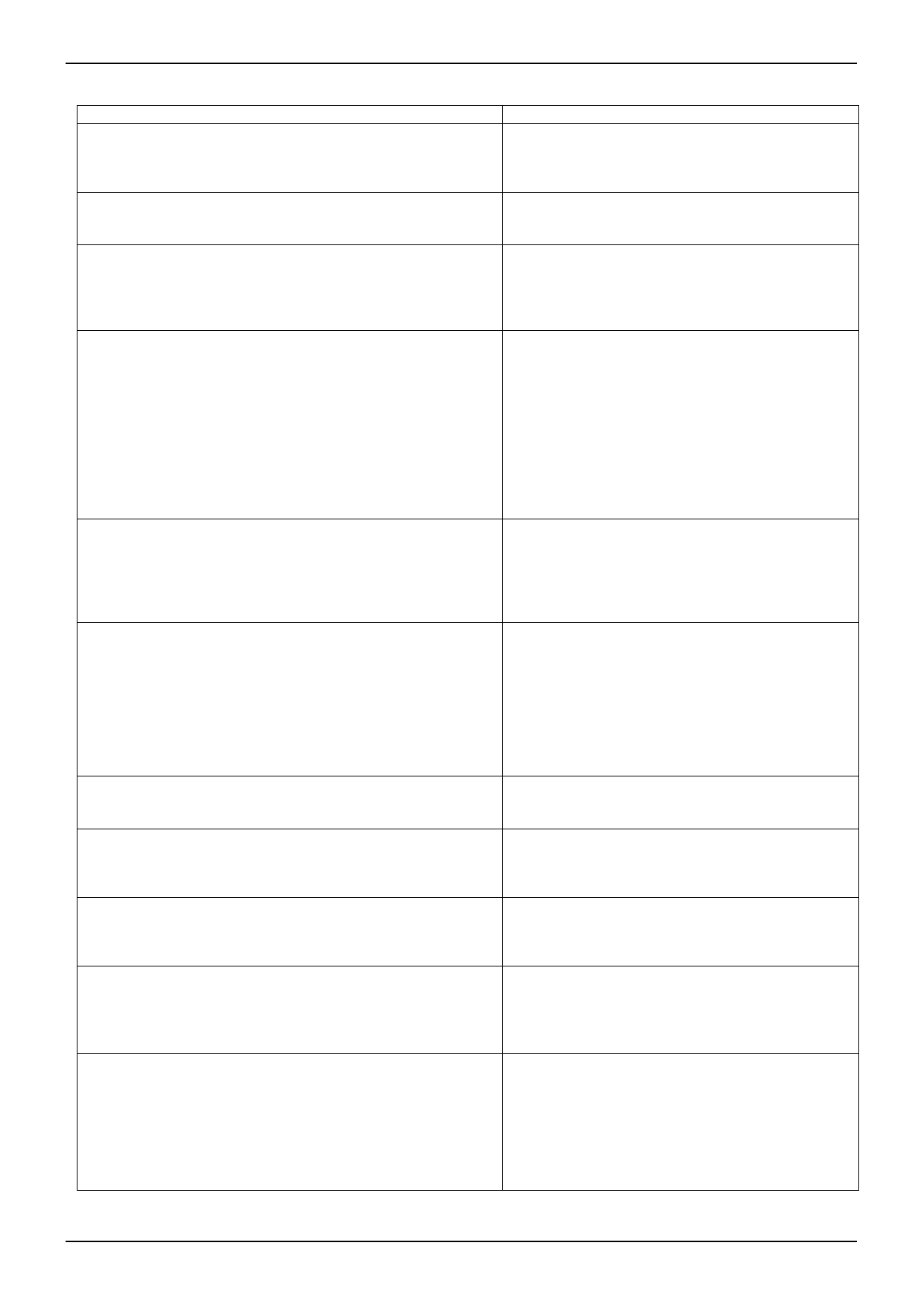

●Selecting application components

Design method

①Output FET

This IC is the predriver for high-side and low-side N-channel

MOS FET drive. Select the FET with the required current

capacity to drive the motor.

②Diodes (BD67861FS)

Diodes are required to protect between the gate and source of

output FET.

③Protection capacitor between the output FET drain and source

Check the operation so that the voltage between the output FET

drain and source does not exceed the absolute maximum

ratings due to the fluctuation of VCC at the time of PWM driving

and then set the value.

④VB current capacitance capacitor

Current capacity from VG changes according to the capacitance

to be connected. However, if the capacitance is too large, the

following action is delayed when VCC starts up, and the

magnitude relation becomes VCC > VG which should be VCC <

VG usually and the large current may flow in internal block

circuits and result in damaging the circuits. When VG is directly

supplied from the external block without using the internal

circuits, disconnect the capacitor between CP1 and CP2, and

connect the 20kΩ resistor (for noise reduction) between CP1

and ground to use.

⑤PWM frequency

PWM frequency can be adjusted by the capacitance and

resistance to connect. When the frequency is high, the heat

generation increases due to switching loss. When the frequency

is low, it enters audible range. Check the operation with the

actual product and determine the constant.

⑥Hall input level

The current value to feed to the hall element changes by

changing the resistance and the amplitude level of hall element

can be adjusted.

Amplitude level increases when the resistance value is chosen

smaller by considering the noise affect, but pay attention also to

the hall input voltage range. BD6761FS (1.5V to 4.1V) and

BD6762FV (0V to 3V)

⑦VREG

VREG which is the internal voltage output pin drives the circuits

in IC. Connect the capacitor to stabilize it.

⑧Current limit

The current flowing to FET can be controlled by setting the

resistance value. Determine the constant according to the motor

specifications.

⑨Hall input noise

Insert capacitors between the hall phases in order to eliminate

the hall input noise due to the effect by the pattern routing

design.

⑩CL (RF) voltage smoothing low pass filter

Smooth the CL (RF) voltage which has PWM noise through the

low pass filter.

⑪FG AMP constant setting

FG AMP gain: GFG is the ratio of R1 and R2 calculated by the

following equation.

GFG=20log R2/R1 [dB]

Set up the gain so that the FGOUT amplitude is large enough to

the hysteresis level of the hysteresis comparator and it cannot

be clamped by the high and low output voltages

(VFGOH and VFGOL).

Design example

Recommended FET RDS035L03 (A)

Recommended diode 1SS355

Insert the diode in the direction from high-side

FET source to the gate side (in the forward direction).

A value of 0.01μ to 0.1μF is recommended.

A value of 0.1μF is appropriate for the capacitance.

Insert the capacitor between the output FET drain and

source. (Position at the close point to FET as much as

possible.)

A value of 0.01μF is appropriate for the capacitor

between CP1 and CP2

(A value of 0.01μF 0.1μF is recommended.)

A value of 0.1μF is appropriate for the capacitor

between VG and VCC.

The following constants are appropriate.

BD6761FS Cfe=1000pF, Rfe=50kΩ, fo=16.5kHz(TYP.)

BD6762FV Cfe=1000pF, Rfe=20kΩ, fo=16.0kHz(TYP.)

Connect to the transistor base via 1k resistor (base

current limit) from the VREG pin. Connect the transistor

collector to VCC, the emitter to the hall element via R1.

Connect the ground side of hall element to the ground

via R2.

A value of 200Ω to 1kΩ is recommended. A value of

200Ω is appropriate, respectively. When connecting to

the VCC side directly with R1, values of R1=5kΩ and

R2=2kΩ are appropriate.

A value of 0.01μF to 0.1μF is recommended. A value of

0.1μ is appropriate.

Following equation shows the current value.

BD6761FS Iomax=0.48/RNF [A]

BD6762FV Iomax=0.26/RNF [A]

A value of 0.01μF is appropriate for the capacitor to be

installed between the hall phases.

A value of 0.01μF to 0.1μF is recommended.

A value of C = 470pF and R=1k is appropriate for the

low pass filter.

For the external constant, since the impedance is high,

make sure to design the pattern with the shortest circuit

route so that the circuit is hard to be affected by noise.

R1 and C1 form a high pass filter and R2 and C2 form a

low pass filter. Each cut off frequency; fMPF and fLPF

is determined by the following equation.

fMPF=1/2πR1C1, fLPF=1/2πR2C2

Set the value so that the main signal from PG by the

motor is not attenuated but the unnecessary noise can

be attenuated.

www.rohm.com

© 2010 ROHM Co., Ltd. All rights reserved.

18/22

2010.06 - Rev.A