ST16C1451CQ48 데이터 시트보기 (PDF) - Exar Corporation

부품명

상세내역

제조사

ST16C1451CQ48 Datasheet PDF : 32 Pages

| |||

áç

REV. 4.2.0

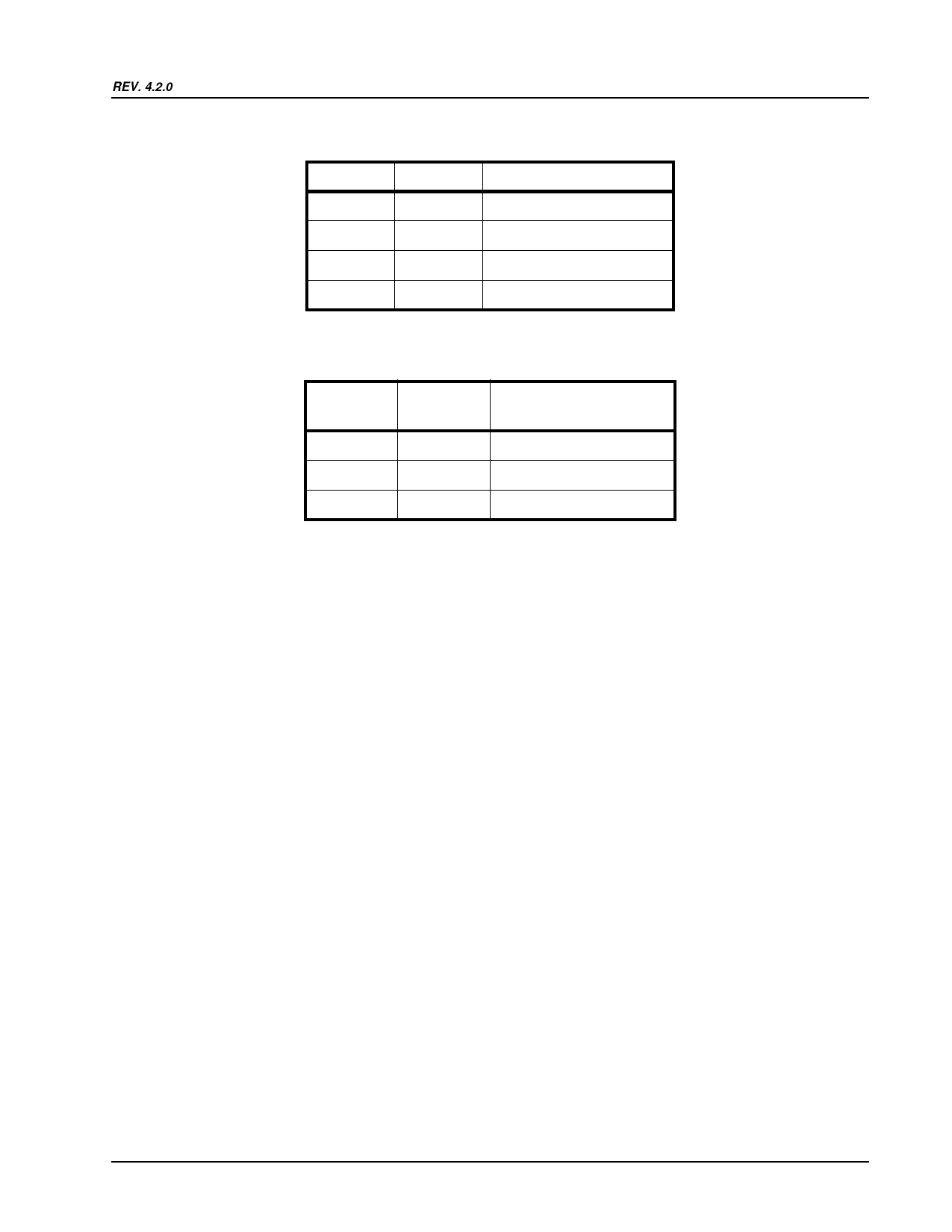

LCR[1:0]: TX and RX Word Length Select

These two bits specify the word length to be transmitted or received.

BIT-1

BIT-0

WORD LENGTH

0

0

5 (default)

0

1

6

1

0

7

1

1

8

ST16C1450/51

2.97V TO 5.5V UART

LCR[2]: TX and RX Stop-bit Length Select

The length of stop bit is specified by this bit in conjunction with the programmed word length.

BIT-2

WORD

LENGTH

STOP BIT LENGTH

(BIT TIME(S))

0

5,6,7,8

1 (default)

1

5

1-1/2

1

6,7,8

2

LCR[3]: TX and RX Parity Select

Parity or no parity can be selected via this bit. The parity bit is a simple way used in communications for data

integrity check. See Table 5 for parity selection summary below.

• Logic 0 = No parity.

• Logic 1 = A parity bit is generated during the transmission while the receiver checks for parity error of the

data character received.

LCR[4]: TX and RX Parity Select

If the parity bit is enabled with LCR bit-3 set to a logic 1, LCR BIT-4 selects the even or odd parity format.

• Logic 0 = ODD Parity is generated by forcing an odd number of logic 1’s in the transmitted character. The

receiver must be programmed to check the same format (default).

• Logic 1 = EVEN Parity is generated by forcing an even number of logic 1’s in the transmitted character. The

receiver must be programmed to check the same format.

17