EP2C5F256I8N 데이터 시트보기 (PDF) - Altera Corporation

부품명

상세내역

제조사

EP2C5F256I8N Datasheet PDF : 470 Pages

| |||

Logic Elements

phase-align double data rate (DDR) signals) provide interface support for

external memory devices such as DDR, DDR2, and single data rate (SDR)

SDRAM, and QDRII SRAM devices at up to 167 MHz.

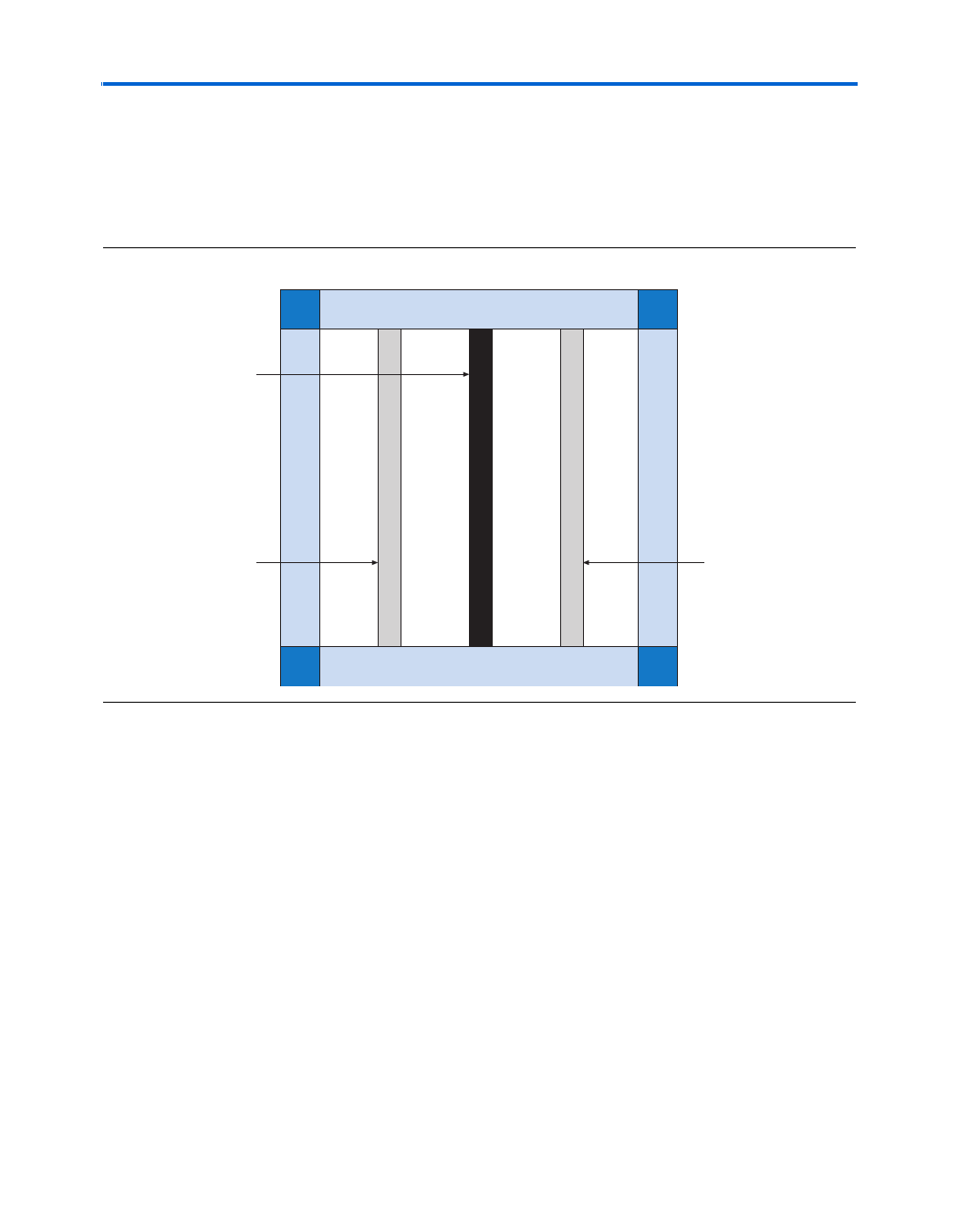

Figure 2–1 shows a diagram of the Cyclone II EP2C20 device.

Figure 2–1. Cyclone II EP2C20 Device Block Diagram

PLL

IOEs

PLL

Embedded

Multipliers

IOEs

Logic

Array

Logic

Array

Logic

Array

Logic

Array

IOEs

M4K Blocks

M4K Blocks

PLL

IOEs

PLL

The number of M4K memory blocks, embedded multiplier blocks, PLLs,

rows, and columns vary per device.

Logic Elements

The smallest unit of logic in the Cyclone II architecture, the LE, is compact

and provides advanced features with efficient logic utilization. Each LE

features:

■ A four-input look-up table (LUT), which is a function generator that

can implement any function of four variables

■ A programmable register

■ A carry chain connection

■ A register chain connection

■ The ability to drive all types of interconnects: local, row, column,

register chain, and direct link interconnects

■ Support for register packing

■ Support for register feedback

2–2

Cyclone II Device Handbook, Volume 1

Altera Corporation

February 2007