Micrel

SY100S351 データシート - Micrel

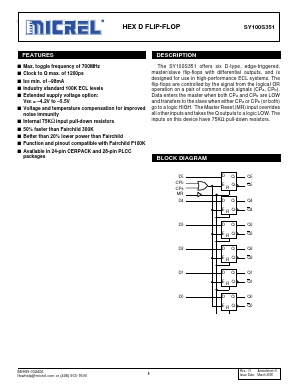

DESCRIPTION

The SY100S351 offers six D-type, edge-triggered, master/slave flip-flops with differential outputs, and is designed for use in high-performance ECL systems. The flip-flops are controlled by the signal from the logical OR operation on a pair of common clock signals (CPa, CPb). Data enters the master when both CPa and CPb are LOW and transfers to the slave when either CPa or CPb (or both) go to a logic HIGH. The Master Reset (MR) input overrides all other inputs and takes the Q outputs to a logic LOW. The inputs on this device have 75KΩ pull-down resistors.

FEATURES

■ Max. toggle frequency of 700MHz

■ Clock to Q max. of 1200ps

■ IEE min. of –98mA

■ Industry standard 100K ECL levels

■ Extended supply voltage option: VEE = –4.2V to –5.5V

■ Voltage and temperature compensation for improved noise immunity

■ Internal 75KΩ input pull-down resistors

■ 50% faster than Fairchild 300K

■ Better than 20% lower power than Fairchild

■ Function and pinout compatible with Fairchild F100K

■ Available in 24-pin CERPACK and 28-pin PLCC packages